- 您现在的位置:买卖IC网 > PDF目录24812 > 935263912557 (NXP SEMICONDUCTORS) 1 CHANNEL(S), 400M bps, SERIAL COMM CONTROLLER, PQFP100 PDF资料下载

参数资料

| 型号: | 935263912557 |

| 厂商: | NXP SEMICONDUCTORS |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 1 CHANNEL(S), 400M bps, SERIAL COMM CONTROLLER, PQFP100 |

| 封装: | 14 X 14 MM, 1 MM HEIGHT, PLASTIC, SOT-386-1, TQFP-100 |

| 文件页数: | 22/56页 |

| 文件大小: | 277K |

| 代理商: | 935263912557 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页当前第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页

Philips Semiconductors

Preliminary specification

PDI1394L21

1394 full duplex AV link layer controller

2000 Jun 06

29

13.1

Link Control Registers

13.1.1

ID Register (IDREG) – Base Address: 0x000

The ID register is automatically updated by the attached PHY with the proper Node ID after completion of the bus reset.

29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

SV00915

NODE ID

BUS ID

VERSION CODE

3130

PART CODE

Reset Value 0xFFFF0101

Bit 31..22:

R/W

BUS ID: The 10-bit bus number that is used with the Node ID in the source address for outgoing packets and used to

accept or reject incoming packets. This field reverts to all ‘1’s (0x3FF) upon bus reset.

Bit 21..16:

R/W

NODE ID: Used in conjunction with Bus ID in the source address for outgoing packets and used to accept or reject

incoming packets. This register auto-updates with the node ID assigned after the 1394 bus Tree-ID sequence.

Bit 15..8:

R

PART CODE: “01” designates PDI1394L21.

Bit 7..0:

R

VERSION CODE: “02” shows this is revision level 2 of this part.

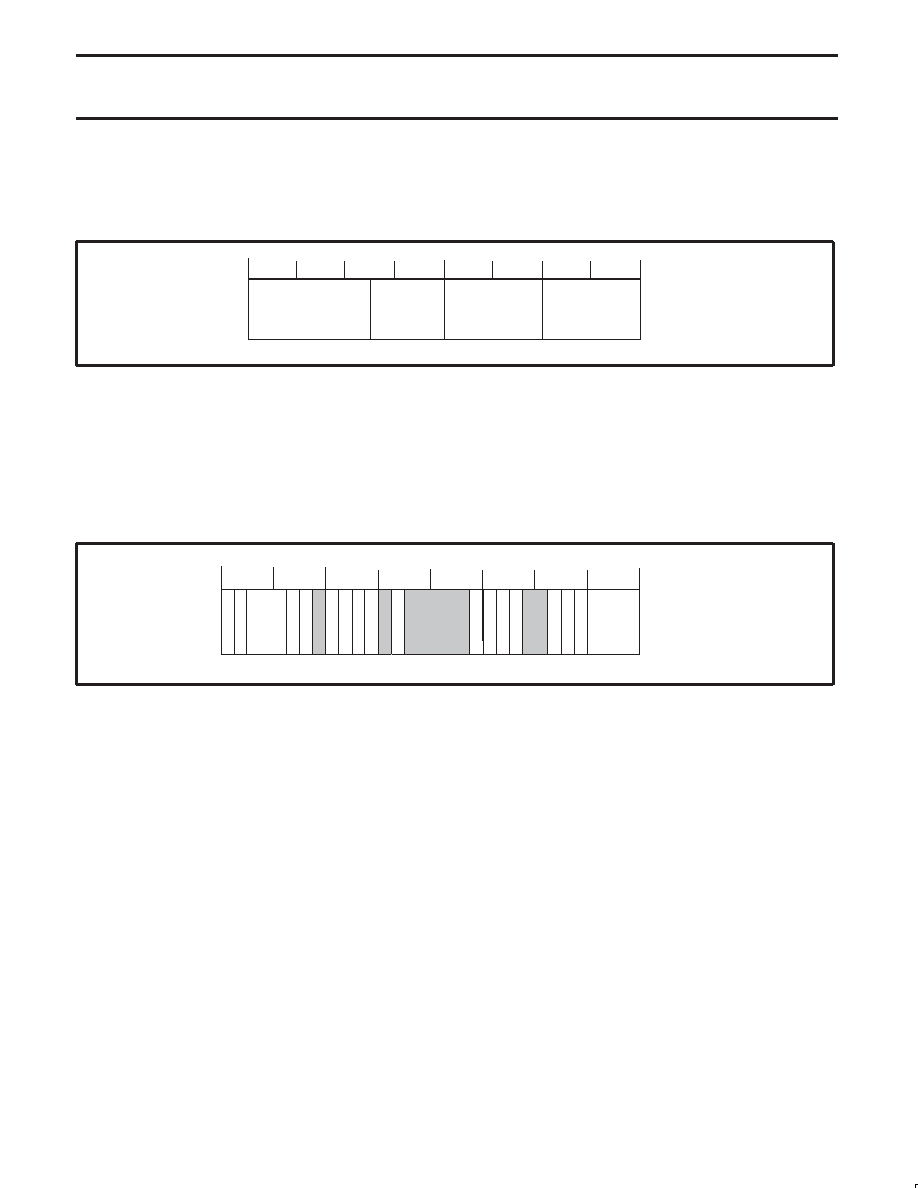

13.1.2

General Link Control (LNKCTL) – Base Address: 0x004

The General Link control register is used to program the Link Layer isochronous transceiver, as well as the overall link transceiver. It also

provides general link status.

29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7

6

5 4 3

2 1

0

SV00892

IDV

ALID

RCVSELFID

ROOT

BUSYFLAG

CYTMREN

STRICTISOCH

CYMASTER

CYSOURCE

RST

Tx

RST

Rx

TxENABLE

RxENABLE

BSYCTRL

ATACK

31 30

TxRDY

RPL

DA

T

AINV

L

TLEND

Reset Value 0x46000002

Bit 31:

R/W

IDValid (IDVALID): When equal to one, the PDI1394L21 accepts the packets addressed to this node. This bit is

automatically set after selfID complete and node ID is updated.

Bit 30:

R/W

Receive Self ID (RCVSELFID): When asserted, the self-identification packets, generated by each PHY device on the

bus, during bus initialization are received and placed into the asynchronous request queue as a single packet. Bit 30

also enables the reception of PHY configuration packets in the asynchronous request queue.

Bit 29..27:

R/W

Busy Control (BSYCTRL): These bits control what busy status the chip returns to incoming packets. The field is

defined below:

000 = use protocol requested by received packet (either dual phase or single phase)

001 = send busy A when it is necessary to send a busy acknowledge (testing/diagnostics)

010 = send a busy B when it is necessary to send a busy acknowledge (testing/diagnostics)

011 = use single phase retry protocol

100 = use protocol requested in packet, always send a busy ack (for all packets)

101 = busy A all incoming packets

110 = busy B all incoming packets are ‘1’

111 = use single phase retry protocol, always send a busy ack

Bit 26:

R/W

Transmitter Enable (TxENABLE): When this bit is set, the link layer transmitter will arbitrate and send packets.

Bit 25:

R/W

Receiver Enable (RxENABLE): When this bit is set, the link layer receiver will receive and respond to bus packets.

Bit 21:

R/W

Reset Transmitter (RSTTx): When set to one, this synchronously resets the transmitter within the link layer.

Bit 20:

R/W

Reset Receiver (RSTRx): When set to one, this synchronously resets the receiver within the link layer.

Bit 12:

R/W

Strict Isochronous (STRICTISOCH): Used to accept or reject isochronous packets sent outside of specified

isochronous cycles (between a Cycle Start and subaction gap). A ‘1’ rejects packets sent outside the specified

cycles, a “0” accepts isochronous packets sent outside the specified cycle.

Bit 11:

R/W

Cycle Master (CYMASTER): When asserted and the PDI1394L21 is attached to the root PHY (ROOT bit = 1), and

the cycle_count field of the cycle timer register increments, the transmitter sends a cycle-start packet. Cycle Master

function will be disabled if a cycle timeout is detected (CYTMOUT bit 5 in LNKPHYINTACK). To restart the Cycle

Master function in such a case, first reset CYMASTER, then set it again.

相关PDF资料 |

PDF描述 |

|---|---|

| 935263912551 | 1 CHANNEL(S), 400M bps, SERIAL COMM CONTROLLER, PQFP100 |

| 08-1101-00 | DREHSCHALTER 1POL 12STELLUNGEN |

| 08-1260-00 | ************GESTRICHEN************ |

| 08-1341-00 | DREHSCHALTER 3POL 4STELLUNGEN |

| 08-2101-00 | DREHSCHALTER 2POL 12STELLUNGEN |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 935264217557 | 制造商:NXP Semiconductors 功能描述:SUB ONLY IC |

| 935267356112 | 制造商:NXP Semiconductors 功能描述:IC TEA1507PN |

| 935268081112 | 制造商:NXP Semiconductors 功能描述:SUB ONLY IC |

| 935268721125 | 制造商:NXP Semiconductors 功能描述:Buffer/Line Driver 1-CH Non-Inverting 3-ST CMOS 5-Pin TSSOP T/R |

| 935269304128 | 制造商:ST-Ericsson 功能描述:IC AUDIO CODEC W/TCH SCRN 48LQFP |

发布紧急采购,3分钟左右您将得到回复。