- 您现在的位置:买卖IC网 > PDF目录24812 > 935263912557 (NXP SEMICONDUCTORS) 1 CHANNEL(S), 400M bps, SERIAL COMM CONTROLLER, PQFP100 PDF资料下载

参数资料

| 型号: | 935263912557 |

| 厂商: | NXP SEMICONDUCTORS |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 1 CHANNEL(S), 400M bps, SERIAL COMM CONTROLLER, PQFP100 |

| 封装: | 14 X 14 MM, 1 MM HEIGHT, PLASTIC, SOT-386-1, TQFP-100 |

| 文件页数: | 31/56页 |

| 文件大小: | 277K |

| 代理商: | 935263912557 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页当前第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页

Philips Semiconductors

Preliminary specification

PDI1394L21

1394 full duplex AV link layer controller

2000 Jun 06

37

13.2.8

Isochronous Receiver Unpacking Control (IRXPKCTL) – Base Address: 0x040

NOTE: When receiver reset is required, first disable receiver (EN_IRX = 0), then wait until Rx FIFO is emptied, then perform the reset. This will

allow previously received packets to go to the application instead of being lost.

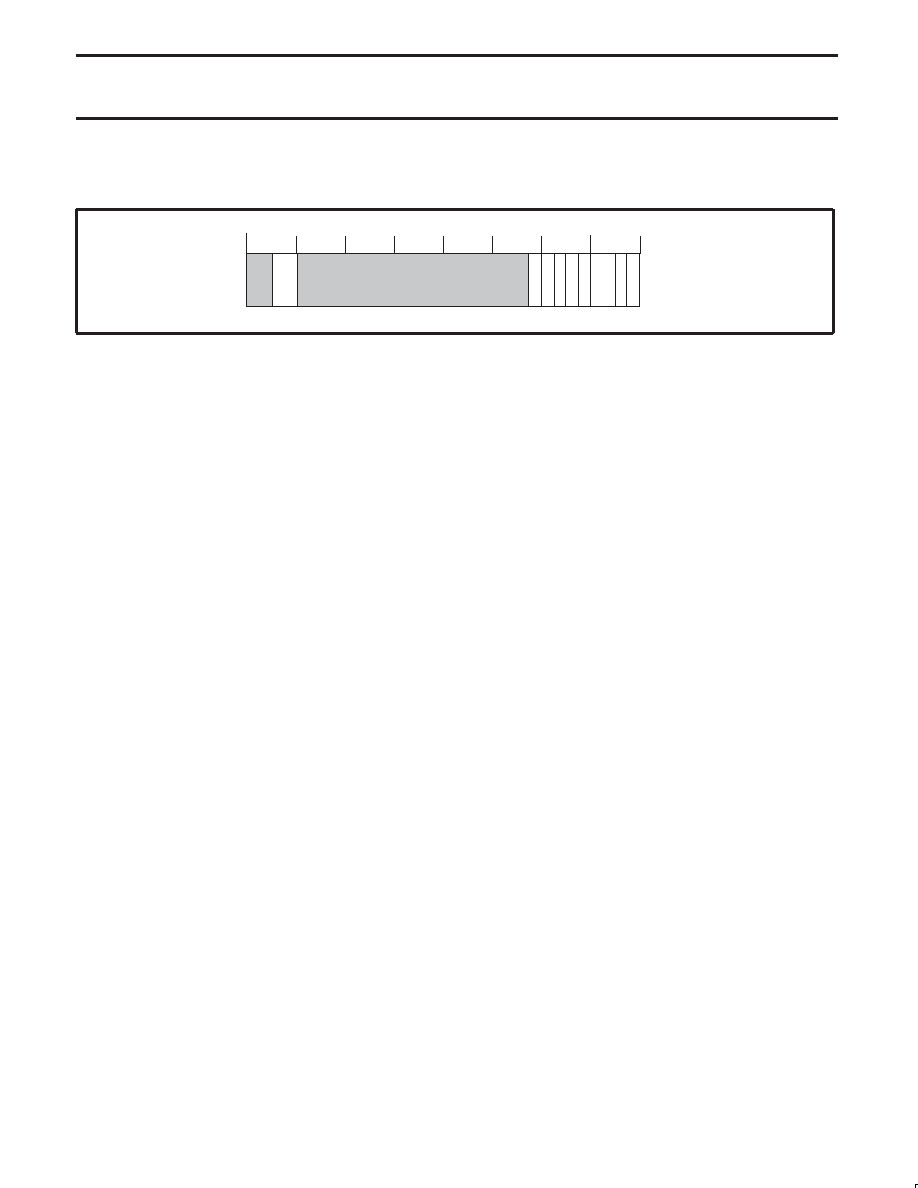

29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

EN_FS

RST_IRX

EN_IRX

SP

A

V

RMVUAP

SV00887

BPAD

31 30

RXAP_CLK

DIS_TSC

SNDIMM

Reset Value 0x00000041

AV Receiver Control Bits.

Bit 29..28:

R/W

RXAP_CLK: Receiver Application Clock, default mode, ‘00’ the AVxCLK pin is an input. This pin can become an

application clock and output for the isochronous Receiver by programming it to ‘01’, ‘10’, or ‘11’.

The programming values are:

00

Input

01

24.576MHz

10

12.288MHz

11

6.144MHz

Note that when enabled as ‘01’, ‘10’, or ‘11’, the AV port that is configured as receiver and enabled will output this

clock signal on its AVxCLK pin.

Bit 8:

R/W

SNDIMM: Send immediately; when set to “1”, this bit will allow a received isochronous packet containing a CRC

error to be output immediately (without regard to the time stamp value). This bit defaults to “0”. In default (reset)

mode, the packet will be output with respect to the time stamp value, even if there is a CRC error.

CAUTION: If there is an error in the time stamp, the packet may be held far into the future. This will affect

subsequently received packets.

Bit 7:

R/W

DIS_TSC: Disable Time Stamp Checking. Defaults to “0”, time stamp checking is enabled. When time stamp

checking is disabled, the time stamp accompanying a packet is output before the packet to the application for use

by the application. This adds an extra quadlet of data to the received data stream; the application must be capable

of handling this extra 4 bytes. Note: The term “Time Stamp” used here refers only to source packet header (full

quadlet) time stamps; it does not mean SYT field hardware synchronization stamps. Also see ENXTMSTP bit in

register X020 for transmit node application time stamp formatting and inputting.

Bit 6:

R/W

RMVUAP: Remove unreliable packets from memory, do not attempt delivery

Bit 5:

R

SPAV: Source packet available for delivery in buffer memory.

Bit 4:

R/W

EN_IRX: Enable receiver operation. Value is only checked whenever a new bus packet arrives, so enable/disable

while running is ‘graceful’, meaning any transfers in process will be completed before this bit is asserted.

Bit 2..3:

R/W

BPAD: Value indicating the amount of byte padding to be removed from the last data quadlet of each source packet,

from 0 to 3 bytes. This is in addition to quadlet padding as defined in IEC 61883 International Standard.

Bit 1:

R/W

EN_FS: Enable processing of SYT stamps.

Bit 0:

R/W

RST_IRX: causes the receiver to be reset when ‘1’. In order for synchronous reset of IRX to work properly, the

application must supply an AVCLK and ensure that the reset bit is kept (programmed) HIGH for at least the duration

of one AVCLK period. Failure to do so may cause the application interface of this module to be improperly reset (or

not reset at all).

相关PDF资料 |

PDF描述 |

|---|---|

| 935263912551 | 1 CHANNEL(S), 400M bps, SERIAL COMM CONTROLLER, PQFP100 |

| 08-1101-00 | DREHSCHALTER 1POL 12STELLUNGEN |

| 08-1260-00 | ************GESTRICHEN************ |

| 08-1341-00 | DREHSCHALTER 3POL 4STELLUNGEN |

| 08-2101-00 | DREHSCHALTER 2POL 12STELLUNGEN |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 935264217557 | 制造商:NXP Semiconductors 功能描述:SUB ONLY IC |

| 935267356112 | 制造商:NXP Semiconductors 功能描述:IC TEA1507PN |

| 935268081112 | 制造商:NXP Semiconductors 功能描述:SUB ONLY IC |

| 935268721125 | 制造商:NXP Semiconductors 功能描述:Buffer/Line Driver 1-CH Non-Inverting 3-ST CMOS 5-Pin TSSOP T/R |

| 935269304128 | 制造商:ST-Ericsson 功能描述:IC AUDIO CODEC W/TCH SCRN 48LQFP |

发布紧急采购,3分钟左右您将得到回复。