- 您现在的位置:买卖IC网 > PDF目录24812 > 935263912557 (NXP SEMICONDUCTORS) 1 CHANNEL(S), 400M bps, SERIAL COMM CONTROLLER, PQFP100 PDF资料下载

参数资料

| 型号: | 935263912557 |

| 厂商: | NXP SEMICONDUCTORS |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 1 CHANNEL(S), 400M bps, SERIAL COMM CONTROLLER, PQFP100 |

| 封装: | 14 X 14 MM, 1 MM HEIGHT, PLASTIC, SOT-386-1, TQFP-100 |

| 文件页数: | 30/56页 |

| 文件大小: | 277K |

| 代理商: | 935263912557 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页当前第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页

Philips Semiconductors

Preliminary specification

PDI1394L21

1394 full duplex AV link layer controller

2000 Jun 06

36

13.2.6

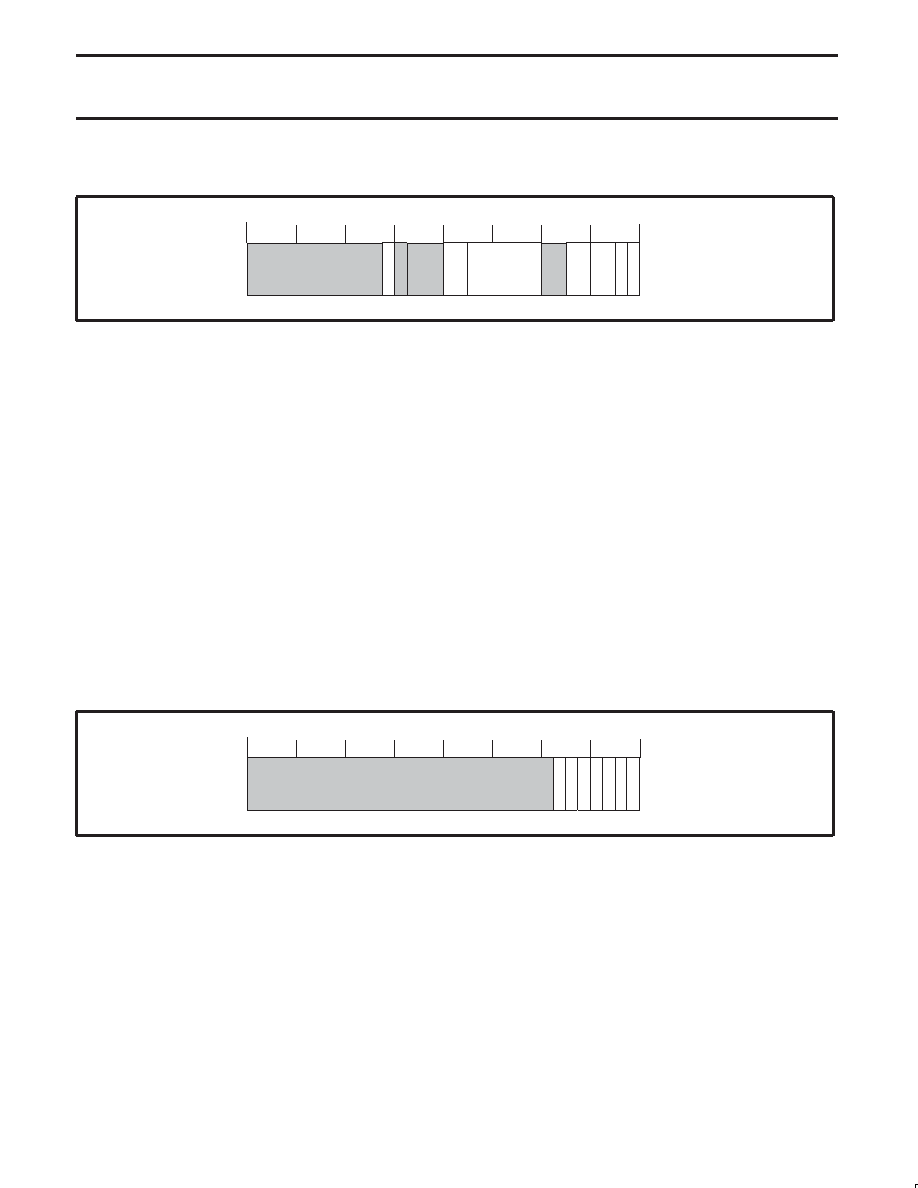

Isochronous Transmitter Control Register (ITXCTL) – Base Address: 0x34

29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

SV01016

TAG

CHANNEL

SPD

31 30

ODD/EVEN

CPHR_EN

SY

EMI

Reset Value 0x00000000

Bit 15..14:

R/W

Tag: Tag code to insert in isochronous bus packet header. Should be ‘01’ for IEC 61883 International Standard data.

Bit 13..8:

R/W

Channel: Isochronous channel number.

Bit 5..4:

R/W

Speed: Cable transmission speed (S100, S200, S400).

00 = 100Mbs

01 = 200Mbs

10 = 400Mbs

11 = reserved

Bit 3..0

R

Sync: Code to insert in SY field of isochronous bus packet header. Bit 1 is odd/even bit used for encryption key

(0 = even, 1 = odd). Bit value determined by state of transmit port AVxENKEY pin. Some data encryption schemes

require that an ODD/EVEN bit accompany each application packet sent for the purpose of changing “keys” after

short intervals of time (makes breaking an encryption code more difficult). The PDI1394L21 uses the sync field

ODD/EVEN bit for this purpose. Data is inputted to the transmitting AV port accompanied by the state of the

ODD/EVEN bit presented to the AVx ENKEY pin. The pin state at the rising edge of the AVCLK as the first byte of

the packet determines the ODD/EVEN “key” state for that packet. The ODD/EVEN key state may change as often as

required, provided that 2 key changes do not appear in the transmit FIFO simultaneously. If this rule is observed, the

proper “key” state will accompany the packet on to the 1394 bus and through the receiving node’s receive FIFO. As

the packet is being outputted at the receive node’s PDI1394L21, the accompanying ODD/EVEN key state will be

output. The key state remains for all bytes of the packet. Typical change rates for the ODD/EVEN key are between

1 change per second and a change every 30 seconds.

13.2.7

Isochronous Transmitter Memory Status (ITXMEM) – Base Address: 0x038

The AV Transmitter Memory Status register reports on the condition of the internal memory buffer used to store incoming AV data streams

before transmission over the 1394 bus.

29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

ITXMAF

ITXM5A

V

ITXME

ITXMF

SV00916

3130

ITM512LFT

ITM256LFT

ITM100LFT

Reset Value 0x00000003

Bit 6:

R

ITM100LFT: Memory has 100 quadlets of space remaining before becoming full.

Bit 5:

R

ITM256LFT: Memory has 256 quadlets of space remaining before becoming full.

Bit 4:

R

IITM512LFT: Memory is 1/2 full.

Bit 3:

R

ITXMF: memory is completely full, no storage available.

Bit 2:

R

ITXMAF: almost full, exactly one quadlet of storage available.

Bit 1:

R

ITXM5AV: at least 5 more quadlets of storage available.

Bit 0:

R

ITXME: memory bank is empty (zero quadlets stored).

相关PDF资料 |

PDF描述 |

|---|---|

| 935263912551 | 1 CHANNEL(S), 400M bps, SERIAL COMM CONTROLLER, PQFP100 |

| 08-1101-00 | DREHSCHALTER 1POL 12STELLUNGEN |

| 08-1260-00 | ************GESTRICHEN************ |

| 08-1341-00 | DREHSCHALTER 3POL 4STELLUNGEN |

| 08-2101-00 | DREHSCHALTER 2POL 12STELLUNGEN |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 935264217557 | 制造商:NXP Semiconductors 功能描述:SUB ONLY IC |

| 935267356112 | 制造商:NXP Semiconductors 功能描述:IC TEA1507PN |

| 935268081112 | 制造商:NXP Semiconductors 功能描述:SUB ONLY IC |

| 935268721125 | 制造商:NXP Semiconductors 功能描述:Buffer/Line Driver 1-CH Non-Inverting 3-ST CMOS 5-Pin TSSOP T/R |

| 935269304128 | 制造商:ST-Ericsson 功能描述:IC AUDIO CODEC W/TCH SCRN 48LQFP |

发布紧急采购,3分钟左右您将得到回复。