- 您现在的位置:买卖IC网 > PDF目录24812 > 935263912557 (NXP SEMICONDUCTORS) 1 CHANNEL(S), 400M bps, SERIAL COMM CONTROLLER, PQFP100 PDF资料下载

参数资料

| 型号: | 935263912557 |

| 厂商: | NXP SEMICONDUCTORS |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 1 CHANNEL(S), 400M bps, SERIAL COMM CONTROLLER, PQFP100 |

| 封装: | 14 X 14 MM, 1 MM HEIGHT, PLASTIC, SOT-386-1, TQFP-100 |

| 文件页数: | 56/56页 |

| 文件大小: | 277K |

| 代理商: | 935263912557 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页当前第56页

Philips Semiconductors

Preliminary specification

PDI1394L21

1394 full duplex AV link layer controller

2000 Jun 06

9

11.1

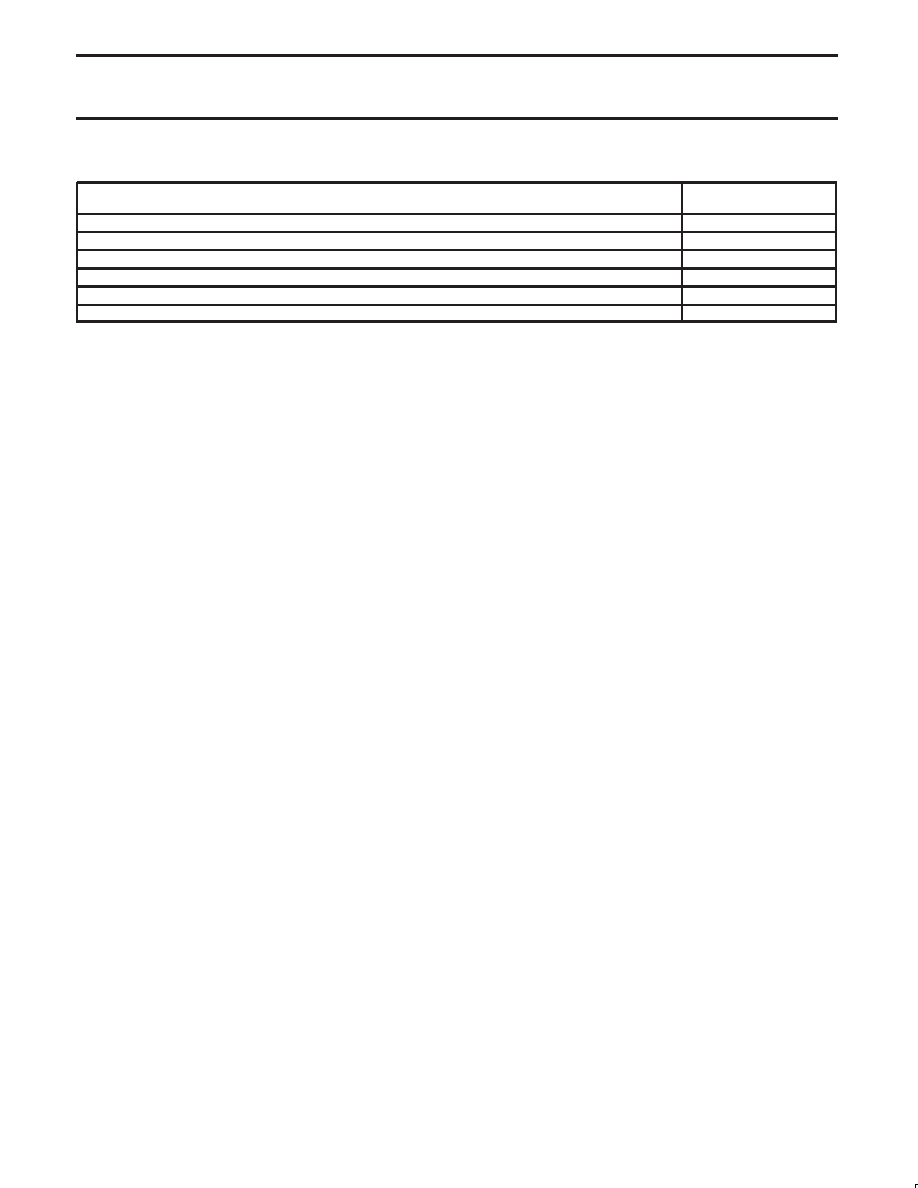

Buffer Memory Sizes

BUFFER MEMORY

SIZE

(Quadlets)

Asynchronous Receive Response FIFO

64

Asynchronous Receive Request FIFO

128

Asynchronous Transmit Response FIFO

64

Asynchronous Transmit Request FIFO

64

Isochronous (AV) Transmit Buffer

1024

Isochronous (AV) Receive Buffer

1024

12.0

FUNCTIONAL DESCRIPTION

12.1

Overview

The PDI1394L21 is an IEEE 1394–1995 compliant link layer controller. It provides a direct interface between a 1394 bus and various MPEG–2

and DVC codecs. Via this interface, the AV Link maps and unmaps these AV datastreams from these codecs onto 1394 isochronous bus

packets. The AV Link also provides an 8051 compatible microcontroller interface for an attached host controller. Through the host interface port,

the host controller can configure the AV layer for transmission or reception of AV datastreams. The host interface port also allows the host

controller to transmit and receive 1394 asynchronous data packets.

12.2

AV interface and AV layer

The AV interface and AV layer allow AV packets to be transmitted from one node to another. The AV transmitter and receiver within the AV layer

perform all the functions required to pack and unpack AV packet data for transfer over a 1394 network. Once the AV layer is properly configured

for operation, no further host controller service should be required. The operation of the AV layer is full-duplex, i.e., the AV layer can receive and

transmit AV packets at the same time.

12.2.1

The AV Interface

The AV Link provides an 8 bit data path to the AV layer. The 8 bit data path is designed with associated clock and control signals to be

compatible with various MPEG–2 and DVC codecs.

The AV interface port buffer, if so programmed, can time stamp incoming AV packets. The AV packet data is stored in the embedded memory

buffer, along with its time stamp information. After the AV packet has been written into the AV layer, the AV layer creates an isochronous bus

packet with the appropriate CIP header. The bus packet along with the CIP header is transferred over the appropriate isochronous

channel/packet. The size and configuration of isochronous data packet payload transmitted is determined by the AV layer’s configuration

registers accessible through the host interface.

The AV interface port waits for the assertion for AVxVALID and AVxSYNC. Note: Do not assert AVxSYNC without AVxVALID. AVxSYNC is

aligned with the rising edge of AVxCLK and the first byte of data on AVxDATA[7:0]. The duration of AVxSYNC is one AVxCLK cycle. AVxSYNC

signals the AV layer that the transfer of an AV packet has begun. At the time the AVxSYNC is asserted, the AV layer creates a new time stamp

in the buffer memory. (This only happens if so configured. The DVC format does not use these time stamps). The time stamp is then transmitted

as part of the source packet header. This allows the AV receiver to provide the AV packet for output at the appropriate time. Only one AVSYNC

pulse is allowed per application packet; if additional sync pulses are presented before the full packet is inputted, a new packet will be started

and the previously inputted packet data will be discarded (and not transmitted) in conjunction with the input error interrupt bit (INPERR, bit 3 of

register 0x02C) being set to flag the error.

When the DV video is enabled (via the format code of the CIP header), the frame synchronization signal AVxFSYNC is time stamped and

placed in the SYT field. The default timestamp value is 3 cycle times (duration of 125

ms each) in the future and is transmitted in the SYT field of

the current CIP header; this value is programmable from 2 to 4 cycle times (see section 13.2.1). On the receiver side, when the SYT stamp

matches the cycle timer register, a pulse is generated on the AVxFSYNC output. The timing for AVxFSYNC is independent of AVxCLK.

12.2.2

IEC 61883 International Standard

The PDI1394L21 is specifically designed to support the IEC61883 International Standard of Digital Interface for Consumer Electronic

Audio/Video Equipment. The IEC specification defines a scheme for mapping various types of AV datastreams onto 1394 isochronous data

packets. The standard also defines a software protocol for managing isochronous connections in a 1394 bus called Connection Management

Protocol (CMP). It also provides a framework for transfer of functional commands, called Function Control Protocol (FCP).

12.2.3

CIP Headers

A feature of the IEC61883 International Standard is the definition of Common Isochronous Packet (CIP) headers. These CIP headers contain

information about the source and type of datastream mapped onto the isochronous packets.

The AV Layer supports the use of CIP headers. CIP headers are added to transmitted isochronous data packets at the AV data source. When

receiving isochronous data packets, the AV layer automatically analyzes their CIP headers. The analysis of the CIP headers determines the

method the AV layer uses to unpack the AV data from the isochronous data packets.

The information contained in the CIP headers is accessible via registers in the host interface.

(See IEC61883 International Standard of Digital Interface for Consumer Electronic Audio/Video Equipment for more details on CIP headers).

相关PDF资料 |

PDF描述 |

|---|---|

| 935263912551 | 1 CHANNEL(S), 400M bps, SERIAL COMM CONTROLLER, PQFP100 |

| 08-1101-00 | DREHSCHALTER 1POL 12STELLUNGEN |

| 08-1260-00 | ************GESTRICHEN************ |

| 08-1341-00 | DREHSCHALTER 3POL 4STELLUNGEN |

| 08-2101-00 | DREHSCHALTER 2POL 12STELLUNGEN |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 935264217557 | 制造商:NXP Semiconductors 功能描述:SUB ONLY IC |

| 935267356112 | 制造商:NXP Semiconductors 功能描述:IC TEA1507PN |

| 935268081112 | 制造商:NXP Semiconductors 功能描述:SUB ONLY IC |

| 935268721125 | 制造商:NXP Semiconductors 功能描述:Buffer/Line Driver 1-CH Non-Inverting 3-ST CMOS 5-Pin TSSOP T/R |

| 935269304128 | 制造商:ST-Ericsson 功能描述:IC AUDIO CODEC W/TCH SCRN 48LQFP |

发布紧急采购,3分钟左右您将得到回复。