- 您现在的位置:买卖IC网 > PDF目录9158 > AD9517-3ABCPZ (Analog Devices Inc)IC CLOCK GEN 2.0GHZ VCO 48LFCSP PDF资料下载

参数资料

| 型号: | AD9517-3ABCPZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 39/80页 |

| 文件大小: | 0K |

| 描述: | IC CLOCK GEN 2.0GHZ VCO 48LFCSP |

| 标准包装: | 1 |

| 类型: | 时钟发生器,扇出配送 |

| PLL: | 是 |

| 输入: | CMOS,LVDS,LVPECL |

| 输出: | CMOS,LVDS,LVPECL |

| 电路数: | 1 |

| 比率 - 输入:输出: | 1:12 |

| 差分 - 输入:输出: | 是/是 |

| 频率 - 最大: | 2.25GHz |

| 除法器/乘法器: | 是/无 |

| 电源电压: | 3.135 V ~ 3.465 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 48-VFQFN 裸露焊盘,CSP |

| 供应商设备封装: | 48-LFCSP-VQ(7x7) |

| 包装: | 托盘 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页当前第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页

AD9517-3

Data Sheet

Rev. E | Page 44 of 80

Phase Offset or Coarse Time Delay (0, 1)

Each channel divider allows for a phase offset, or a coarse time

delay, to be programmed by setting register bits (see Table 38).

These settings determine the number of cycles (successive

rising edges) of the channel divider input frequency by which to

offset, or delay, the rising edge of the output of the divider. This

delay is with respect to a nondelayed output (that is, with a

phase offset of zero). The amount of the delay is set by five bits

loaded into the phase offset (PO) register plus the start high (SH)

bit for each channel divider. When the start high bit is set, the

delay is also affected by the number of low cycles (M) that are

programmed for the divider.

The sync function must be used to make phase offsets effective

(see the Synchronizing the Outputs—Sync Function section).

Table 38. Setting Phase Offset and Division for Divider 0 and

Divider 1

Divider

Start

High (SH)

Phase

Offset (PO)

Low Cycles

M

High Cycles

N

0

0x191[4]

0x191[3:0]

0x190[7:4]

0x190[3:0]

1

0x197[4]

0x197[3:0]

0x196[7:4]

0x196[3:0]

Let

Δt = delay (in seconds).

Δc = delay (in cycles of clock signal at input to DX).

TX = period of the clock signal at the input of the divider, DX

(in seconds).

Φ = 16 × SH[4] + 8 × PO[3] + 4 × PO[2] + 2 × PO[1] + 1 × PO[0]

The channel divide-by is set as N = high cycles and M = low cycles.

Case 1

For Φ ≤ 15:

Δt = Φ × TX

Δc = Δt/TX = Φ

Case 2

For Φ ≥ 16:

Δt = (Φ 16 + M + 1) × TX

Δc = Δt/TX

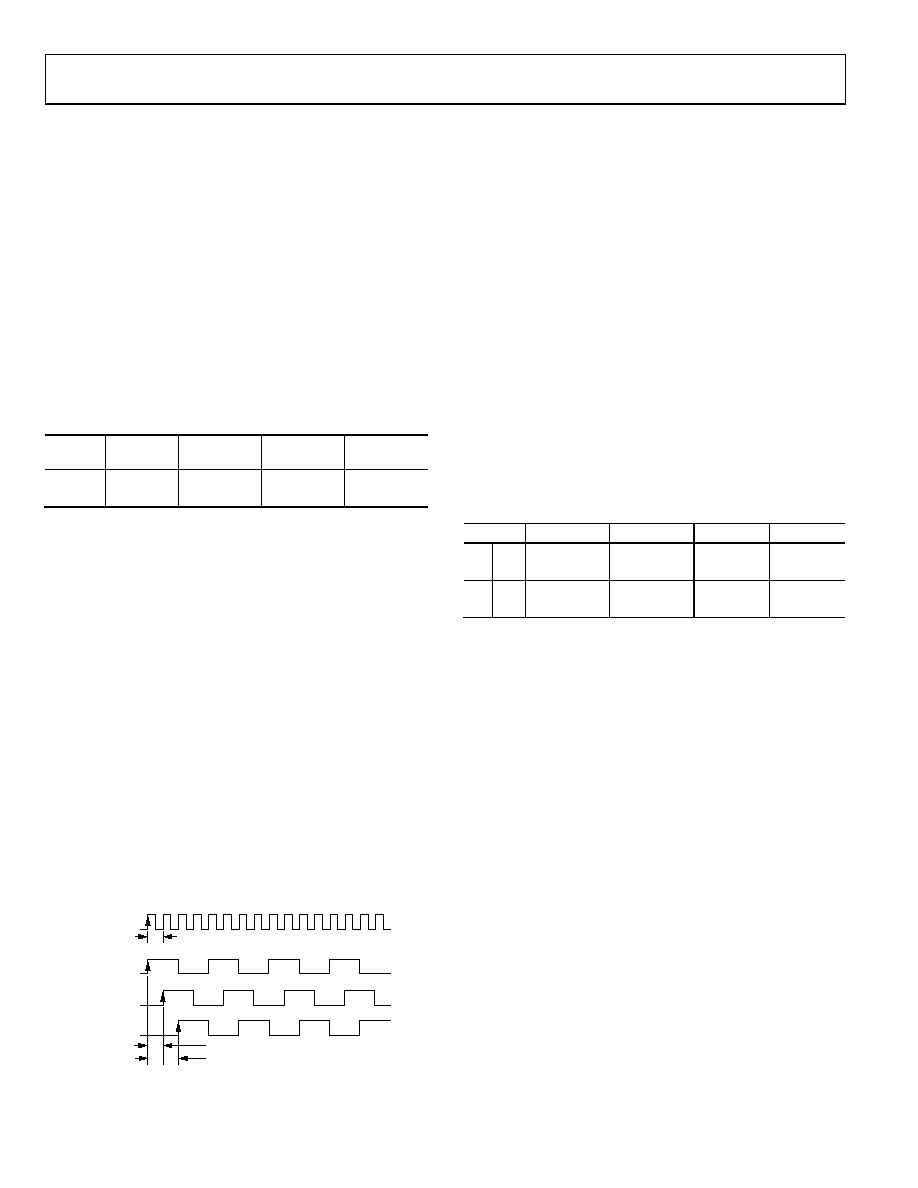

By giving each divider a different phase offset, output-to-output

delays can be set in increments of the channel divider input

clock cycle. Figure 55 shows the results of setting such a coarse

offset between outputs.

CHANNEL DIVIDER OUTPUTS

DIV = 4, DUTY = 50%

01

23

456

78

9 10 11 12 13 14 15

Tx

DIVIDER 0

DIVIDER 1

DIVIDER 2

CHANNEL

DIVIDER INPUT

SH = 0

PO = 0

SH = 0

PO = 1

SH = 0

PO = 2

1 × Tx

2 × Tx

0

6427-

071

Figure 55. Effect of Coarse Phase Offset (or Delay)

Channel Dividers—LVDS/CMOS Outputs

Channel Divider 2 and Channel Divider 3 each drive a pair of

LVDS outputs, giving a total of four LVDS outputs (OUT4 to

OUT7). Alternatively, each of these LVDS differential outputs

can be configured individually as a pair (A and B) of CMOS

single-ended outputs, providing for up to eight CMOS outputs.

By default, the B output of each pair is off but can be turned on

as desired.

Channel Divider 2 and Channel Divider 3 each consist of two

cascaded, 2 to 32, frequency dividers. The channel frequency

division is DX.1 × DX.2 or up to 1024. Divide-by-1 is achieved by

bypassing one or both of these dividers. Both of the dividers

also have DCC enabled by default, but this function can be

disabled, if desired, by setting the DCCOFF bit of the channel.

A coarse phase offset or delay is also programmable (see the

section). The channel dividers operate up to 1600 MHz. The

features and settings of the dividers are selected by programming

the appropriate setup and control registers (see Table 52 and

Divider

M

N

Bypass

DCCOFF

2

2.1

0x199[7:4]

0x199[3:0]

0x19C[4]

0x19D[0]

2.2

0x19B[7:4]

0x19B[3:0]

0x19C[5]

0x19D[0]

3

3.1

0x19E[7:4]

0x19E[3:0]

0x1A1[4]

0x1A2[0]

3.2

0x1A0[7:4]

0x1A0[3:0]

0x1A1[5]

0x1A2[0]

1 Note that the value stored in the register = # of cycles minus 1.

Channel Frequency Division (Divider 2 and Divider 3)

The division for each channel divider is set by the bits in the

registers for the individual dividers (X.Y = 2.1, 2.2, 3.1, and 3.2)

Number of Low Cycles = MX.Y + 1

Number of High Cycles = NX.Y + 1

When both X.1 and X.2 are bypassed, DX = 1 × 1 = 1.

When only X.2 is bypassed, DX = (NX.1 + MX.1 + 2) × 1.

When both X.1 and X.2 are not bypassed, DX = (NX.1 + MX.1 + 2) ×

(NX.2 + MX.2 + 2).

By cascading the dividers, channel division up to 1024 can be

obtained. However, not all integer value divisions from 1 to

1024 are obtainable; only the values that are the product of the

separate divisions of the two dividers (DX.1 × DX.2) can be realized.

If only one divider is needed when using Divider 2 and Divider 3,

use the first one (X.1) and bypass the second one (X.2). Do not

bypass X.1 and use X.2.

相关PDF资料 |

PDF描述 |

|---|---|

| AD9517-1ABCPZ | IC CLOCK GEN 2.5GHZ VCO 48LFCSP |

| V110A48H300BL2 | CONVERTER MOD DC/DC 48V 300W |

| AD9511BCPZ | IC CLOCK DIST 5OUT PLL 48LFCSP |

| V110A48H300BL | CONVERTER MOD DC/DC 48V 300W |

| VI-B60-MV | CONVERTER MOD DC/DC 5V 150W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9517-3ABCPZ | 制造商:Analog Devices 功能描述:CLOCK GENERATOR 2.25GHZ LFCSP-48 制造商:Analog Devices 功能描述:CLOCK GENERATOR, 2.25GHZ, LFCSP-48 |

| AD9517-3ABCPZ-RL7 | 功能描述:IC CLOCK GEN 2.0GHZ VCO 48LFCSP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:2,000 系列:- 类型:PLL 时钟发生器 PLL:带旁路 输入:LVCMOS,LVPECL 输出:LVCMOS 电路数:1 比率 - 输入:输出:2:11 差分 - 输入:输出:是/无 频率 - 最大:240MHz 除法器/乘法器:是/无 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:32-LQFP 供应商设备封装:32-TQFP(7x7) 包装:带卷 (TR) |

| AD9517-3BCPZ | 制造商:Analog Devices 功能描述: |

| AD9517-3BCPZ-REEL7 | 制造商:Analog Devices 功能描述: |

| AD9517-3BCPZ-TR | 制造商:Analog Devices 功能描述:12-OUTPUT CLOCK GENERATOR WITH INTEGRATED 2.0 GHZ VCO - Tape and Reel |

发布紧急采购,3分钟左右您将得到回复。