- 您现在的位置:买卖IC网 > PDF目录9158 > AD9517-3ABCPZ (Analog Devices Inc)IC CLOCK GEN 2.0GHZ VCO 48LFCSP PDF资料下载

参数资料

| 型号: | AD9517-3ABCPZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 56/80页 |

| 文件大小: | 0K |

| 描述: | IC CLOCK GEN 2.0GHZ VCO 48LFCSP |

| 标准包装: | 1 |

| 类型: | 时钟发生器,扇出配送 |

| PLL: | 是 |

| 输入: | CMOS,LVDS,LVPECL |

| 输出: | CMOS,LVDS,LVPECL |

| 电路数: | 1 |

| 比率 - 输入:输出: | 1:12 |

| 差分 - 输入:输出: | 是/是 |

| 频率 - 最大: | 2.25GHz |

| 除法器/乘法器: | 是/无 |

| 电源电压: | 3.135 V ~ 3.465 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 48-VFQFN 裸露焊盘,CSP |

| 供应商设备封装: | 48-LFCSP-VQ(7x7) |

| 包装: | 托盘 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页当前第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页

AD9517-3

Data Sheet

Rev. E | Page 6 of 80

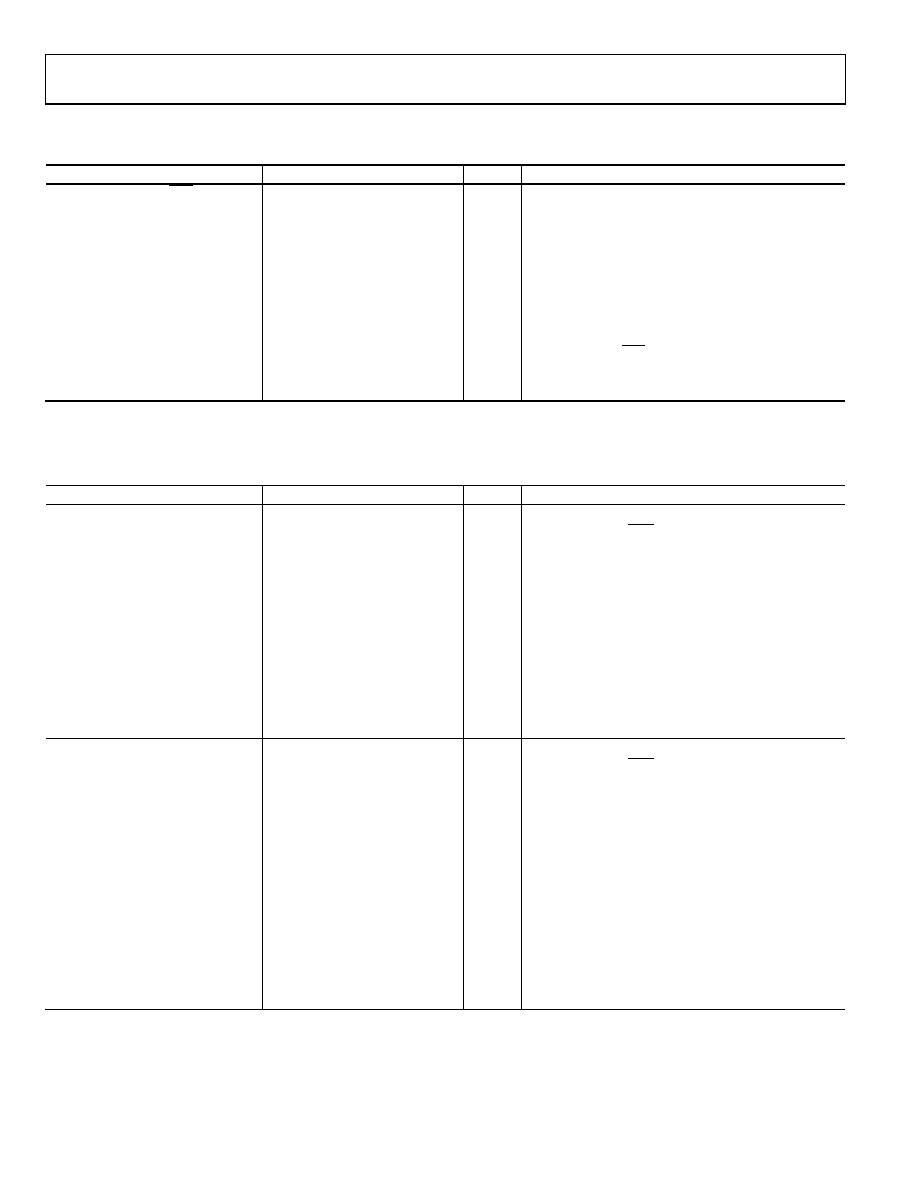

CLOCK INPUTS

Table 3.

Parameter

Min

Typ

Max

Unit

Test Conditions/Comments

CLOCK INPUTS (CLK, CLK)

Differential input

Input Frequency

2.4

GHz

High frequency distribution (VCO divider)

1.6

GHz

Distribution only (VCO divider bypassed)

Input Sensitivity, Differential

150

mV p-p

Measured at 2.4 GHz; jitter performance is improved

with slew rates > 1 V/ns

Input Level, Differential

2

V p-p

Larger voltage swings may turn on the protection

diodes and may degrade jitter performance

Input Common-Mode Voltage, VCM

1.3

1.57

1.8

V

Self-biased; enables ac coupling

Input Common-Mode Range, VCMR

1.3

1.8

V

With 200 mV p-p signal applied; dc-coupled

Input Sensitivity, Single-Ended

150

mV p-p

CLK ac-coupled; CLK ac-bypassed to RF ground

Input Resistance

3.9

4.7

5.7

k

Self-biased

Input Capacitance

2

pF

1

Below about 1 MHz, the input should be dc-coupled. Care should be taken to match VCM.

CLOCK OUTPUTS

Table 4.

Parameter

Min

Typ

Max

Unit

Test Conditions/Comments

LVPECL CLOCK OUTPUTS

Termination = 50 to VS 2 V

OUT0, OUT1, OUT2, OUT3

Differential (OUT, OUT)

Output Frequency, Maximum

2950

MHz

Using direct to output; see Figure 25 for peak-to-peak

differential amplitude

Output High Voltage (VOH)

VS_LVPECL

1.12

VS_LVPECL

0.98

VS_LVPECL

0.84

V

Output Low Voltage (VOL)

VS_LVPECL

2.03

VS_LVPECL

1.77

VS_LVPECL

1.49

V

Output Differential Voltage (VOD)

550

790

980

mV

This is VOH VOL for each leg of a differential pair for

default amplitude setting with driver not toggling; the

peak-to-peak amplitude measured using a differential

probe across the differential pair with the driver

toggling is roughly 2× these values (see Figure 25 for

variation over frequency)

LVDS CLOCK OUTPUTS

Differential termination 100 at 3.5 mA

OUT4, OUT5, OUT6, OUT7

Differential (OUT, OUT)

Output Frequency

800

MHz

The AD9517 outputs toggle at higher frequencies, but

the output amplitude may not meet the VOD

specification; see Figure 26

Output Differential Voltage (VOD)

247

360

454

mV

VOH VOL measurement across a differential pair at the

default amplitude setting with output driver not

toggling; see Figure 26 for variation over frequency

Delta VOD

25

mV

This is the absolute value of the difference between

VOD when the normal output is high vs. when the

complementary output is high

Output Offset Voltage (VOS)

1.125

1.24

1.375

V

(VOH + VOL)/2 across a differential pair

Delta VOS

25

mV

This is the absolute value of the difference between

VOS when the normal output is high vs. when the

complementary output is high

Short-Circuit Current (ISA, ISB)

14

24

mA

Output shorted to GND

相关PDF资料 |

PDF描述 |

|---|---|

| AD9517-1ABCPZ | IC CLOCK GEN 2.5GHZ VCO 48LFCSP |

| V110A48H300BL2 | CONVERTER MOD DC/DC 48V 300W |

| AD9511BCPZ | IC CLOCK DIST 5OUT PLL 48LFCSP |

| V110A48H300BL | CONVERTER MOD DC/DC 48V 300W |

| VI-B60-MV | CONVERTER MOD DC/DC 5V 150W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9517-3ABCPZ | 制造商:Analog Devices 功能描述:CLOCK GENERATOR 2.25GHZ LFCSP-48 制造商:Analog Devices 功能描述:CLOCK GENERATOR, 2.25GHZ, LFCSP-48 |

| AD9517-3ABCPZ-RL7 | 功能描述:IC CLOCK GEN 2.0GHZ VCO 48LFCSP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:2,000 系列:- 类型:PLL 时钟发生器 PLL:带旁路 输入:LVCMOS,LVPECL 输出:LVCMOS 电路数:1 比率 - 输入:输出:2:11 差分 - 输入:输出:是/无 频率 - 最大:240MHz 除法器/乘法器:是/无 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:32-LQFP 供应商设备封装:32-TQFP(7x7) 包装:带卷 (TR) |

| AD9517-3BCPZ | 制造商:Analog Devices 功能描述: |

| AD9517-3BCPZ-REEL7 | 制造商:Analog Devices 功能描述: |

| AD9517-3BCPZ-TR | 制造商:Analog Devices 功能描述:12-OUTPUT CLOCK GENERATOR WITH INTEGRATED 2.0 GHZ VCO - Tape and Reel |

发布紧急采购,3分钟左右您将得到回复。