- 您现在的位置:买卖IC网 > PDF目录1894 > AD9895KBCZRL (Analog Devices Inc)IC CCD SIGNAL PROC/GEN 64-CSPBGA PDF资料下载

参数资料

| 型号: | AD9895KBCZRL |

| 厂商: | Analog Devices Inc |

| 文件页数: | 15/58页 |

| 文件大小: | 0K |

| 描述: | IC CCD SIGNAL PROC/GEN 64-CSPBGA |

| 标准包装: | 2,000 |

| 类型: | CCD 信号处理器,12 位 |

| 输入类型: | 逻辑 |

| 输出类型: | 逻辑 |

| 接口: | 3 线串口 |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 64-VFBGA,CSPBGA |

| 供应商设备封装: | 64-CSPBGA(9x9) |

| 包装: | 带卷 (TR) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页当前第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页

REV. A

–22–

AD9891/AD9895

Second Vertical Sequence During VSG Lines

Most CCDs require additional vertical timing during the sensor

gate line. The AD9891/AD9895 supports the option to output a

second set of sequences for V1–V4 during the line when the sen-

sor gates VSG1–VSG4 are active. Figure 25 shows a typical VSG

line, which includes two separate sets of vertical sequences on V1–

V4. The sequences at the start of the line are the same as those

generated in the previous line. But the second sequence only

occurs in the line where the VSG signals are active. To select the

sequences used for the second sequence, the registers in

Table XI are used. To enable the second set of sequences during

the VSG line, the VTP_SGLINEMODE is set HIGH. As with

the standard vertical regions, each V1–V4 output has an indi-

vidual start position, programmed in the VxSTART_SGLINE

Registers. Each V1–V4 output can select from the pool of 12

unique sequences using individual sequence pointer registers,

VxSPTR_SGLINE. Also, any sequence may be inverted for a

particular V1–V4 output by using the VxINV_SGLINE Registers.

Vertical Sweep Mode Operation

The AD9891/AD9895 contains a special mode of vertical timing

operation called Sweep Mode. This mode is used to generate a

large number of repetitive pulses that span across multiple HD

lines. One example of where this mode may be needed is at the

start of the CCD readout operation. At the end of the image

exposure, but before the image is transferred by the sensor gate

pulses, the vertical interline CCD Registers should be “clean” of

all charge. This can be accomplished by quickly shifting out any

charge with a long series of pulses on the V1–V4 outputs. De-

pending on the vertical resolution of the CCD, up to two or

three thousand clock cycles will be needed to shift the charge out

of each vertical CCD line. This operation will span across mul-

tiple HD line lengths. Normally, the AD9891/AD9895 sequences

are contained within one HD line length. But when Sweep Mode

is enabled, the HD boundaries will be ignored until the region is

finished. To enable Sweep Mode within any region, program

the appropriate SWEEP (0–4) Registers to HIGH.

Figure 26 shows an example of the Sweep Mode operation. The

number of vertical pulses needed will depend on the vertical

resolution of the CCD. The V1–V4 output signals are generated

using the Individual Vertical Sequence Registers (shown in Table

VII). A single pulse is created using the first, second, and third

toggle positions, and then the number of repeats is set to the

number of vertical shifts required by the CCD. The maximum

number of repeats is 4096 in this mode, using the VTPREP

Register. This produces a pulse train of the appropriate length.

Normally, the pulse train would be truncated at the end of the

HD line length. But with Sweep Mode enabled for this region, the

HD boundaries will be ignored. In Figure 26, the sweep region

occupies 23 HD lines. After the Sweep Mode region is completed,

normal sequence operation will resume in the next region.

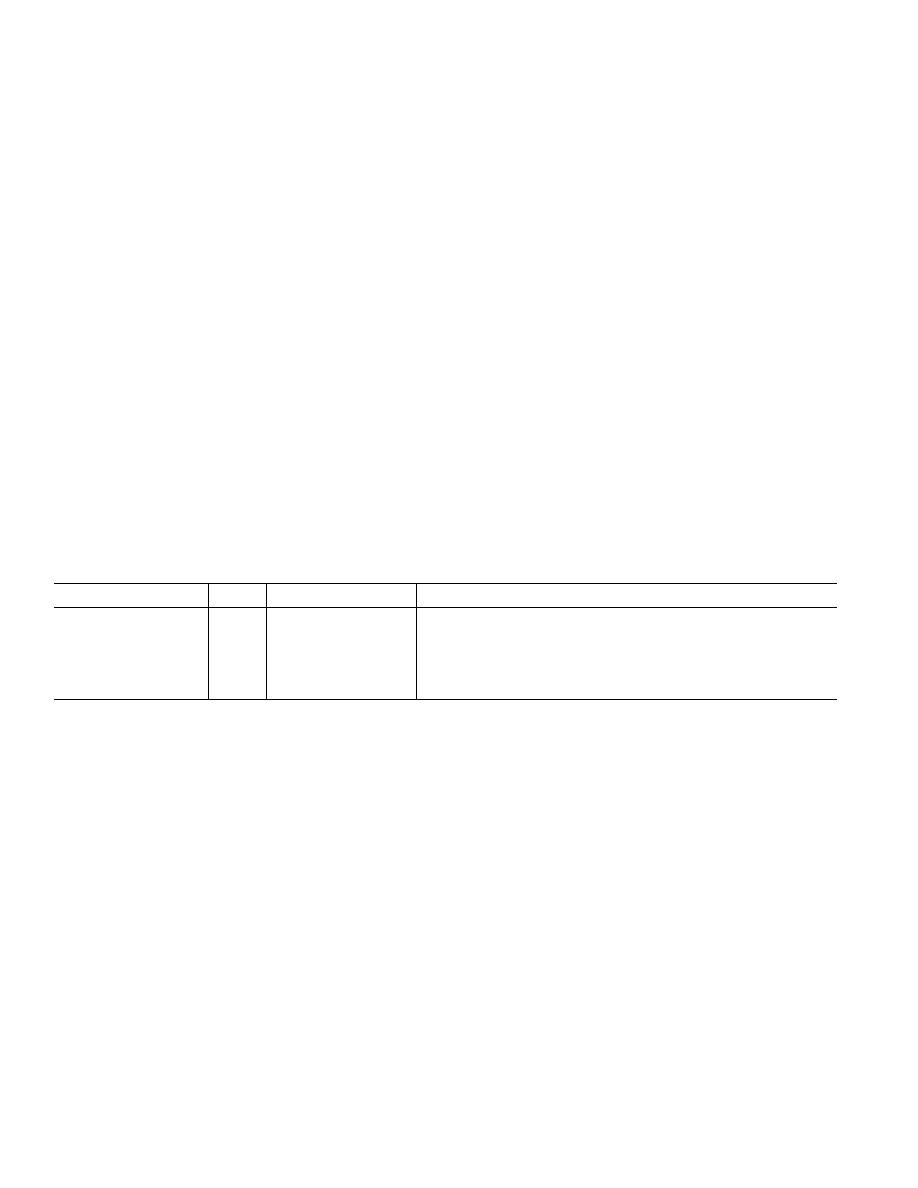

Table XI. Second Vertical Sequence Registers During SG Lines

Register Name

Length

Range

Description

VTP_SGLINEMODE

1b

HIGH/LOW

To Turn on Second Sequences during SG Line, Set = HIGH

VxSTART_SGLINE

12b

0–4095 Pixel Location

Sequence Start Position for Each Vx Output for SG Line Sequence

VxSPTR_SGLINE

4b

0–11 Sequence #

Sequence Pointer for Vx Output during second SG Line Sequence

VxINV_SGLINE

1b

HIGH/LOW

When HIGH, the Polarity of Sequence VxSPTRFIRST Is Inverted

x is the V-output from 1–4.

相关PDF资料 |

PDF描述 |

|---|---|

| AD9910BSVZ-REEL | IC DDS 1GSPS 14BIT PAR 100TQFP |

| AD9911BCPZ-REEL7 | IC DDS 500MSPS DAC 10BIT 56LFCSP |

| AD9912ABCPZ | IC DDS 1GSPS DAC 14BIT 64LFCSP |

| AD9913BCPZ-REEL7 | IC DDS 250MSPS 10BIT ADC 32LFCSP |

| AD9923ABBCZ | IC PROCESSOR CCD 12BIT 105CSPBGA |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9898 | 制造商:AD 制造商全称:Analog Devices 功能描述:CCD Signal Processor with Precision Timing⑩ Generator |

| AD9898KCP-20 | 制造商:Rochester Electronics LLC 功能描述:10 BIT 20 MSPS ANALOG FRONT END CONVERTE - Bulk 制造商:Analog Devices 功能描述: |

| AD9898KCPRL-20 | 制造商:AD 制造商全称:Analog Devices 功能描述:CCD Signal Processor with Precision Timing⑩ Generator |

| AD9899ARS-2 | 制造商:Analog Devices 功能描述: |

| AD9901 | 制造商:AD 制造商全称:Analog Devices 功能描述:Ultrahigh Speed Phase/Frequency Discriminator |

发布紧急采购,3分钟左右您将得到回复。