- 您现在的位置:买卖IC网 > PDF目录1894 > AD9895KBCZRL (Analog Devices Inc)IC CCD SIGNAL PROC/GEN 64-CSPBGA PDF资料下载

参数资料

| 型号: | AD9895KBCZRL |

| 厂商: | Analog Devices Inc |

| 文件页数: | 27/58页 |

| 文件大小: | 0K |

| 描述: | IC CCD SIGNAL PROC/GEN 64-CSPBGA |

| 标准包装: | 2,000 |

| 类型: | CCD 信号处理器,12 位 |

| 输入类型: | 逻辑 |

| 输出类型: | 逻辑 |

| 接口: | 3 线串口 |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 64-VFBGA,CSPBGA |

| 供应商设备封装: | 64-CSPBGA(9x9) |

| 包装: | 带卷 (TR) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页当前第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页

REV. A

AD9891/AD9895

–33–

PxGA GAIN REGISTER CODE

10

32

PxGA

GAIN

–

dB

40

48

58

0

8

16

24

31

6

4

2

0

–2

–4

8

(100000)

(011111)

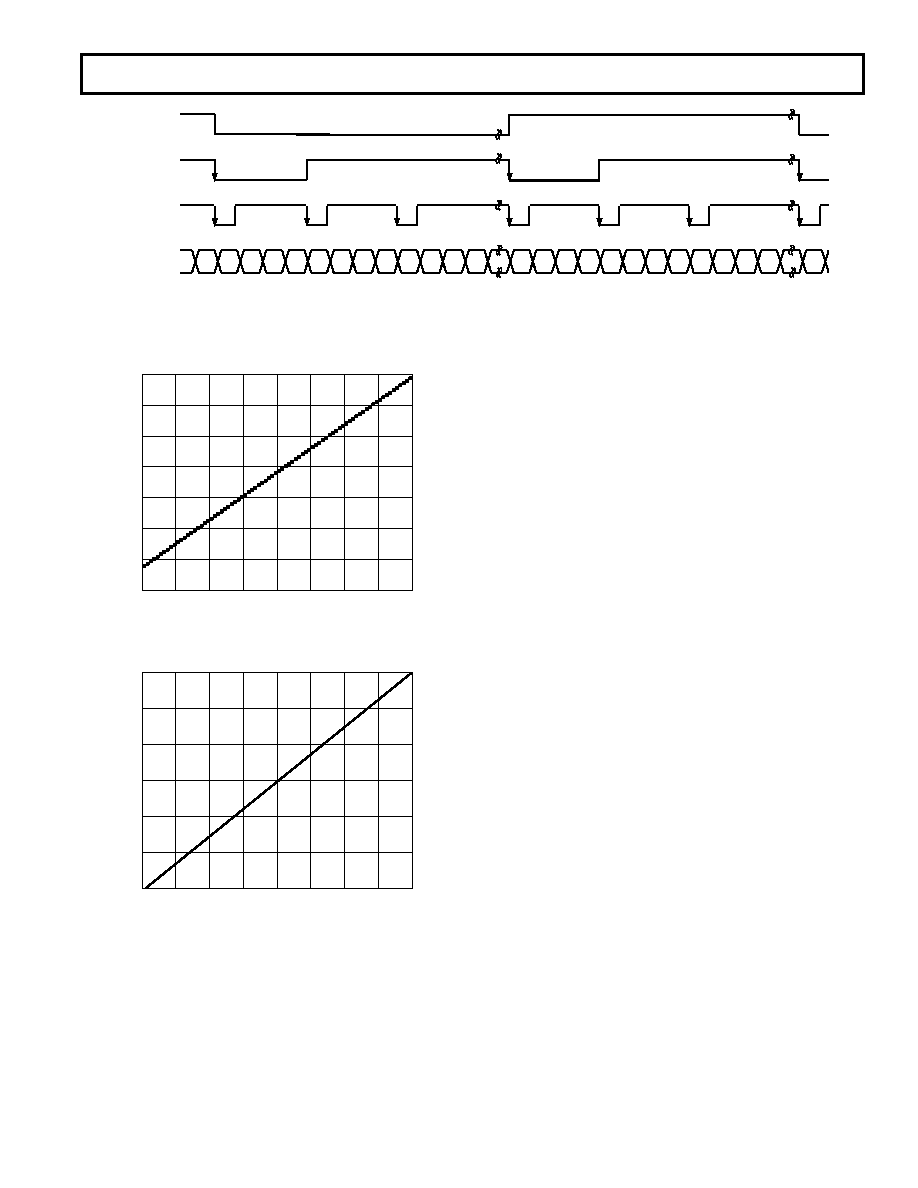

Figure 40. PxGA Gain Curve

VGA GAIN REGISTER CODE

36

0

1023

127

VG

A

GAIN

–

dB

255

383

511

639

767

895

30

24

18

12

6

Figure 41. VGA Gain Curve (PxGA not included)

Variable Gain Amplifier

The VGA stage provides a gain range of 2 dB to 36 dB, pro-

grammable with 10-bit resolution through the serial digital

interface. Combined with approximately 4 dB from the PxGA

stage, the total gain range for the AD9891/AD9895 is 6 dB to

40 dB. The minimum gain of 6 dB is needed to match a 1 V

input signal with the ADC full-scale range of 2 V. When com-

pared to 1 V full-scale systems (such as ADI’s AD9803), the

equivalent gain range is 0 dB to 34 dB.

The VGA gain curve follows a “linear-in-dB” characteristic.

The exact VGA gain can be calculated for any gain register

value by using the equation:

Gain

Code

=×

+

(.

)

.

0 035

3 55

where the code range is 0 to 1023. PxGA default gain is included.

The gain accuracy specifications include the PxGA gain of

approximately 4 dB, for a total gain range of 6 dB to 40 dB.

Optical Black Clamp

The optical black clamp loop is used to remove residual offsets

in the signal chain and to track low frequency variations in the

CCD’s black level. During the optical black (shielded) pixel

interval on each line, the ADC output is compared with a fixed

black level reference selected by the user in the Clamp Level

Register. The clamp level is programmable in 256 steps, with a

range between 0 LSB and 63.75 LSB in the AD9891 and be-

tween 0 LSB and 255 LSB in the AD9895. The resulting error

signal is filtered to reduce noise, and the correction value is

applied to the ADC input through a D/A converter. Normally,

the optical black clamp loop is turned on once per horizontal

line, but this loop can be updated more slowly to suit a particu-

lar application. If external digital clamping is used during

the post- processing, the AD9891/AD9895 optical black

clamping may be disabled using Bit D5 in the Operation Regis-

ter (see Serial Interface Timing and Register Listing sections).

When the loop is disabled, the Clamp Level Register may still

be used to provide programmable offset adjustment.

The optical black clamp is controlled by the CLPOB signal,

which is fully programmable (see Horizontal Clamping and

Blanking section). System timing examples are shown in the

Horizontal Timing Sequence Example section. The CLPOB

pulse should be placed during the CCD’s optical black pixels. It

is recommended that the CLPOB pulse duration be at least

20 pixels wide. Shorter pulsewidths may be used, but the ability

to track low frequency variations in the black level will be

reduced.

A/D Converter

The AD9891 uses a high a performance 10-bit ADC archi-

tecture, optimized for high speed and low power, while the

AD9895 uses a 12-bit ADC architecture. Differential

nonlinearity (DNL) performance is typically better than

0.5 LSB for both products. The ADC uses a 2 V input range.

Better noise performance results from using a larger ADC full-

scale range.

VD

NOTES

1. VD FALLING EDGE WILL RESET THE PxGA GAIN REGISTER STEERING TO “01230123” LINE.

2. HD FALLING EDGES WILL ALTERNATE THE PxGA GAIN REGISTER STEERING BETWEEN “01230123” AND “23012301” LINES.

3. FLD STATUS IS IGNORED.

HD

02

0

2

13

20

31

20

31

X

PxGA GAIN

REGISTER

FLD

ODD FIELD

EVEN FIELD

Figure 39g. 4-Color 2-Color Steering Mode

相关PDF资料 |

PDF描述 |

|---|---|

| AD9910BSVZ-REEL | IC DDS 1GSPS 14BIT PAR 100TQFP |

| AD9911BCPZ-REEL7 | IC DDS 500MSPS DAC 10BIT 56LFCSP |

| AD9912ABCPZ | IC DDS 1GSPS DAC 14BIT 64LFCSP |

| AD9913BCPZ-REEL7 | IC DDS 250MSPS 10BIT ADC 32LFCSP |

| AD9923ABBCZ | IC PROCESSOR CCD 12BIT 105CSPBGA |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9898 | 制造商:AD 制造商全称:Analog Devices 功能描述:CCD Signal Processor with Precision Timing⑩ Generator |

| AD9898KCP-20 | 制造商:Rochester Electronics LLC 功能描述:10 BIT 20 MSPS ANALOG FRONT END CONVERTE - Bulk 制造商:Analog Devices 功能描述: |

| AD9898KCPRL-20 | 制造商:AD 制造商全称:Analog Devices 功能描述:CCD Signal Processor with Precision Timing⑩ Generator |

| AD9899ARS-2 | 制造商:Analog Devices 功能描述: |

| AD9901 | 制造商:AD 制造商全称:Analog Devices 功能描述:Ultrahigh Speed Phase/Frequency Discriminator |

发布紧急采购,3分钟左右您将得到回复。