- 您现在的位置:买卖IC网 > PDF目录16915 > ADP1043A-USB-Z (Analog Devices Inc)EVAL BOARD DIG POWER SUPPLY PDF资料下载

参数资料

| 型号: | ADP1043A-USB-Z |

| 厂商: | Analog Devices Inc |

| 文件页数: | 46/72页 |

| 文件大小: | 0K |

| 描述: | EVAL BOARD DIG POWER SUPPLY |

| 标准包装: | 1 |

| 附件类型: | 连接 USB 至 I2C 的接收器 |

| 适用于相关产品: | ADP1043A |

| 相关产品: | ADP1043AACPZ-RLDKR-ND - IC SECONDARY SIDE CTRLR 32LFCSP ADP1043AACPZ-RLCT-ND - IC SECONDARY SIDE CTRLR 32LFCSP ADP1043AACPZ-RLTR-ND - IC SECONDARY SIDE CTRLR 32LFCSP |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页当前第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页

�� �

�

�

�ADP1043A�

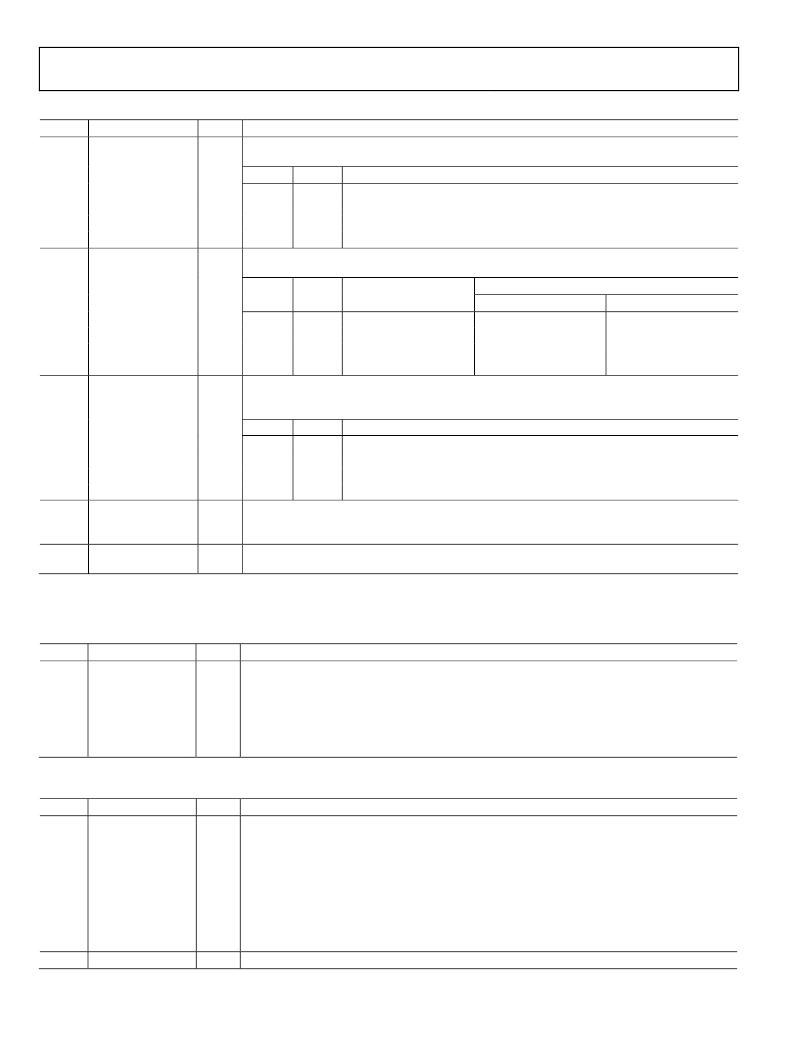

�Table� 44.� Register� 0x30—OrFET�

�Bits�

�[7:6]�

�[5:4]�

�Name�

�Accurate� OrFET�

�threshold�

�OrFET� enable�

�threshold�

�R/W�

�R/W�

�R/W�

�Description�

�These� bits� program� the� voltage� difference� between� CS2+� and� CS2?� at� which� the� accurate� OrFET�

�flag� is� set.� The� CS2+� and� CS2?� input� pins� are� used� to� control� this� function.�

�Bit� 7�

�Bit� 6�

�Voltage� Drop� Across� Sense� Resistor� from� CS2+� to� CS2?� (Threshold)�

�0�

�0�

�0� mV�

�0�

�1�

�Reserved�

�1�

�0�

�Reserved�

�1�

�1�

�Reserved�

�These� bits� program� the� voltage� difference� between� VS1� and� VS2� before� the� OrFET� is� enabled.� The�

�VS1� and� VS2� input� pins� are� used� to� control� the� OrFET� enable� function.�

�Voltage� Difference� from� VS1� to� VS2�

�Bit� 5�

�0�

�0�

�1�

�1�

�Bit� 4�

�0�

�1�

�0�

�1�

�%� of� ADC� Full� Range�

�?0.5�

�0�

�1�

�2�

�12� V� V� OUT� (mV)�

�?93�

�0�

�186�

�372�

�48� V� V� OUT� (mV)�

�?372�

�0�

�744�

�1488�

�[3:2]�

�Fast� OrFET�

�threshold�

�R/W�

�These� bits� program� the� threshold� voltage� difference� between� CS2+� and� CS2?� at� which� the� OrFET�

�is� disabled.� The� CS2+� and� CS2?� input� pins� are� used� to� control� this� function.� The� internal� circuit� is�

�an� analog� comparator.�

�Bit� 3�

�0�

�0�

�1�

�1�

�Bit� 2�

�0�

�1�

�0�

�1�

�Voltage� Difference� from� CS2+� to� CS2?� (mV)�

�?100�

�?75�

�?50�

�?25�

�1�

�Fast� OrFET�

�debounce�

�R/W�

�These� bits� determine� the� debounce� on� the� fast� OrFET� control� before� it� disables� the� OrFET.�

�0� =� 40� ns.�

�1� =� 200� ns.�

�0�

�Fast� OrFET� bypass�

�R/W�

�Set� this� bit� to� completely� bypass� the� fast� OrFET� control.� To� also� bypass� the� accurate� OrFET� disable�

�control,� the� response� to� the� accurate� OrFET� disable� flag� should� be� set� to� ignore.�

�VOLTAGE� SENSE� REGISTERS�

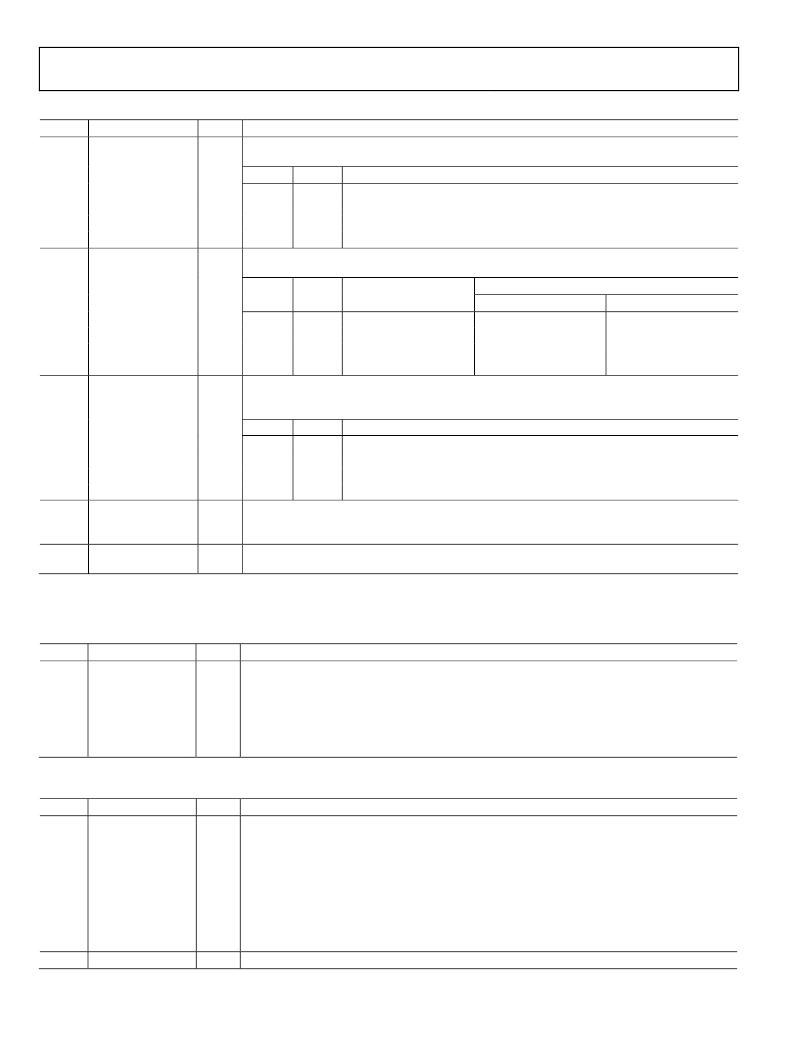

�Table 45. Register 0x31—VS3 Voltag� e� Setting� (Remote� Voltage)�

�Bits�

�[7:0]�

�Name�

�VS3� voltage� setting�

�R/W�

�R/W�

�Description�

�This� register� is� used� to� set� the� output� voltage� (voltage� differential� at� the� VS3+� and� VS3?� pins).�

�Programmable� from� 0%� to� 155%� of� nominal� voltage.� Each� LSB� corresponds� to� a� 0.6%� increase.�

�Setting� this� register� to� a� value� of� 0xA5� gives� an� output� voltage� setting� of� 100%� of� the� nominal�

�voltage.� This� is� the� default� value� and� is� stored� in� this� register� when� shipped� from� the� factory.�

�Updating� the� VS3� voltage� setting� is� a� two-stage� process.� First,� the� user� must� change� the� value� in�

�this� register;� this� information� is� stored� in� a� shadow� register.� To� latch� the� new� VS3� voltage� setting�

�into� the� state� machine,� the� user� must� set� the� GO� bit� (Register� 0x5D[0]).�

�Table� 46.� Register� 0x32—VS1� Overvoltage� Limit� (OVP)�

�Bits�

�[7:3]�

�Name�

�VS1� OVP� setting�

�R/W�

�R/W�

�Description�

�Local� overvoltage� limit.� This� limit� is� programmable� from� 107.7%� to� 145.3%� of� the� nominal� VS1�

�voltage;� 0x00� corresponds� to� 107.7%.� Each� LSB� results� in� an� increase� of� 1.21%.� The� VS1� OVP�

�threshold� is� calculated� as� follows:�

�VS1_OVP_Threshold� =� [(89� +� VS1_OVP_Setting� )/128]� � 1.55� V�

�For� example,� if� the� VS1� OVP� setting� is� 10,� then�

�VS1_OVP_Threshold� =� [(89� +� 10)/128]� � 1.55� V� =� 1.2� V�

�Setting� these� bits� to� 0� gives� an� OVP� limit� of� 107.7%� of� the� nominal� VS1� voltage.�

�Setting� these� bits� to� 10� gives� an� OVP� limit� of� 120%� of� the� nominal� VS1� voltage.�

�Setting� these� bits� to� 20� gives� an� OVP� limit� of� 132%� of� the� nominal� VS1� voltage.�

�Setting� these� bits� to� 31� gives� an� OVP� limit� of� 145.3%� of� the� nominal� VS1� voltage.�

�2�

�Reserved�

�R/W�

�Reserved.�

�Rev.� 0� |� Page� 46� of� 72�

�相关PDF资料 |

PDF描述 |

|---|---|

| VE-2TZ-EX | CONVERTER MOD DC/DC 2V 30W |

| GCM15DTAS | CONN EDGECARD 30POS R/A .156 SLD |

| 202D232-4-61/42-0 | BOOT MOLDED |

| VE-2TZ-EW | CONVERTER MOD DC/DC 2V 40W |

| GSM06DREF | CONN EDGECARD 12POS .156 EYELET |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADP1043-EVALZ | 制造商:Analog Devices 功能描述:EVALUATION BOARDS - Bulk |

| ADP1043FB100-EVALZ | 制造商:Analog Devices 功能描述:ADP1043 100W EVALUATION BOARD |

| ADP1045ACPZ-RL | 制造商:Analog Devices 功能描述: |

| ADP1046 | 制造商:AD 制造商全称:Analog Devices 功能描述:Digital Controller for Isolated |

| ADP1046-100-EVALZ | 功能描述:BOARD EVAL FOR ADP1046-100 RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:- 标准包装:1 系列:PCI Express® (PCIe) 主要目的:接口,收发器,PCI Express 嵌入式:- 已用 IC / 零件:DS80PCI800 主要属性:- 次要属性:- 已供物品:板 |

发布紧急采购,3分钟左右您将得到回复。