- 您现在的位置:买卖IC网 > PDF目录1899 > ADSP-21160MKB-80 (Analog Devices Inc)IC DSP CONTROLLER 32BIT 400 BGA PDF资料下载

参数资料

| 型号: | ADSP-21160MKB-80 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 31/52页 |

| 文件大小: | 0K |

| 描述: | IC DSP CONTROLLER 32BIT 400 BGA |

| 产品培训模块: | SHARC Processor Overview |

| 标准包装: | 1 |

| 系列: | SHARC® |

| 类型: | 浮点 |

| 接口: | 主机接口,连接端口,串行端口 |

| 时钟速率: | 80MHz |

| 非易失内存: | 外部 |

| 芯片上RAM: | 512kB |

| 电压 - 输入/输出: | 3.30V |

| 电压 - 核心: | 2.50V |

| 工作温度: | 0°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 400-BBGA |

| 供应商设备封装: | 400-PBGA(27x27) |

| 包装: | 托盘 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页当前第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页

–37–

REV. 0

ADSP-21160M

Serial Ports

To determine whether communication is possible between

two devices at clock speed n, the following specifications

must be confirmed: 1) frame sync delay and frame sync

setup and hold, 2) data delay and data setup and hold, and

3) SCLK width.

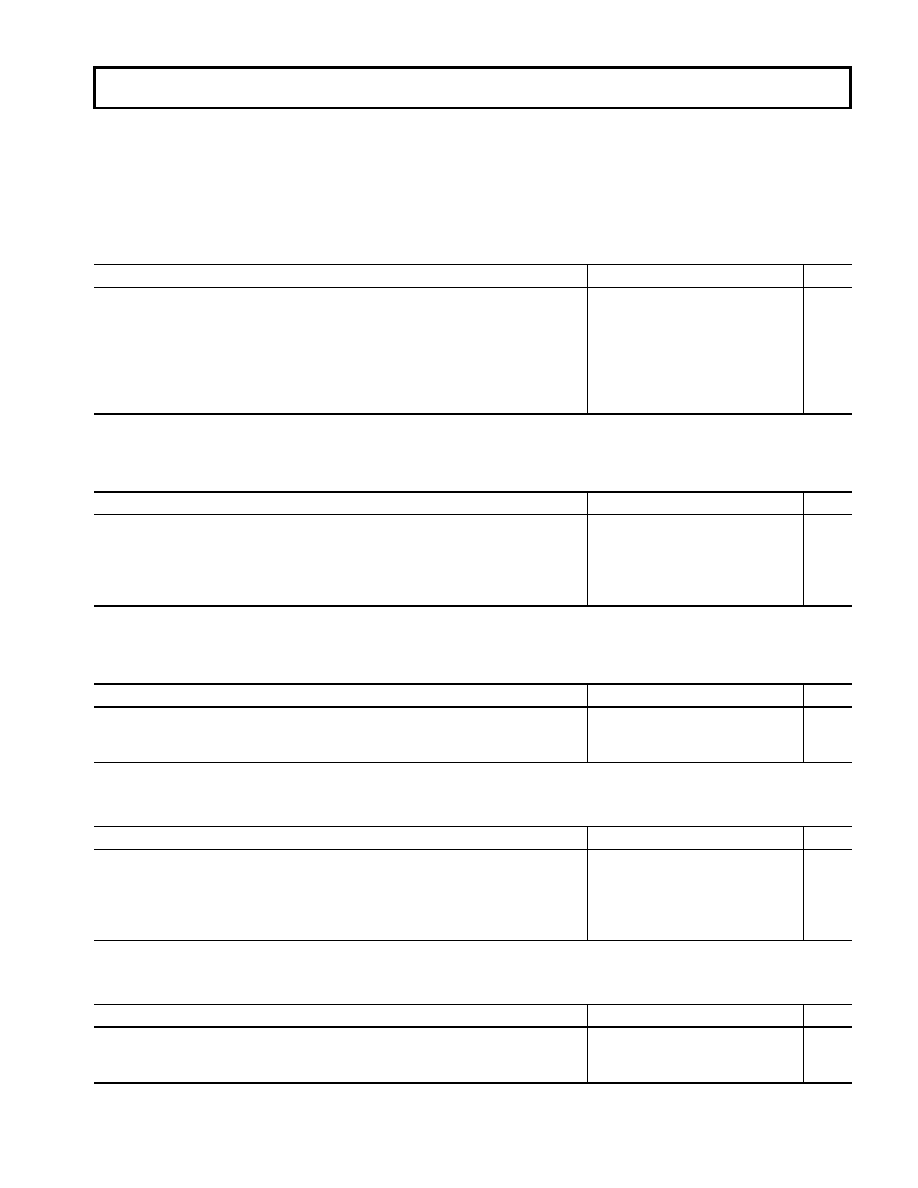

Table 21. Serial Ports—External Clock

Parameter

Min

Max

Unit

Timing Requirements:

t

SFSE

TFS/RFS Setup Before TCLK/RCLK1

3.5

ns

t

HFSE

TFS/RFS Hold After TCLK/RCLK1,2

4ns

t

SDRE

Receive Data Setup Before RCLK1

1.5

ns

t

HDRE

Receive Data Hold After RCLK1

4ns

t

SCLKW

TCLK/RCLK Width

14

ns

t

SCLK

TCLK/RCLK Period

2t

CCLK

ns

1 Referenced to sample edge.

2 RFS hold after RCK when MCE = 1, MFD= 0 is 0 ns minimumfrom drive edge. TFS hold after TCK for late external TFS is 0 ns minimum from drive edge.

Table 22. Serial Ports—Internal Clock

Parameter

Min

Max

Unit

Timing Requirements:

t

SFSI

8ns

t

HFSI

TFS/RFS Hold After TCLK/RCLK1,2

1ns

t

SDRI

Receive Data Setup Before RCLK1

6.5

ns

t

HDRI

Receive Data Hold After RCLK1

3ns

1 Referenced to sample edge.

2 RFS hold after RCK when MCE = 1, MFD= 0 is 0 ns minimumfrom drive edge. TFS hold after TCK for late external TFS is 0 ns minimum from drive edge.

Table 23. Serial Ports—External or Internal Clock

Parameter

Min

Max

Unit

Switching Characteristics:

t

DFSE

RFS Delay After RCLK (Internally Generated RFS)1

13

ns

t

HOFSE

RFS Hold After RCLK (Internally Generated RFS)1

3ns

1 Referenced to drive edge.

Table 24. Serial Ports—External Clock

Parameter

Min

Max

Unit

Switching Characteristics:

t

DFSE

TFS Delay After TCLK (Internally Generated TFS)1

13

ns

t

HOFSE

TFS Hold After TCLK (Internally Generated TFS)1

3ns

t

DDTE

Transmit Data Delay After TCLK1

16

ns

t

HDTE

Transmit Data Hold After TCLK1

0ns

1 Referenced to drive edge.

Table 25. Serial Ports—Internal Clock

Parameter

Min

Max

Unit

Switching Characteristics:

t

DFSI

TFS Delay After TCLK (Internally Generated TFS)1

4.5

ns

t

HOFSI

TFS Hold After TCLK (Internally Generated TFS)1

–1.5

ns

相关PDF资料 |

PDF描述 |

|---|---|

| ADSP-21160NCB-100 | IC DSP CONTROLLER 32BIT 400BGA |

| ADSP-21161NCCA-100 | IC DSP CONTROLLER 32BIT 225MBGA |

| ADSP-21261SKBCZ150 | IC DSP 32BIT 150MHZ 136-CSPBGA |

| ADSP-21368KBPZ-3A | IC DSP 32BIT 400MHZ 256BGA |

| ADSP-21371BSWZ-2B | IC DSP 32BIT 266MHZ 208-LQFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADSP-21160MKBZ-80 | 功能描述:IC DSP CONTROLLER 32BIT 400 BGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - DSP(数字式信号处理器) 系列:SHARC® 标准包装:2 系列:StarCore 类型:SC140 内核 接口:DSI,以太网,RS-232 时钟速率:400MHz 非易失内存:外部 芯片上RAM:1.436MB 电压 - 输入/输出:3.30V 电压 - 核心:1.20V 工作温度:-40°C ~ 105°C 安装类型:表面贴装 封装/外壳:431-BFBGA,FCBGA 供应商设备封装:431-FCPBGA(20x20) 包装:托盘 |

| ADSP-21160N | 制造商:AD 制造商全称:Analog Devices 功能描述:DSP Microcomputer |

| ADSP-21160NCB-100 | 功能描述:IC DSP CONTROLLER 32BIT 400BGA RoHS:否 类别:集成电路 (IC) >> 嵌入式 - DSP(数字式信号处理器) 系列:SHARC® 标准包装:2 系列:StarCore 类型:SC140 内核 接口:DSI,以太网,RS-232 时钟速率:400MHz 非易失内存:外部 芯片上RAM:1.436MB 电压 - 输入/输出:3.30V 电压 - 核心:1.20V 工作温度:-40°C ~ 105°C 安装类型:表面贴装 封装/外壳:431-BFBGA,FCBGA 供应商设备封装:431-FCPBGA(20x20) 包装:托盘 |

| ADSP-21160NCB-TBD | 制造商:AD 制造商全称:Analog Devices 功能描述:DSP Microcomputer |

| ADSP-21160NCBZ-100 | 功能描述:IC DSP CONTROLLER 32BIT 400-PBGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - DSP(数字式信号处理器) 系列:SHARC® 标准包装:40 系列:TMS320DM64x, DaVinci™ 类型:定点 接口:I²C,McASP,McBSP 时钟速率:400MHz 非易失内存:外部 芯片上RAM:160kB 电压 - 输入/输出:3.30V 电压 - 核心:1.20V 工作温度:0°C ~ 90°C 安装类型:表面贴装 封装/外壳:548-BBGA,FCBGA 供应商设备封装:548-FCBGA(27x27) 包装:托盘 配用:TMDSDMK642-0E-ND - DEVELPER KIT W/NTSC CAMERA296-23038-ND - DSP STARTER KIT FOR TMS320C6416296-23059-ND - FLASHBURN PORTING KIT296-23058-ND - EVAL MODULE FOR DM642TMDSDMK642-ND - DEVELOPER KIT W/NTSC CAMERA |

发布紧急采购,3分钟左右您将得到回复。