- 您现在的位置:买卖IC网 > PDF目录19403 > ADSP-21261SKSTZ150 (Analog Devices Inc)IC DSP 32BIT 150MHZ 144LQFP PDF资料下载

参数资料

| 型号: | ADSP-21261SKSTZ150 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 40/44页 |

| 文件大小: | 0K |

| 描述: | IC DSP 32BIT 150MHZ 144LQFP |

| 产品培训模块: | SHARC Processor Overview |

| 标准包装: | 60 |

| 系列: | SHARC® |

| 类型: | 浮点 |

| 接口: | DAI,SPI |

| 时钟速率: | 150MHz |

| 非易失内存: | ROM(384 kB) |

| 芯片上RAM: | 128kB |

| 电压 - 输入/输出: | 3.30V |

| 电压 - 核心: | 1.20V |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 144-LQFP |

| 供应商设备封装: | 144-LQFP(20x20) |

| 包装: | 托盘 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页当前第40页第41页第42页第43页第44页

ADSP-21261

Rev. 0

|

Page 5 of 44

|

March 2006

element are arranged in parallel, maximizing computational

throughput. Single multifunction instructions execute parallel

ALU and multiplier operations. In SIMD mode, the parallel

ALU and multiplier operations occur in both processing ele-

ments. These computation units support IEEE 32-bit single

precision floating-point, 40-bit extended precision floating-

point, and 32-bit fixed-point data formats.

Data Register File

A general-purpose data register file is contained in each

processing element. The register files transfer data between the

computation units and the data buses, and store intermediate

results. These 10-port, 32-register (16 primary, 16 secondary)

register files, combined with the ADSP-2126x enhanced Har-

vard architecture, allow unconstrained data flow between

computation units and internal memory. The registers in PEX

are referred to as R0–R15 and in PEY as S0–S15.

Single-Cycle Fetch of Instruction and Four Operands

The ADSP-21261 features an enhanced Harvard architecture in

which the data memory (DM) bus transfers data and the pro-

gram memory (PM) bus transfers both instructions and data

(see Figure 1 on Page 1). With the ADSP-21261’s separate pro-

gram and data memory buses and on-chip instruction cache,

the processor can simultaneously fetch four operands (two over

each data bus) and one instruction (from the cache), all in a

single cycle.

Instruction Cache

The ADSP-21261 includes an on-chip instruction cache that

enables three-bus operation for fetching an instruction and four

data values. The cache is selective—only the instructions whose

fetches conflict with PM bus data accesses are cached. This

cache allows full-speed execution of core, looped operations

such as digital filter multiply-accumulates, and FFT butterfly

processing.

Data Address Generators with Zero-Overhead Hardware

Circular Buffer Support

The ADSP-21261’s two data address generators (DAGs) are

used for indirect addressing and implementing circular data

buffers in hardware. Circular buffers allow efficient program-

ming of delay lines and other data structures required in digital

signal processing, and are commonly used in digital filters and

Fourier transforms. The two DAGs of the ADSP-21261 contain

sufficient registers to allow the creation of up to 32 circular buff-

ers (16 primary register sets, 16 secondary). The DAGs

automatically handle address pointer wraparound, reduce over-

head, increase performance, and simplify implementation.

Circular buffers can start and end at any memory location.

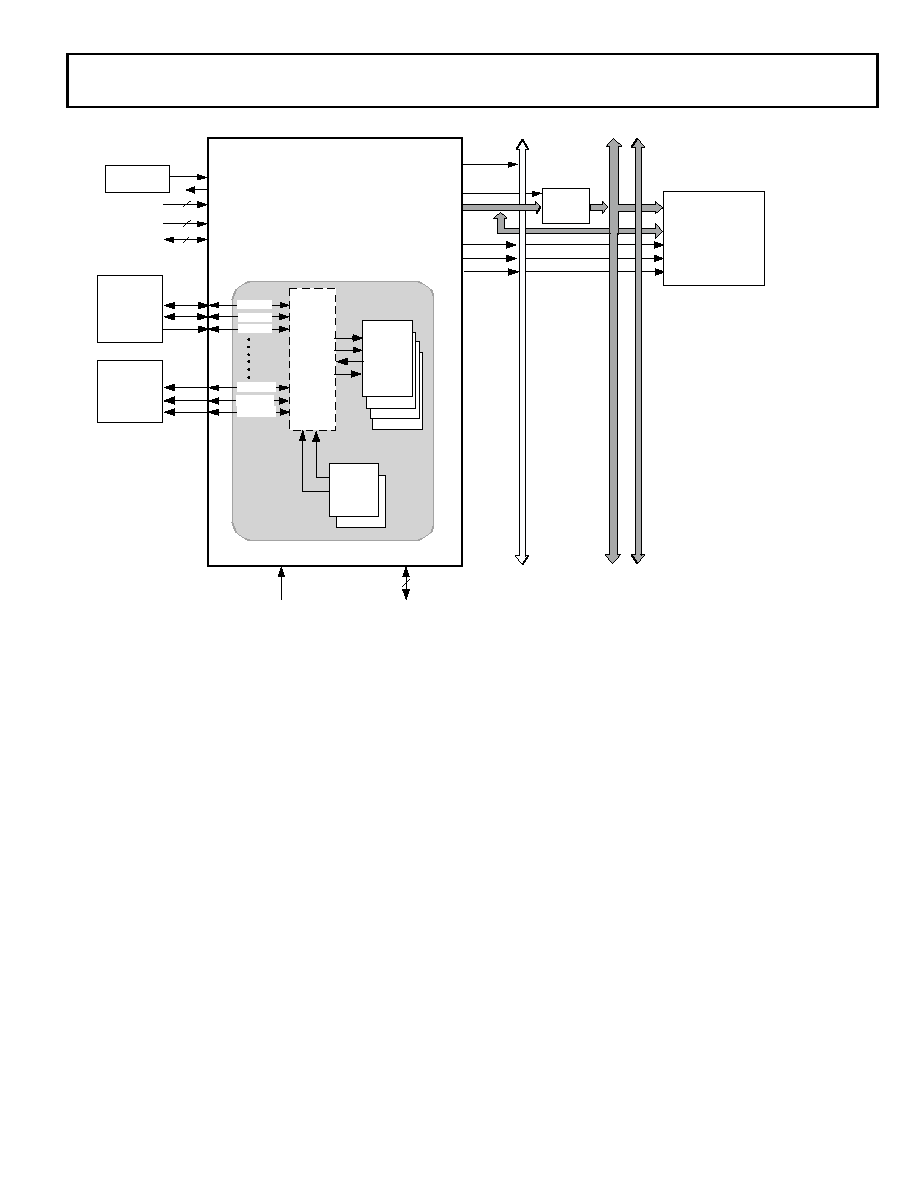

Figure 2. ADSP-21261 System Sample Configuration

DAI

SPORT3

SPO RT2

SP ORT1

SPORT0

SCLK0

SD0A

SFS0

SD0B

SRU

DAI_ P1

DAI_P 2

DAI_P 3

DAI_ P1 8

DAI_ P19

DAI_P 20

DAC

(OP TIONAL)

ADC

(OPTI ONAL)

FS

CLK

SDAT

FS

CLK

SDAT

3

CLOCK

2

CLKI N

XTAL

CLK_ CFG 1– 0

BOOTCFG1– 0

FLAG 3– 1

ADDR

PARALLE L

PO RT

RAM , ROM

BOOT ROM

I/O DEVICE

OE

DATA

WE

RD

WR

CLKOUT

ALE

AD15 –0

LATCH

RESE T

JTAG

6

ADS P-21261

ADD

RE

S

DAT

A

CO

N

T

RO

L

CS

FLAG0

PCGB

PCG A

CLK

FS

相关PDF资料 |

PDF描述 |

|---|---|

| ADSP-BF531SBBCZ4RL | IC DSP CTLR 16BIT 400MHZ 160-CSP |

| MAX6504UKP005+T | IC TEMP SWITCH SOT23-5 |

| TPSB476K010A0250 | CAP TANT 47UF 10V 10% 1210 |

| TPSB476K006H0500 | CAP TANT 47UF 6.3V 10% 1210 |

| VI-B63-EU-B1 | CONVERTER MOD DC/DC 24V 200W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADSP-21262 | 制造商:AD 制造商全称:Analog Devices 功能描述:SHARC Processor |

| ADSP-21262_05 | 制造商:AD 制造商全称:Analog Devices 功能描述:Embedded Processor |

| ADSP-21262KSTZ200 | 制造商:Analog Devices 功能描述:- Trays |

| ADSP-21262SBBC-150 | 功能描述:IC DSP 32BIT 150MHZ 136-CSPBGA RoHS:否 类别:集成电路 (IC) >> 嵌入式 - DSP(数字式信号处理器) 系列:SHARC® 标准包装:2 系列:StarCore 类型:SC140 内核 接口:DSI,以太网,RS-232 时钟速率:400MHz 非易失内存:外部 芯片上RAM:1.436MB 电压 - 输入/输出:3.30V 电压 - 核心:1.20V 工作温度:-40°C ~ 105°C 安装类型:表面贴装 封装/外壳:431-BFBGA,FCBGA 供应商设备封装:431-FCPBGA(20x20) 包装:托盘 |

| ADSP-21262SBBCZ150 | 功能描述:IC DSP 32BIT 150MHZ 136-CSPBGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - DSP(数字式信号处理器) 系列:SHARC® 标准包装:40 系列:TMS320DM64x, DaVinci™ 类型:定点 接口:I²C,McASP,McBSP 时钟速率:400MHz 非易失内存:外部 芯片上RAM:160kB 电压 - 输入/输出:3.30V 电压 - 核心:1.20V 工作温度:0°C ~ 90°C 安装类型:表面贴装 封装/外壳:548-BBGA,FCBGA 供应商设备封装:548-FCBGA(27x27) 包装:托盘 配用:TMDSDMK642-0E-ND - DEVELPER KIT W/NTSC CAMERA296-23038-ND - DSP STARTER KIT FOR TMS320C6416296-23059-ND - FLASHBURN PORTING KIT296-23058-ND - EVAL MODULE FOR DM642TMDSDMK642-ND - DEVELOPER KIT W/NTSC CAMERA |

发布紧急采购,3分钟左右您将得到回复。