- 您现在的位置:买卖IC网 > PDF目录298893 > BX805555030P (INTEL CORP) 64-BIT, MICROPROCESSOR, BGA771 PDF资料下载

参数资料

| 型号: | BX805555030P |

| 厂商: | INTEL CORP |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 64-BIT, MICROPROCESSOR, BGA771 |

| 封装: | LGA-771 |

| 文件页数: | 66/104页 |

| 文件大小: | 3690K |

| 代理商: | BX805555030P |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页当前第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页

Signal Definitions

64

Dual-Core Intel Xeon Processor 5000 Series Datasheet

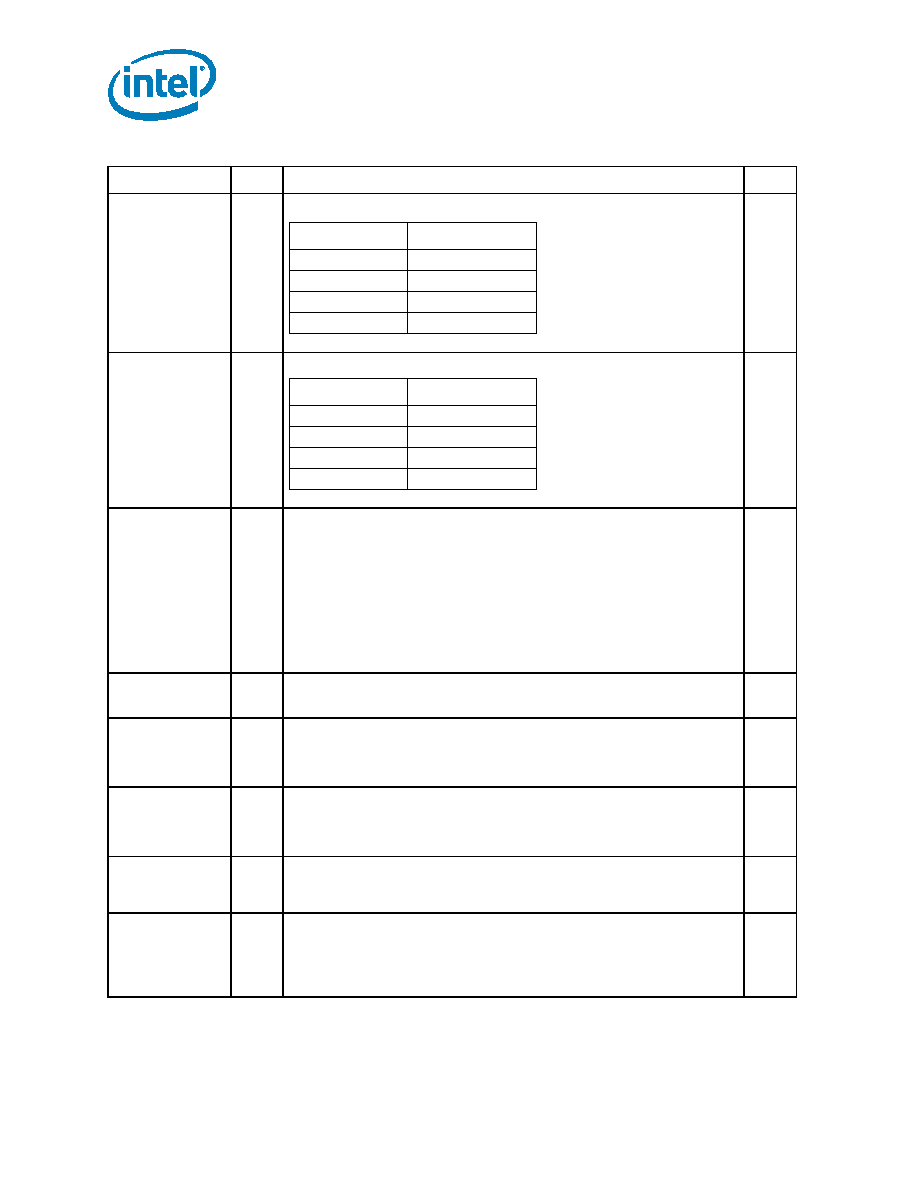

DSTBN[3:0]#

I/O

Data strobe used to latch in D[63:0]#.

3

DSTBP[3:0]#

I/O

Data strobe used to latch in D[63:0]#.

3

FERR#/PBE#

O

FERR#/PBE# (floating-point error/pending break event) is a multiplexed signal and

its meaning is qualified by STPCLK#. When STPCLK# is not asserted, FERR#/PBE#

indicates a floating-point error and will be asserted when the processor detects an

unmasked floating-point error. When STPCLK# is not asserted, FERR#/PBE# is

similar to the ERROR# signal on the Intel 387 coprocessor, and is included for

compatibility with systems using MS-DOS*-type floating-point error reporting. When

STPCLK# is asserted, an assertion of FERR#/PBE# indicates that the processor has a

pending break event waiting for service. The assertion of FERR#/PBE# indicates that

the processor should be returned to the Normal state. For additional information on

the pending break event functionality, including the identification of support of the

feature and enable/disable information, refer to Vol. 3 of the Intel Architecture

Software Developer’s Manual and the Intel Processor Identification and the CPUID

Instruction application note.

2

FORCEPR#

I

The FORCEPR# (force power reduction) input can be used by the platform to cause

the Dual-Core Intel Xeon Processor 5000 series to activate the Thermal Control

Circuit (TCC).

GTLREF_ADD_C0

GTLREF_ADD_C1

I

GTLREF_ADD_C0 and GTLREF_ADD_C1 determine the signal reference level for

AGTL+ address and common clock input lands on processor core 0 and processor

core 1 respectively. GTLREF_ADD is used by the AGTL+ receivers to determine if a

signal is a logical 0 or a logical 1. Please refer to the appropriate platform design

guidelines for additional details.

GTLREF_DATA_C0

GTLREF_DATA_C1

I

GTLREF_DATA_C0 AND GTLREF_DATA_C1 determine the signal reference level for

AGTL+ data input lands on processor core 0 and processor core 1 respectively.

GTLREF_DATA is used by the AGTL+ receivers to determine if a signal is a logical 0 or

a logical 1. Please refer to the appropriate platform design guidelines for additional

details.

HIT#

HITM#

I/O

HIT# (Snoop Hit) and HITM# (Hit Modified) convey transaction snoop operation

results. Any FSB agent may assert both HIT# and HITM# together to indicate that it

requires a snoop stall, which can be continued by reasserting HIT# and HITM#

together.

3

IERR#

O

IERR# (Internal Error) is asserted by a processor as the result of an internal error.

Assertion of IERR# is usually accompanied by a SHUTDOWN transaction on the

processor FSB. This transaction may optionally be converted to an external error

signal (for example, NMI) by system core logic. The processor will keep IERR#

asserted until the assertion of RESET#.

This signal does not have on-die termination.

2

Table 5-1.

Signal Definitions (Sheet 4 of 8)

Name

Type

Description

Notes

Signals

Associated Strobes

D[15:0]#, DBI0#

DSTBN0#

D[31:16]#, DBI1#

DSTBN1#

D[47:32]#, DBI2#

DSTBN2#

D[63:48]#, DBI3#

DSTBN3#

Signals

Associated Strobes

D[15:0]#, DBI0#

DSTBP0#

D[31:16]#, DBI1#

DSTBP1#

D[47:32]#, DBI2#

DSTBP2#

D[63:48]#, DBI3#

DSTBP3#

相关PDF资料 |

PDF描述 |

|---|---|

| BX80557E2140 | MICROPROCESSOR, PBGA775 |

| BXM80526B600128 | 64-BIT, 600 MHz, MICROPROCESSOR, PBGA495 |

| BXM80526B700128 | 64-BIT, 700 MHz, MICROPROCESSOR, CPGA495 |

| BXM80526B700 | 64-BIT, 700 MHz, MICROPROCESSOR, CPGA495 |

| BXM80536GC2100F | 32-BIT, 2100 MHz, MICROPROCESSOR, CPGA478 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| BX805555050A S L96C | 制造商:Intel 功能描述:XEON PROCESSOR 5050 |

| BX805555060A S L96A | 制造商:Intel 功能描述:MPU Xeon 65nm 3.2GHz 771-Pin FCLGA6 |

| BX805555060P S L96A | 制造商:Intel 功能描述:MPU Xeon 制造商:Intel 功能描述:MPU Xeon? Processor 5060 65nm 3.2GHz 771-Pin FCLGA6 |

| BX805565120P S L9RY | 制造商:Intel 功能描述:MPU Xeon 制造商:Intel 功能描述:MPU Xeon? Processor 5120 RISC 64-Bit 65nm 1.86GHz 771-Pin LGA Box |

| BX805565130A S LAGC | 制造商:Intel 功能描述:5100 MEMORY CONTROLLER HUB CHIPSET |

发布紧急采购,3分钟左右您将得到回复。