参数资料

| 型号: | CDB4245 |

| 厂商: | Cirrus Logic Inc |

| 文件页数: | 32/59页 |

| 文件大小: | 0K |

| 描述: | BOARD EVAL FOR CS4245 CODEC |

| 标准包装: | 1 |

| 主要目的: | 音频编解码器 |

| 嵌入式: | 是,FPGA / CPLD |

| 已用 IC / 零件: | CS4245 |

| 主要属性: | 4 个单端模拟和 1 个麦克风输入和 8 个输出,S/PDIF 发射器和接收器 |

| 次要属性: | 图形用户界面 |

| 已供物品: | 板 |

| 产品目录页面: | 754 (CN2011-ZH PDF) |

| 相关产品: | CS4245-DQZR-ND - IC CODEC AUD STER 104DB 48-LQFP 598-1616-ND - IC CODEC AUD STER 104DB 48LQFP 598-1034-ND - IC CODEC AUD STER 104DB 48LQFP |

| 其它名称: | 598-1501 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页当前第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页

�� �

�

�

�CS4245�

�4.2.3�

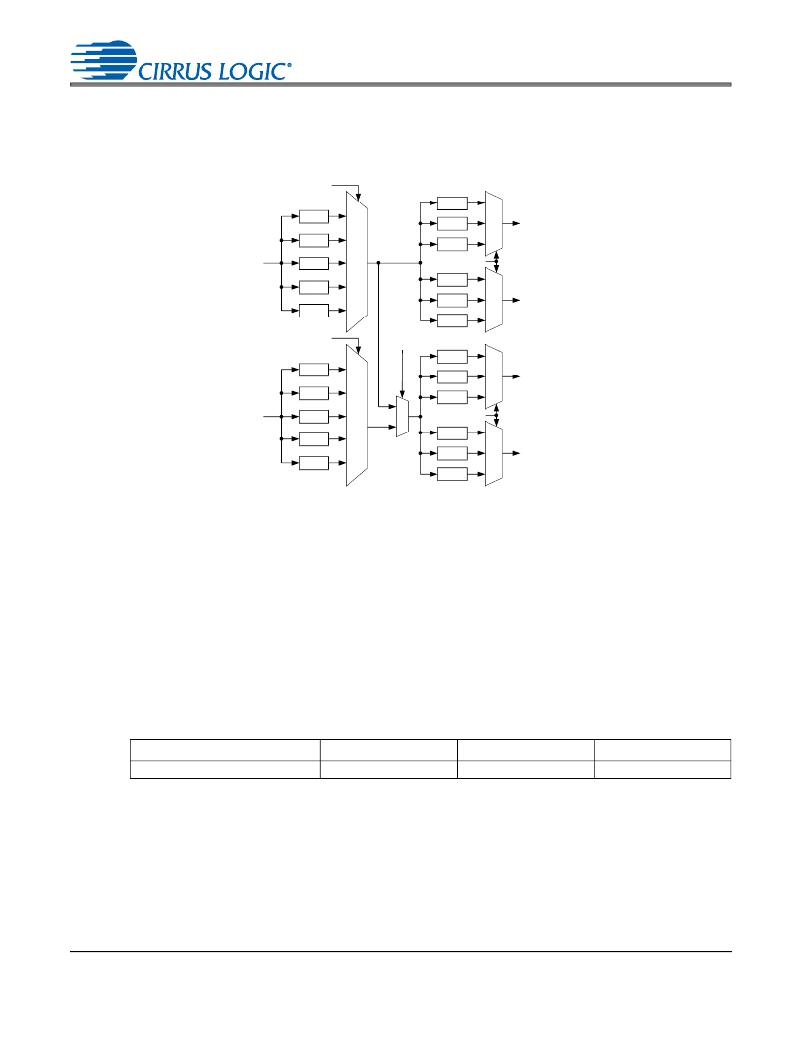

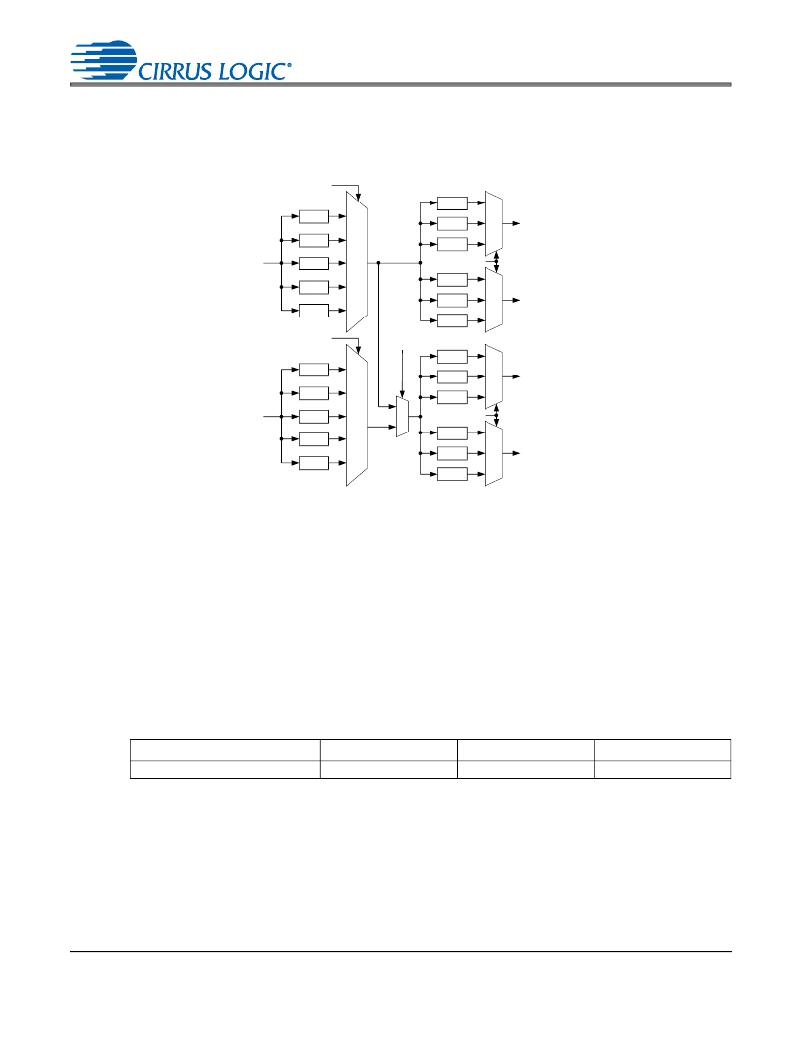

�Master� Mode�

�As� a� clock� master,� LRCK� and� SCLK� will� operate� as� outputs.� The� two� serial� ports� may� be� independently�

�placed� into� Master� or� Slave� mode.� Each� LRCK� and� SCLK� is� internally� derived� from� its� respective� MCLK�

��MCLK1� Freq� Bits�

�÷256�

�00�

�MCLK1�

�÷1�

�÷1.5�

�÷2�

�÷3�

�÷4�

�MCLK2� Freq� Bits�

�÷1�

�000�

�001�

�010�

�011�

�100�

�000�

�ASynch� Bit�

�÷128�

�÷64�

�ADC_FM� Bits�

�÷4�

�÷2�

�÷1�

�÷256�

�÷128�

�01�

�10�

�00�

�01�

�10�

�00�

�01�

�LRCK1�

�SCLK1�

�LRCK2�

�MCLK2�

�÷1.5�

�÷2�

�÷3�

�÷4�

�001�

�010�

�011�

�100�

�0�

�1�

�÷64�

�DAC_FM� Bits�

�÷4�

�÷2�

�10�

�00�

�01�

�SCLK2�

�÷1�

�10�

�Figure� 13.� Master� Mode� Clocking�

�4.2.4�

�Slave� Mode�

�In� Slave� Mode,� SCLK� and� LRCK� operate� as� inputs.� Each� serial� port� may� be� independently� placed� into�

�Slave� Mode.� The� Left/Right� clock� signal� must� be� equal� to� the� sample� rate,� Fs.� If� operating� in� Asynchro-�

�nous� Mode,� LRCK1� must� be� synchronously� derived� from� MCLK1� and� LRCK2� must� be� synchronously� de-�

�rived� from� MCLK2.� If� operating� in� Synchronous� Mode,� LRCK1,� and� LRCK2� must� be� synchronously�

�derived� from� MCLK1.� For� more� information� on� Synchronous� and� Asynchronous� Modes,� see� “Synchro-�

��For� each� serial� port,� the� serial� bit� clock� must� be� equal� to� 128x,� 64x,� 48x� or� 32x� Fs,� depending� on� the� de-�

�sired� speed� mode.� If� operating� in� Asynchronous� Mode,� the� serial� bit� clock� SCLK1� must� be� synchronously�

�derived� from� MCLK1� and� SCLK2� must� be� synchronously� derived� from� MCLK2.� If� operating� in� Synchro-�

�nous� Mode,� SCLK1,� and� SCLK2� must� be� synchronously� derived� from� MCLK1.� Refer� to� Table� 4� for� re-�

�quired� serial� bit� clock� to� Left/Right� clock� ratios.�

�Single-Speed�

�Double-Speed�

�Quad-Speed�

�SCLK/LRCK� Ratio�

�32x,� 48x,� 64x,� 128x�

�32x,� 48x,� 64x�

�32x,� 48x,� 64x�

�Table� 4.� Slave� Mode� Serial� Bit� Clock� Ratios�

�4.3�

�32�

�High-Pass� Filter� and� DC� Offset� Calibration�

�When� using� operational� amplifiers� in� the� input� circuitry� driving� the� CS4245,� a� small� DC� offset� may� be� driven�

�into� the� A/D� converter.� The� CS4245� includes� a� high-pass� filter� after� the� decimator� to� remove� any� DC� offset�

�which� could� result� in� recording� a� DC� level,� possibly� yielding� clicks� when� switching� between� devices� in� a� mul-�

�tichannel� system.�

�DS656F3�

�相关PDF资料 |

PDF描述 |

|---|---|

| CDB42L55 | BOARD EVAL FOR CS42L55 CODEC |

| CDB44L11 | EVALUATION BOARD FOR CS44L11 |

| CDB48500-USB | KIT USB EVALUATION FOR CDB48500 |

| CDB5378 | EVALUATION BOARD FOR CS5378 |

| CDB5460AU | EVALUATION BOARD FOR CS5460A |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CDB42518 | 功能描述:音频 IC 开发工具 Eval Bd RoHS:否 制造商:Texas Instruments 产品:Evaluation Kits 类型:Audio Amplifiers 工具用于评估:TAS5614L 工作电源电压:12 V to 38 V |

| CDB42528 | 功能描述:音频 IC 开发工具 Eval Bd RoHS:否 制造商:Texas Instruments 产品:Evaluation Kits 类型:Audio Amplifiers 工具用于评估:TAS5614L 工作电源电压:12 V to 38 V |

| CDB4265 | 功能描述:音频 IC 开发工具 Eval Bd 192kHz CODEC w/PGA & Input Mux RoHS:否 制造商:Texas Instruments 产品:Evaluation Kits 类型:Audio Amplifiers 工具用于评估:TAS5614L 工作电源电压:12 V to 38 V |

| CDB4270 | 功能描述:音频 IC 开发工具 Eval Bd 105dB 192kHz CODEC RoHS:否 制造商:Texas Instruments 产品:Evaluation Kits 类型:Audio Amplifiers 工具用于评估:TAS5614L 工作电源电压:12 V to 38 V |

| CDB4271 | 功能描述:音频 IC 开发工具 Eval Bd CS4271 RoHS:否 制造商:Texas Instruments 产品:Evaluation Kits 类型:Audio Amplifiers 工具用于评估:TAS5614L 工作电源电压:12 V to 38 V |

发布紧急采购,3分钟左右您将得到回复。