参数资料

| 型号: | CS61584A-IQ3Z |

| 厂商: | Cirrus Logic Inc |

| 文件页数: | 19/47页 |

| 文件大小: | 0K |

| 描述: | IC LINE INTERFACE T1/E1 64LQFP |

| 标准包装: | 160 |

| 接口: | 并行/串行 |

| 电源电压: | 3.3V,5V |

| 封装/外壳: | 64-LQFP |

| 供应商设备封装: | 64-LQFP(10x10) |

| 包装: | 托盘 |

| 安装类型: | 表面贴装 |

| 产品目录页面: | 759 (CN2011-ZH PDF) |

| 其它名称: | 598-1713 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页当前第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页

CS61584A

26

DS261PP5

AAO: The Automatic All-Ones (AAO) bit in the

Mask Register (Channel 1, bit 1) causes an un-

framed all-ones pattern to be output at the RPOS

and RNEG (or RDATA) pins when the receiver is

in a loss of signal (LOS) condition.

9.1.3

Control A Registers

The Control A registers are read-write registers and

are shown in Table 7. The Control A registers se-

lect device configuration and power down control.

CLKE: Establishes the edge of the of RCLK that

RPOS and RNEG (or RDATA) are valid.

PD: Controls per channel power down.

ATTEN0 and ATTEN1: Controls the jitter attenu-

ator location and -3 dB knee frequency (See Jitter

Attenuator section).

CODER: Controls the coder mode function. The

TPOS, TNEG, RPOS, and RNEG pins are active

when the transparent mode is enabled. The TDA-

TA, RDATA, AIS, and BPV pins are active when

the coder mode is enabled.

AMI-T: Controls the line encoder in the transmit

direction. The selection of B8ZS or HDB3 is deter-

mined by the CON[3:0] bits (See the Transmitter

section).

AMI-R: Controls the line decoder in the receive di-

rection. The selection of B8ZS or HDB3 is deter-

mined by the CON[3:0] bits (See the Transmitter

section).

EXZ: Controls the automatic detection of excessive

zeros on the BPV pin according to ANSI T1.231

when coder mode is enabled (CODERx = 1).

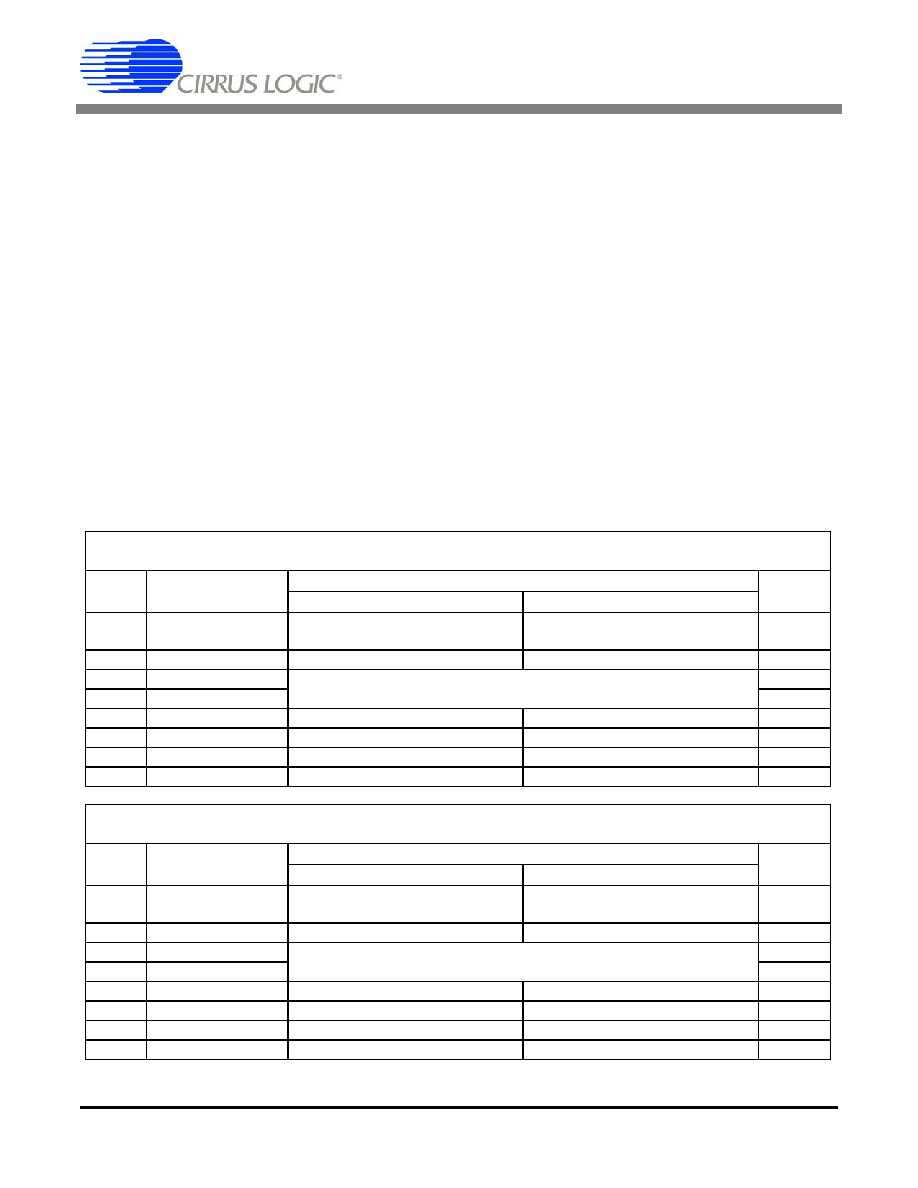

Control A Register (Channel 1)

Serial Port Address: 0x14; Parallel Port Address: 0xY4

Bit

Description

Definition

Reset

Value

10

7

CLKE

RPOS/RNEG (or RDATA) valid on

falling edge of RCLK

RPOS/RNEG (or RDATA) valid on

rising edge of RCLK

0

6

PD1

Power down channel

Power up channel

0

5

ATTEN01

Jitter attenuator location

(See Jitter Attenuator section)

0

4ATTEN11

0

3

CODER1

Coder mode enabled

Transparent mode enabled

0

2

AMI-T1

AMI encoder enabled

B8ZS/HDB3 encoder enabled

0

1

AMI-R1

AMI decoder enabled

B8ZS/HDB3 decoder enabled

0

Factory Test

Test

Normal operation

0

Control A Register (Channel 2)

Serial Port Address: 0x15; Parallel Port Address: 0xY5

Bit

Description

Definition

Reset

Value

10

7

EXZ

Excessive zeros detection for both

channels enabled

Excessive zeros detection for both

channels disabled

0

6

PD2

Power down channel

Power up channel

0

5

ATTEN02

Jitter attenuator location

(See Jitter Attenuator section)

0

4ATTEN12

0

3

CODER2

Coder mode enabled

Transparent mode enabled

0

2

AMI-T2

AMI encoder enabled

B8ZS/HDB3 encoder enabled

0

1

AMI-R2

AMI decoder enabled

B8ZS/HDB3 decoder enabled

0

Factory Test

Test

Normal operation

0

Table 7. Control A Registers

CS61584A

26

DS261F1

相关PDF资料 |

PDF描述 |

|---|---|

| CS61884-IRZ | IC LN INTERF T1/E1/J1 160-LFBGA |

| CS8130-CS | IC IR TRANSCEIVER 2-5V 20-SSOP |

| CS8190EDWF20G | IC TACH/SPEEDO DRVR PREC 20SOICW |

| CS8191XNF16 | IC DRVR AIRCORE TACH/SPEED 16DIP |

| CS82C5296 | IC UART/BRG 5V 16MHZ 28-PLCC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CS61584A-IQ3ZR | 功能描述:网络控制器与处理器 IC IC 3.3V/5V Dul T1/E1 Line Intrfc Unit RoHS:否 制造商:Micrel 产品:Controller Area Network (CAN) 收发器数量: 数据速率: 电源电流(最大值):595 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:PBGA-400 封装:Tray |

| CS61584A-IQ5 | 功能描述:网络控制器与处理器 IC IC 3.3V/5V Dual T1/ E1 Line Intrfc Unit RoHS:否 制造商:Micrel 产品:Controller Area Network (CAN) 收发器数量: 数据速率: 电源电流(最大值):595 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:PBGA-400 封装:Tray |

| CS61584A-IQ5Z | 功能描述:网络控制器与处理器 IC IC 3.3V/5V Dual T1/ E1 Line Intrfc Unit RoHS:否 制造商:Micrel 产品:Controller Area Network (CAN) 收发器数量: 数据速率: 电源电流(最大值):595 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:PBGA-400 封装:Tray |

| CS61584A-IQ5ZR | 功能描述:网络控制器与处理器 IC IC 3.3V/5V Dul T1/E1 Line Intrfc Unit RoHS:否 制造商:Micrel 产品:Controller Area Network (CAN) 收发器数量: 数据速率: 电源电流(最大值):595 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:PBGA-400 封装:Tray |

| CS61584-IL3 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Line Interface |

发布紧急采购,3分钟左右您将得到回复。