参数资料

| 型号: | CS61584A-IQ3Z |

| 厂商: | Cirrus Logic Inc |

| 文件页数: | 26/47页 |

| 文件大小: | 0K |

| 描述: | IC LINE INTERFACE T1/E1 64LQFP |

| 标准包装: | 160 |

| 接口: | 并行/串行 |

| 电源电压: | 3.3V,5V |

| 封装/外壳: | 64-LQFP |

| 供应商设备封装: | 64-LQFP(10x10) |

| 包装: | 托盘 |

| 安装类型: | 表面贴装 |

| 产品目录页面: | 759 (CN2011-ZH PDF) |

| 其它名称: | 598-1713 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页当前第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页

CS61584A

32

DS261PP5

10.1

JTAG Data Registers (DR)

The test data registers are the Boundary-Scan Reg-

ister (BSR), the Device Identification Register

(DIR), and the Bypass Register (BR).

Boundary Scan Register: The BSR is connected in

parallel to all the digital I/O pins, and provides the

mechanism for applying/reading test patterns

to/from the board traces. The BSR is 62 bits long

and is initialized and read using the instruction

SAMPLE/PRELOAD. The bit ordering for the

BSR is the same as the top-view package pin out,

beginning with the LOS1 pin and moving counter-

clockwise to end with the PD1 pin as shown in Ta-

ble 10. Note that the analog, oscillator, power,

ground, CLKE/IPOL, and MODE pins are not in-

cluded as part of the boundary-scan register.

The input pins require one bit in the BSR and only

one J-TCK cycle is required to load test data for

each input pin.

The output pins have two bits in the BSR to define

output high, output low, or high impedance. The

first bit (shifted in first) selects between an output-

enabled state (bit set to 1) or high-impedance state

(bit set to 0). The second bit shifted in contains the

test data that may be output on the pin. Therefore,

two J-TCK cycles are required to load test data for

each output pin.

The bi-directional pins have three bits in the BSR

to define input, output high, output low, or high im-

pedance. The first bit shifted into the BSR config-

ures the output driver as high-impedance (bit set to

0) or active (bit set to 1). The second bit shifted into

the BSR sets the output value when the first bit is 1.

The third bit captures the value of the pin. This pin

may have its value set externally as an input (if the

first bit is 0) or set internally as an output (if the

first bit is 1). To configure a pad as an input, the J-

TDI pattern is 0X0. To configure a pad as an out-

put, the J-TDI pattern is 1X1. Therefore, three J-

TCK cycles are required to load test data for each

bi-directional pin.

When JTAG testing is conducted in Host mode, the

polarity of the INT pin is determined by the state of

the IPOL pin. The JTAG BSR should configure the

INT pin as an input in Hardware mode and as an

output in Host mode.

Device Identification Register: The DIR provides

the manufacturer, part number, and version of the

CS61584A. This information can be used to verify

that the proper version or revision number has been

used in the system under test. The DIR is 32 bits

long and is partitioned as shown in Table 11. Data

from the DIR is shifted out to J-TDO LSB first.

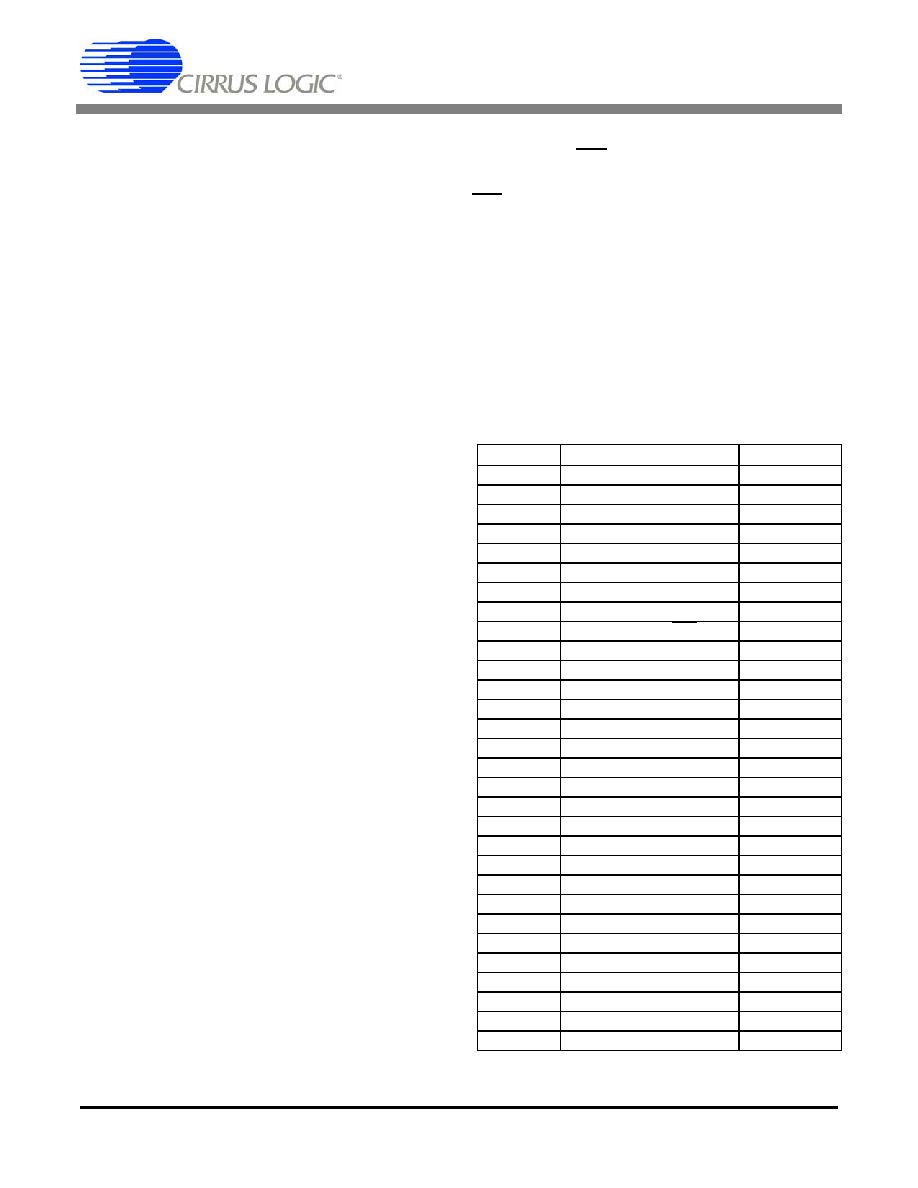

BSR Bits

Pin Name

Pad Type

0 - 2

LOS1, SAD6

bi-directional

3 - 5

TNEG1, AIS1

bi-directional

6

TPOS1, TDATA1

input

7TCLK1

input

8 - 9

RNEG1, BPV1

output

10 - 11

RPOS1, RDATA1

output

12 - 13

RCLK1

output

14

ATTEN1, CS

input

15 - 17

RLOOP1, INT

bi-directional

18

RLOOP2, SCLK, RD(DS)

input

19 - 21

LLOOP, SDO, AD0

bi-directional

22 - 24

TAOS1, SDI, AD1

bi-directional

25 - 27

TAOS2, SPOL, AD2

bi-directional

28 - 30

CON01, AD3

bi-directional

31 - 33

CON02, AD4

bi-directional

34 - 36

CON11, AD5

bi-directional

37 - 39

CON12, AD6

bi-directional

40 - 42

CON21, AD7

bi-directional

43

CON22, ALE(AS)

input

44

CON31, WR(R/W)

input

45 - 46

RCLK2

output

47 - 48

RPOS2, RDATA2

output

49 - 50

RNEG2, BPV2

output

51

TCLK2

input

52

TPOS2, TDATA2

input

53 - 55

TNEG2, AIS2

bi-directional

56 - 58

LOS2, SAD7

bi-directional

59

CON32, BTS

input

60

PD2, SAD5

input

61

PD1, SAD4

input

Table 10. Boundary Scan Register

CS61584A

32

DS261F1

相关PDF资料 |

PDF描述 |

|---|---|

| CS61884-IRZ | IC LN INTERF T1/E1/J1 160-LFBGA |

| CS8130-CS | IC IR TRANSCEIVER 2-5V 20-SSOP |

| CS8190EDWF20G | IC TACH/SPEEDO DRVR PREC 20SOICW |

| CS8191XNF16 | IC DRVR AIRCORE TACH/SPEED 16DIP |

| CS82C5296 | IC UART/BRG 5V 16MHZ 28-PLCC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CS61584A-IQ3ZR | 功能描述:网络控制器与处理器 IC IC 3.3V/5V Dul T1/E1 Line Intrfc Unit RoHS:否 制造商:Micrel 产品:Controller Area Network (CAN) 收发器数量: 数据速率: 电源电流(最大值):595 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:PBGA-400 封装:Tray |

| CS61584A-IQ5 | 功能描述:网络控制器与处理器 IC IC 3.3V/5V Dual T1/ E1 Line Intrfc Unit RoHS:否 制造商:Micrel 产品:Controller Area Network (CAN) 收发器数量: 数据速率: 电源电流(最大值):595 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:PBGA-400 封装:Tray |

| CS61584A-IQ5Z | 功能描述:网络控制器与处理器 IC IC 3.3V/5V Dual T1/ E1 Line Intrfc Unit RoHS:否 制造商:Micrel 产品:Controller Area Network (CAN) 收发器数量: 数据速率: 电源电流(最大值):595 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:PBGA-400 封装:Tray |

| CS61584A-IQ5ZR | 功能描述:网络控制器与处理器 IC IC 3.3V/5V Dul T1/E1 Line Intrfc Unit RoHS:否 制造商:Micrel 产品:Controller Area Network (CAN) 收发器数量: 数据速率: 电源电流(最大值):595 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:PBGA-400 封装:Tray |

| CS61584-IL3 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Line Interface |

发布紧急采购,3分钟左右您将得到回复。