- 您现在的位置:买卖IC网 > PDF目录170654 > DAC5687IPZPG4 (TEXAS INSTRUMENTS INC) PARALLEL, WORD INPUT LOADING, 0.0104 us SETTLING TIME, 16-BIT DAC, PQFP100 PDF资料下载

参数资料

| 型号: | DAC5687IPZPG4 |

| 厂商: | TEXAS INSTRUMENTS INC |

| 元件分类: | DAC |

| 英文描述: | PARALLEL, WORD INPUT LOADING, 0.0104 us SETTLING TIME, 16-BIT DAC, PQFP100 |

| 封装: | GREEN, PLASTIC, HTQFP-100 |

| 文件页数: | 18/79页 |

| 文件大小: | 2490K |

| 代理商: | DAC5687IPZPG4 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页当前第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页

www.ti.com

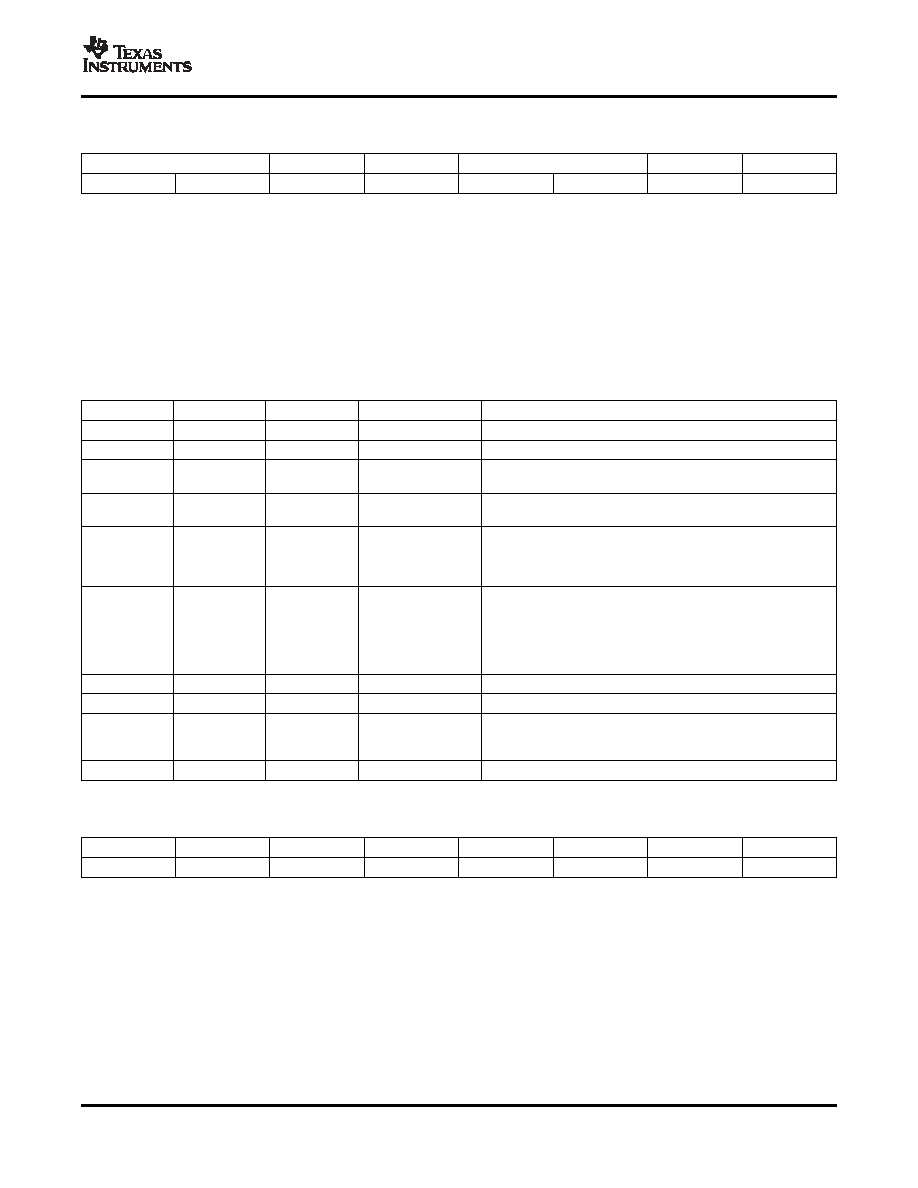

Register Name: CONFIG0—Address: 0x01, Default = 0x00

Register Name: CONFIG1—Address: 0x02, Default = 0x00

SLWS164E – FEBRUARY 2005 – REVISED SEPTEMBER 2006

BIT 7

BIT 0

pll_div(1:0)

pll_freq

pll_kv

interp(1:0)

inv_plllock

fifo_bypass

0

pll_div(1:0): PLL VCO divider; {00 = 1, 01 = 2, 10 = 4, 11 = 8}.

pll_freq: PLL VCO center frequency; {0 = low center frequency, 1 = high center frequency}.

pll_kv: PLL VCO gain; {0 = high gain, 1 = low gain}.

interp(1:0): FIR interpolation; {00 = X2, 01 = X4, 10 = X4L, 11 = X8}. X4 uses lower power than X4L, but fDAC =

320 MHz maximum when NCO or QMC is used.

inv_plllock: Multifunction bit, depending on clock mode

fifo_bypass: When set, the internal four-sample FIFO is disabled. When cleared, the FIFO is enabled.

Table 2. inv_plllock Bit Modes

PLLVDD

dual_clk

inv_plllock

fifo_bypass

DESCRIPTION

0 V

0

1

Input data latched on PLLLOCK pin rising edges, FIFO disabled

0 V

0

1

Input data latched on PLLLOCK pin falling edges, FIFO disabled

0 V

0

Input data latched on PLLLOCK pin rising edges, FIFO enabled

and must be synchronized

0 V

0

1

0

Input data latched on PLLLOCK pin falling edges, FIFO enabled

and must be synchronized

0 V

1

0

1

Input data latched on CLK1/CLK1C differential input. Timing

between CLK1 and CLK2 rising edges must be tightly controlled

(500 ps maximum at 500-MHz CLK2). PLLLOCK output signal is

always low. The FIFO is always disabled in this mode.

0 V

1

0

Input data latched on CLK1/CLK1C differential input. No phase

relationship required between CLK1 and CLK2. The FIFO is

employed to manage the internal handoff between the CLK1

input clock and the CLK2 derived output clock; the FIFO must

be synchronized. The PLLLOCK output signal reflects the

internally generated FIFO output clock.

0 V

1

0

Not a valid setting. Do not use.

0 V

1

Not a valid setting. Do not use.

3.3 V

X

1

Internal PLL enabled, CLK1/CLK1C input differential clock is

used to latch the input data. The FIFO is always disabled in this

mode.

3.3 V

X

0

Not a valid setting. Do not use.

BIT 7

BIT 0

qflag

interl

dual_clk

twos

rev_abus

rev_bbus

fir_bypass

full_bypass

0

qflag: When set, the QFLAG input pin operates as a B sample indicator when interleaved data is enabled. When

cleared, the TXENABLE rising determines the A/B timing relationship.

interl: When set, interleaved input data mode is enabled; both A and B data streams are input at the DA[15:0]

input pins.

dual_clk: Only used when the PLL is disabled. When set, two differential clocks are used to input the data to the

chip; CLK1/CLK1C is used to latch the input data into the chip and CLK2/CLK2C is used as the DAC

sample clock.

twos: When set, input data is interpreted as 2s complement. When cleared, input data is interpreted as offset

binary.

rev_abus: When cleared, DA input data MSB to LSB order is DA[15] = MSB and DA[0] = LSB. When set, DA

Copyright 2005–2006, Texas Instruments Incorporated

25

Product Folder Link(s): DAC5687

相关PDF资料 |

PDF描述 |

|---|---|

| DAC5688IRGCTG4 | PARALLEL, WORD INPUT LOADING, 0.0104 us SETTLING TIME, 16-BIT DAC, PQCC64 |

| DAC702LH | PARALLEL, WORD INPUT LOADING, 4 us SETTLING TIME, 16-BIT DAC, CDIP24 |

| DAC7545KUG4 | PARALLEL, WORD INPUT LOADING, 2 us SETTLING TIME, 12-BIT DAC, PDSO20 |

| DAC7545JP | PARALLEL, WORD INPUT LOADING, 2 us SETTLING TIME, 12-BIT DAC, PDIP20 |

| DAC7545KP | PARALLEL, WORD INPUT LOADING, 2 us SETTLING TIME, 12-BIT DAC, PDIP20 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| DAC5687IPZPR | 功能描述:数模转换器- DAC 16-bit 500 MSPS 2-8x Interpolat’g Dual-Ch RoHS:否 制造商:Texas Instruments 转换器数量:1 DAC 输出端数量:1 转换速率:2 MSPs 分辨率:16 bit 接口类型:QSPI, SPI, Serial (3-Wire, Microwire) 稳定时间:1 us 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-14 封装:Tube |

| DAC5687IPZPRG4 | 功能描述:数模转换器- DAC 16-bit 500 MSPS 2-8x Interpolat’g Dual-Ch RoHS:否 制造商:Texas Instruments 转换器数量:1 DAC 输出端数量:1 转换速率:2 MSPs 分辨率:16 bit 接口类型:QSPI, SPI, Serial (3-Wire, Microwire) 稳定时间:1 us 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-14 封装:Tube |

| DAC5687MPZPEP | 功能描述:数模转换器- DAC 16B 500Msps 2X-8X Interp 2-Channel DAC RoHS:否 制造商:Texas Instruments 转换器数量:1 DAC 输出端数量:1 转换速率:2 MSPs 分辨率:16 bit 接口类型:QSPI, SPI, Serial (3-Wire, Microwire) 稳定时间:1 us 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-14 封装:Tube |

| DAC5688 | 制造商:TI 制造商全称:Texas Instruments 功能描述:DUAL-CHANNEL, 16-BIT, 800 MSPS, 2x-8x INTERPOLATING DIGITAL-TO-ANALOG CONVERTER (DAC) |

| DAC5688_10 | 制造商:TI 制造商全称:Texas Instruments 功能描述:DUAL-CHANNEL, 16-BIT, 800 MSPS, 2x-8x INTERPOLATING DIGITAL-TO-ANALOG CONVERTER (DAC) |

发布紧急采购,3分钟左右您将得到回复。