- 您现在的位置:买卖IC网 > PDF目录170654 > DAC5687IPZPG4 (TEXAS INSTRUMENTS INC) PARALLEL, WORD INPUT LOADING, 0.0104 us SETTLING TIME, 16-BIT DAC, PQFP100 PDF资料下载

参数资料

| 型号: | DAC5687IPZPG4 |

| 厂商: | TEXAS INSTRUMENTS INC |

| 元件分类: | DAC |

| 英文描述: | PARALLEL, WORD INPUT LOADING, 0.0104 us SETTLING TIME, 16-BIT DAC, PQFP100 |

| 封装: | GREEN, PLASTIC, HTQFP-100 |

| 文件页数: | 37/79页 |

| 文件大小: | 2490K |

| 代理商: | DAC5687IPZPG4 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页当前第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页

www.ti.com

CLK1

DA[15:0]

DB[15:0]

ts(DATA)

th(DATA)

A0

A1

A2

AN

AN+1

A3

B0

B1

B2

BN

BN+1

B3

T0039-01

B0053-09

CLK

Buffer

CLK

Buffer

PFD

Charge

Pump

VCO

/1

/2

/4

/8

00

01

10

11

1

0

/2

Data

Latch

1 2

1

0

00

01

10

11

/2

0

1

CLK1

CLK1C

CLK2

LPF

pll_div(1:0)

PLLVDD

PLLLOCK

PLLVDD

DA[15:0]

DB[15:0]

interl

interp(1:0)

f

DAC

f

/2X2

DAC

f

/4

DAC

X4

f

/4

DAC

X4L

f

/8

DAC

X8

Data

Lock

CLK2C

SLWS164E – FEBRUARY 2005 – REVISED SEPTEMBER 2006

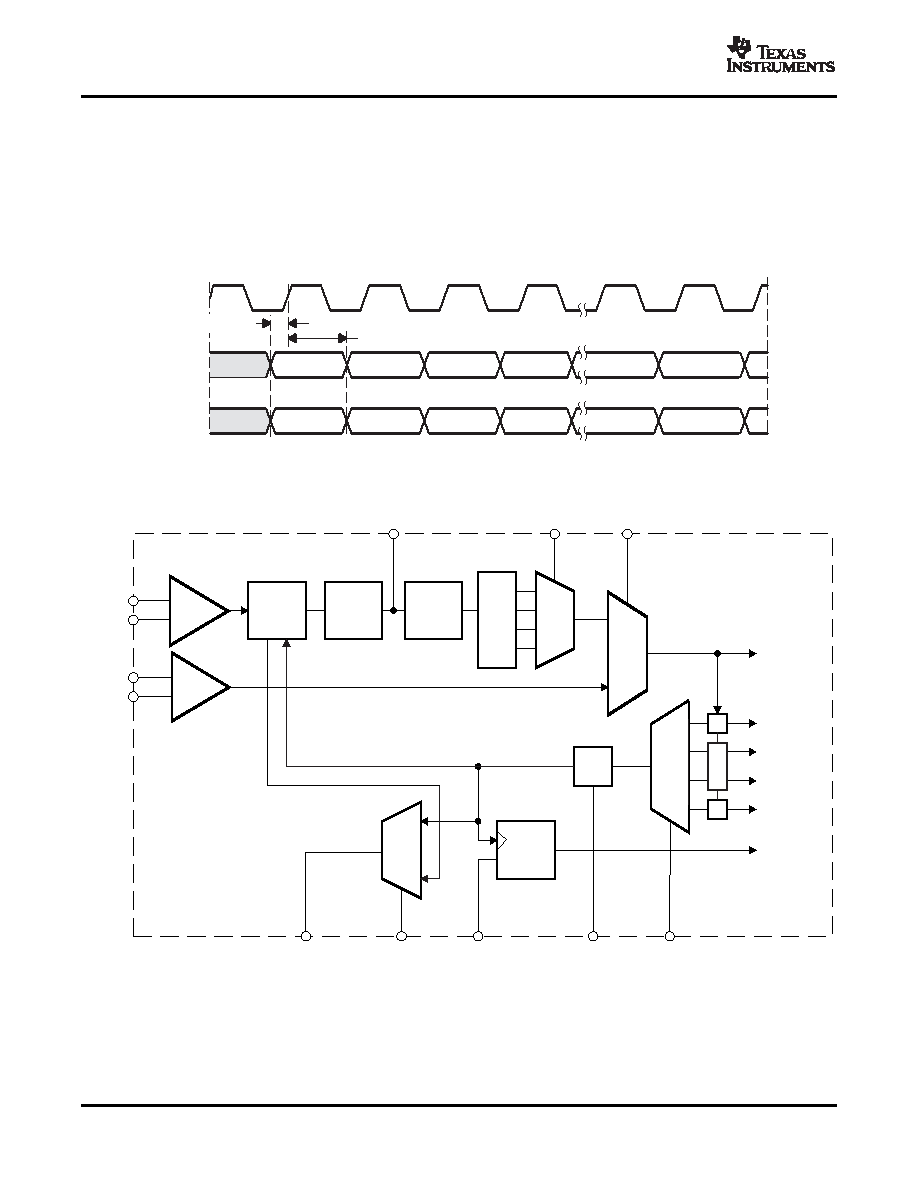

A type-four phase-frequency detector (PFD) in the internal PLL compares this reference clock to a feedback

clock and drives the PLL to maintain synchronization between the two clocks. The feedback clock is generated

by dividing the VCO output by 1

×, 2×, 4×, or 8× as selected by the prescaler div(1:0). The output of the prescaler

is the DAC sample rate clock and is divided down to generate clocks at

÷2, ÷4, and ÷8. The feedback clock is

selected by the registers sel(1:0), which is fed back to the PFD for synchronization to the input clock. The

feedback clock is also used for the data input rate, so the ratio of DAC output clock to feedback clock sets the

interpolation rate of the DAC5687. The PLLLOCK pin is an output indicating when the PLL has achieved lock. An

external RC low-pass PLL filter is provided by the user at pin LPF. See the Low-Pass Filter section for

filter-setting calculations. This is the only mode where the LPF filter applies.

Figure 45. Dual-Bus Mode Timing Diagram (PLL Mode)

Figure 46. Clock Generation Architecture in PLL Mode

42

Copyright 2005–2006, Texas Instruments Incorporated

Product Folder Link(s): DAC5687

相关PDF资料 |

PDF描述 |

|---|---|

| DAC5688IRGCTG4 | PARALLEL, WORD INPUT LOADING, 0.0104 us SETTLING TIME, 16-BIT DAC, PQCC64 |

| DAC702LH | PARALLEL, WORD INPUT LOADING, 4 us SETTLING TIME, 16-BIT DAC, CDIP24 |

| DAC7545KUG4 | PARALLEL, WORD INPUT LOADING, 2 us SETTLING TIME, 12-BIT DAC, PDSO20 |

| DAC7545JP | PARALLEL, WORD INPUT LOADING, 2 us SETTLING TIME, 12-BIT DAC, PDIP20 |

| DAC7545KP | PARALLEL, WORD INPUT LOADING, 2 us SETTLING TIME, 12-BIT DAC, PDIP20 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| DAC5687IPZPR | 功能描述:数模转换器- DAC 16-bit 500 MSPS 2-8x Interpolat’g Dual-Ch RoHS:否 制造商:Texas Instruments 转换器数量:1 DAC 输出端数量:1 转换速率:2 MSPs 分辨率:16 bit 接口类型:QSPI, SPI, Serial (3-Wire, Microwire) 稳定时间:1 us 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-14 封装:Tube |

| DAC5687IPZPRG4 | 功能描述:数模转换器- DAC 16-bit 500 MSPS 2-8x Interpolat’g Dual-Ch RoHS:否 制造商:Texas Instruments 转换器数量:1 DAC 输出端数量:1 转换速率:2 MSPs 分辨率:16 bit 接口类型:QSPI, SPI, Serial (3-Wire, Microwire) 稳定时间:1 us 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-14 封装:Tube |

| DAC5687MPZPEP | 功能描述:数模转换器- DAC 16B 500Msps 2X-8X Interp 2-Channel DAC RoHS:否 制造商:Texas Instruments 转换器数量:1 DAC 输出端数量:1 转换速率:2 MSPs 分辨率:16 bit 接口类型:QSPI, SPI, Serial (3-Wire, Microwire) 稳定时间:1 us 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-14 封装:Tube |

| DAC5688 | 制造商:TI 制造商全称:Texas Instruments 功能描述:DUAL-CHANNEL, 16-BIT, 800 MSPS, 2x-8x INTERPOLATING DIGITAL-TO-ANALOG CONVERTER (DAC) |

| DAC5688_10 | 制造商:TI 制造商全称:Texas Instruments 功能描述:DUAL-CHANNEL, 16-BIT, 800 MSPS, 2x-8x INTERPOLATING DIGITAL-TO-ANALOG CONVERTER (DAC) |

发布紧急采购,3分钟左右您将得到回复。