- 您现在的位置:买卖IC网 > PDF目录170654 > DAC5687IPZPG4 (TEXAS INSTRUMENTS INC) PARALLEL, WORD INPUT LOADING, 0.0104 us SETTLING TIME, 16-BIT DAC, PQFP100 PDF资料下载

参数资料

| 型号: | DAC5687IPZPG4 |

| 厂商: | TEXAS INSTRUMENTS INC |

| 元件分类: | DAC |

| 英文描述: | PARALLEL, WORD INPUT LOADING, 0.0104 us SETTLING TIME, 16-BIT DAC, PQFP100 |

| 封装: | GREEN, PLASTIC, HTQFP-100 |

| 文件页数: | 53/79页 |

| 文件大小: | 2490K |

| 代理商: | DAC5687IPZPG4 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页当前第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页

www.ti.com

Power-Up Sequence

Sleep Mode

APPLICATION INFORMATION

Designing the PLL Loop Filter

SLWS164E – FEBRUARY 2005 – REVISED SEPTEMBER 2006

In all conditions, bring up DVDD first. If PLLVDD is powered (PLL on), CLKVDD should be powered before or

simultaneously with PLLVDD. AVDD, CLKVDD, and IOVDD can be powered simultaneously or in any order.

Within AVDD, the multiple AVDD pins should be powered simultaneously.

There are no specific requirements on the ramp rate for the supplies.

The DAC5687 features a power-down mode that turns off the output current and reduces the supply current to

less than 5 mA over the supply range of 3 V to 3.6 V and temperature range. The power-down mode is activated

by applying a logic level 1 to the SLEEP pin (e.g., by connecting pin SLEEP to AVDD). An internal pulldown

circuit at node SLEEP ensures that the DAC5687 is enabled if the input is left disconnected. Power-up and

power-down activation times depend on the value of external capacitor at node EXTIO. For a nominal capacitor

value of 0.1

F, power down takes less than 5 s and approximately 3 ms to power back up.

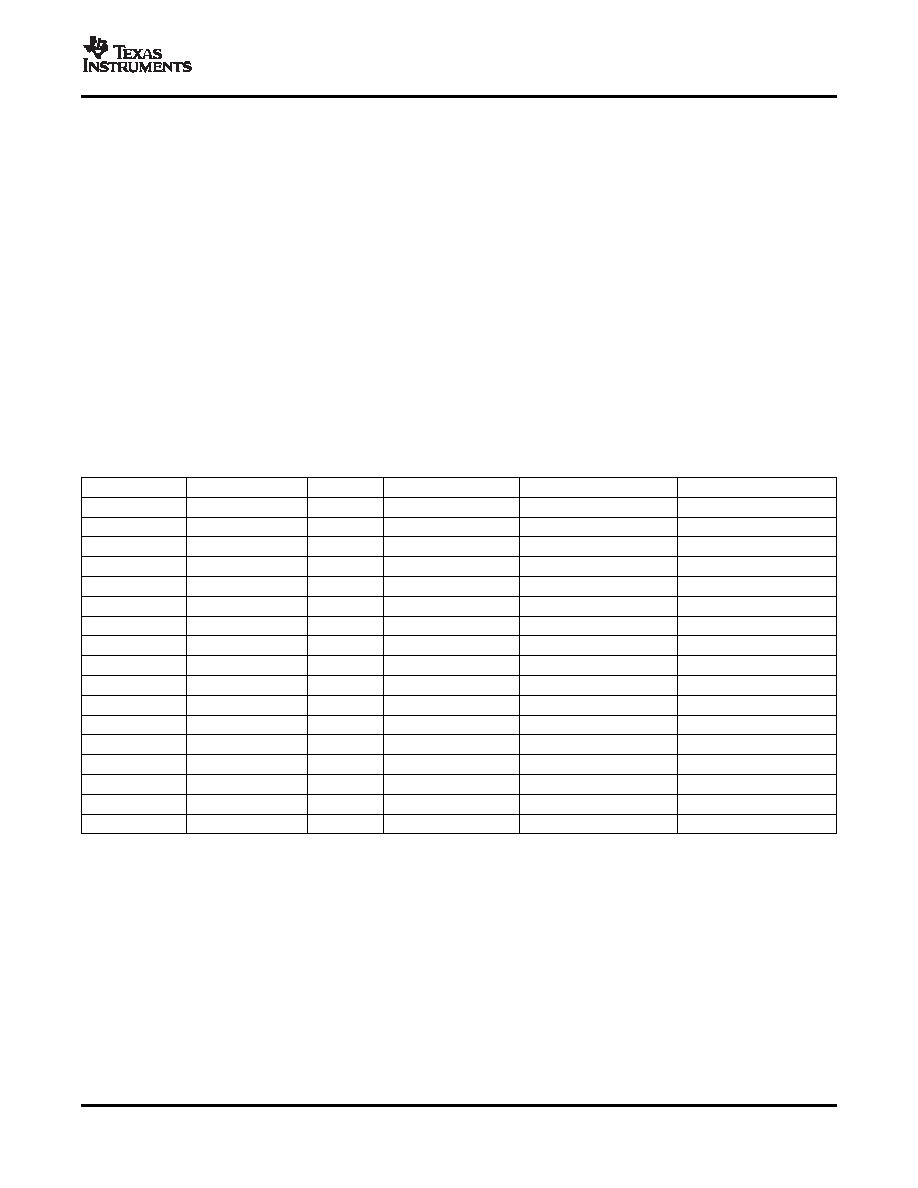

Table 15. Optimum DAC5687 PLL Settings

fDAC (MHz)

pll_freq

pll_kv

pll_div(1:0)

fVCO/fDAC

Estimated GVCO (MHz/V)

25 to 28.125

0

11

8

380

28.125 to 46.25

0

1

11

8

250

46.25 to 60

0

11

8

300

60 to 61.875

1

11

8

130

61.875 to 65

1

0

11

8

225

65 to 92.5

0

1

10

4

250

92.5 to 120

0

10

4

300

120 to 123.75

1

10

4

130

123.75 to 130

1

0

10

4

225

130 to 185

0

1

01

2

250

185 to 240

0

01

2

300

240 to 247.5

1

01

2

130

247.5 to 260

1

0

01

2

225

260 to 370

0

1

00

1

250

370 to 480

0

00

1

300

480 to 495

1

00

1

130

495 to 520

1

0

00

1

225

The optimized DAC5687 PLL settings based on the VCO frequency MIN and MAX values (see the digital

specifications) as a function of fDAC are listed in Table 15. To minimize phase noise at a given fDAC, pll_freq,

pll_kv, and pll_div have been chosen so GVCO is minimized and within the MIN and MAX frequency for a given

setting.

For example, if fDAC = 245.76 MHz, pll_freq is set to 1, pll_kv is set to 0 and pll_div(1:0) is set to 01 (divide

by 2) to lock the VCO at 491.52 MHz.

The external loop filter components C1, C2, and R1 are set by the GVCO, N = fVCO/fDATA = fVCO ×

Interpolation/fDAC, the loop phase margin φd and the loop bandwidth ωd. Except for applications where abrupt

clock frequency changes require a fast PLL lock time, it is suggested that

φ

d be set to at least 80 degrees for

stable locking and suppression of the phase-noise side lobes. Phase margins of 60 degrees or less can be

sensitive to board layout and decoupling details.

C1, C2, and R1 are then calculated by the following equations

Copyright 2005–2006, Texas Instruments Incorporated

57

Product Folder Link(s): DAC5687

相关PDF资料 |

PDF描述 |

|---|---|

| DAC5688IRGCTG4 | PARALLEL, WORD INPUT LOADING, 0.0104 us SETTLING TIME, 16-BIT DAC, PQCC64 |

| DAC702LH | PARALLEL, WORD INPUT LOADING, 4 us SETTLING TIME, 16-BIT DAC, CDIP24 |

| DAC7545KUG4 | PARALLEL, WORD INPUT LOADING, 2 us SETTLING TIME, 12-BIT DAC, PDSO20 |

| DAC7545JP | PARALLEL, WORD INPUT LOADING, 2 us SETTLING TIME, 12-BIT DAC, PDIP20 |

| DAC7545KP | PARALLEL, WORD INPUT LOADING, 2 us SETTLING TIME, 12-BIT DAC, PDIP20 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| DAC5687IPZPR | 功能描述:数模转换器- DAC 16-bit 500 MSPS 2-8x Interpolat’g Dual-Ch RoHS:否 制造商:Texas Instruments 转换器数量:1 DAC 输出端数量:1 转换速率:2 MSPs 分辨率:16 bit 接口类型:QSPI, SPI, Serial (3-Wire, Microwire) 稳定时间:1 us 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-14 封装:Tube |

| DAC5687IPZPRG4 | 功能描述:数模转换器- DAC 16-bit 500 MSPS 2-8x Interpolat’g Dual-Ch RoHS:否 制造商:Texas Instruments 转换器数量:1 DAC 输出端数量:1 转换速率:2 MSPs 分辨率:16 bit 接口类型:QSPI, SPI, Serial (3-Wire, Microwire) 稳定时间:1 us 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-14 封装:Tube |

| DAC5687MPZPEP | 功能描述:数模转换器- DAC 16B 500Msps 2X-8X Interp 2-Channel DAC RoHS:否 制造商:Texas Instruments 转换器数量:1 DAC 输出端数量:1 转换速率:2 MSPs 分辨率:16 bit 接口类型:QSPI, SPI, Serial (3-Wire, Microwire) 稳定时间:1 us 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-14 封装:Tube |

| DAC5688 | 制造商:TI 制造商全称:Texas Instruments 功能描述:DUAL-CHANNEL, 16-BIT, 800 MSPS, 2x-8x INTERPOLATING DIGITAL-TO-ANALOG CONVERTER (DAC) |

| DAC5688_10 | 制造商:TI 制造商全称:Texas Instruments 功能描述:DUAL-CHANNEL, 16-BIT, 800 MSPS, 2x-8x INTERPOLATING DIGITAL-TO-ANALOG CONVERTER (DAC) |

发布紧急采购,3分钟左右您将得到回复。