- 您现在的位置:买卖IC网 > PDF目录16264 > DS21Q59DK (Maxim Integrated Products)KIT DESIGN FOR DS21Q59 PDF资料下载

参数资料

| 型号: | DS21Q59DK |

| 厂商: | Maxim Integrated Products |

| 文件页数: | 21/76页 |

| 文件大小: | 0K |

| 描述: | KIT DESIGN FOR DS21Q59 |

| 产品培训模块: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 标准包装: | 1 |

| 主要目的: | 电信,调帧器和线路接口装置(LIU) |

| 已用 IC / 零件: | DS21Q59 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页当前第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页

DS21Q59 Quad E1 Transceiver

28 of 76

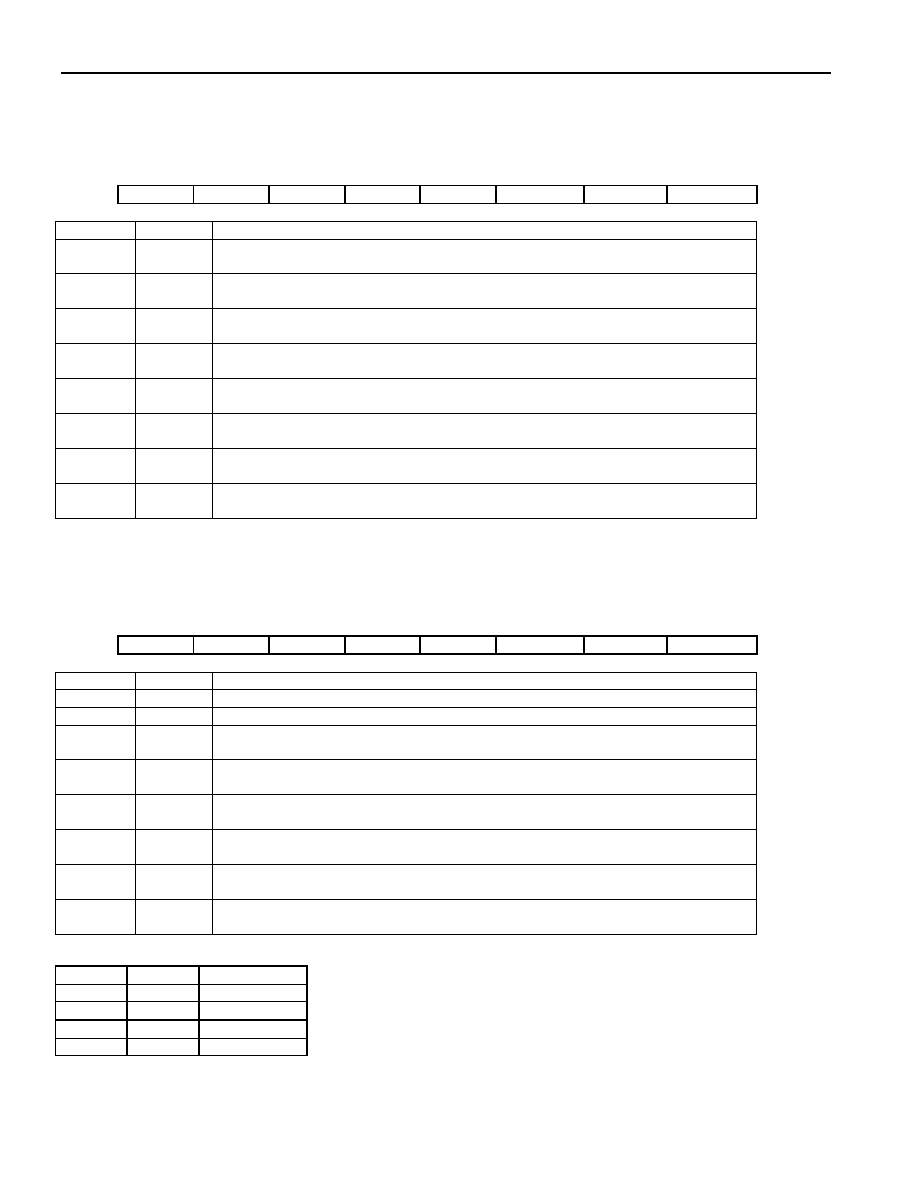

9.1 Interrupt Handling

The host can quickly determine which status registers in the four ports are causing an interrupt by reading one of

the unused addresses such as 0Ch, 0Dh, or 0Eh in any port.

Bit #

7

6

5

4

3

2

1

0

Name

SR2P4

SR1P4

SR2P3

SR1P3

SR2P2

SR1P2

SR2P1

SR1P1

NAME

BIT

FUNCTION

SR2P4

7

Status Register 2, Port 4. A 1 in this bit position indicates that status register 2

in port 4 is asserting an interrupt.

SR1P4

6

Status Register 1, Port 4. A 1 in this bit position indicates that status register 1

in port 4 is asserting an interrupt.

SR2P3

5

Status Register 2, Port 3. A 1 in this bit position indicates that status register 2

in port 3 is asserting an interrupt.

SR1P3

4

Status Register 1, Port 3. A 1 in this bit position indicates that status register 1

in port 3 is asserting an interrupt.

SR2P2

3

Status Register 2, Port 2. A 1 in this bit position indicates that status register 2

in port 2 is asserting an interrupt.

SR1P2

2

Status Register 1, Port 2. A 1 in this bit position indicates that status register 1

in port 2 is asserting an interrupt.

SR2P1

1

Status Register 2, Port 1. A 1 in this bit position indicates that status register 2

in port 1 is asserting an interrupt.

SR1P1

0

Status Register 1, Port 1. A 1 in this bit position indicates that status register 1

in port 1 is asserting an interrupt.

Register Name:

RIR

Register Description:

Receive Information Register

Register Address:

08 Hex

Bit #

7

6

5

4

3

2

1

0

Name

RGM1

RGM0

JALT

RESF

RESE

CRCRC

FASRC

CASRC

NAME

BIT

FUNCTION

RGM1

7

Receive Gain Monitor Bit 1. See table below for level indication.

RGM0

6

Receive Gain Monitor Bit 0. See table below for level indication.

JALT

5

Jitter Attenuator Limit Trip. Set when the jitter attenuator FIFO reaches to

within 4 bits of its limit; useful for debugging jitter attenuation operation.

RESF

4

Receive Elastic Store Full. Set when the receive elastic store buffer fills and a

frame is deleted.

RESE

3

Receive Elastic Store Empty. Set when the receive elastic store buffer

empties and a frame is repeated.

CRCRC

2

CRC Resync Criteria Met. Set when 915/1000 codewords are received in

error.

FASRC

1

FAS Resync Criteria Met. Set when three consecutive FAS words are

received in error.

CASRC

0

CAS Resync Criteria Met. Set when two consecutive CAS MF alignment

words are received in error.

Level Indication

RGM1

RGM0

LEVEL (dB)

0

0 to 10

0

1

10 to 20

1

0

20 to 30

1

>30

相关PDF资料 |

PDF描述 |

|---|---|

| RCM28DCTH | CONN EDGECARD 56POS DIP .156 SLD |

| EET-ED2D152EA | CAP ALUM 1500UF 200V 20% SNAP |

| RCM28DCTD | CONN EDGECARD 56POS DIP .156 SLD |

| PLE0G681MDO1 | CAP ALUM 680UF 4V 20% RADIAL |

| PLE0E561MCO1 | CAP ALUM 560UF 2.5V 20% RADIAL |

相关代理商/技术参数 |

参数描述 |

|---|---|

| DS21Q59L | 功能描述:网络控制器与处理器 IC Quad E1 Transceiver RoHS:否 制造商:Micrel 产品:Controller Area Network (CAN) 收发器数量: 数据速率: 电源电流(最大值):595 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:PBGA-400 封装:Tray |

| DS21Q59L+ | 功能描述:网络控制器与处理器 IC Quad E1 Transceiver RoHS:否 制造商:Micrel 产品:Controller Area Network (CAN) 收发器数量: 数据速率: 电源电流(最大值):595 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:PBGA-400 封装:Tray |

| DS21Q59LN | 功能描述:网络控制器与处理器 IC Quad E1 Transceiver RoHS:否 制造商:Micrel 产品:Controller Area Network (CAN) 收发器数量: 数据速率: 电源电流(最大值):595 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:PBGA-400 封装:Tray |

| DS21Q59LN+ | 功能描述:网络控制器与处理器 IC Quad E1 Transceiver RoHS:否 制造商:Micrel 产品:Controller Area Network (CAN) 收发器数量: 数据速率: 电源电流(最大值):595 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:PBGA-400 封装:Tray |

| DS21S07A | 制造商:Maxim Integrated Products 功能描述: |

发布紧急采购,3分钟左右您将得到回复。