- 您现在的位置:买卖IC网 > PDF目录16264 > DS21Q59DK (Maxim Integrated Products)KIT DESIGN FOR DS21Q59 PDF资料下载

参数资料

| 型号: | DS21Q59DK |

| 厂商: | Maxim Integrated Products |

| 文件页数: | 46/76页 |

| 文件大小: | 0K |

| 描述: | KIT DESIGN FOR DS21Q59 |

| 产品培训模块: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 标准包装: | 1 |

| 主要目的: | 电信,调帧器和线路接口装置(LIU) |

| 已用 IC / 零件: | DS21Q59 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页当前第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页

DS21Q59 Quad E1 Transceiver

50 of 76

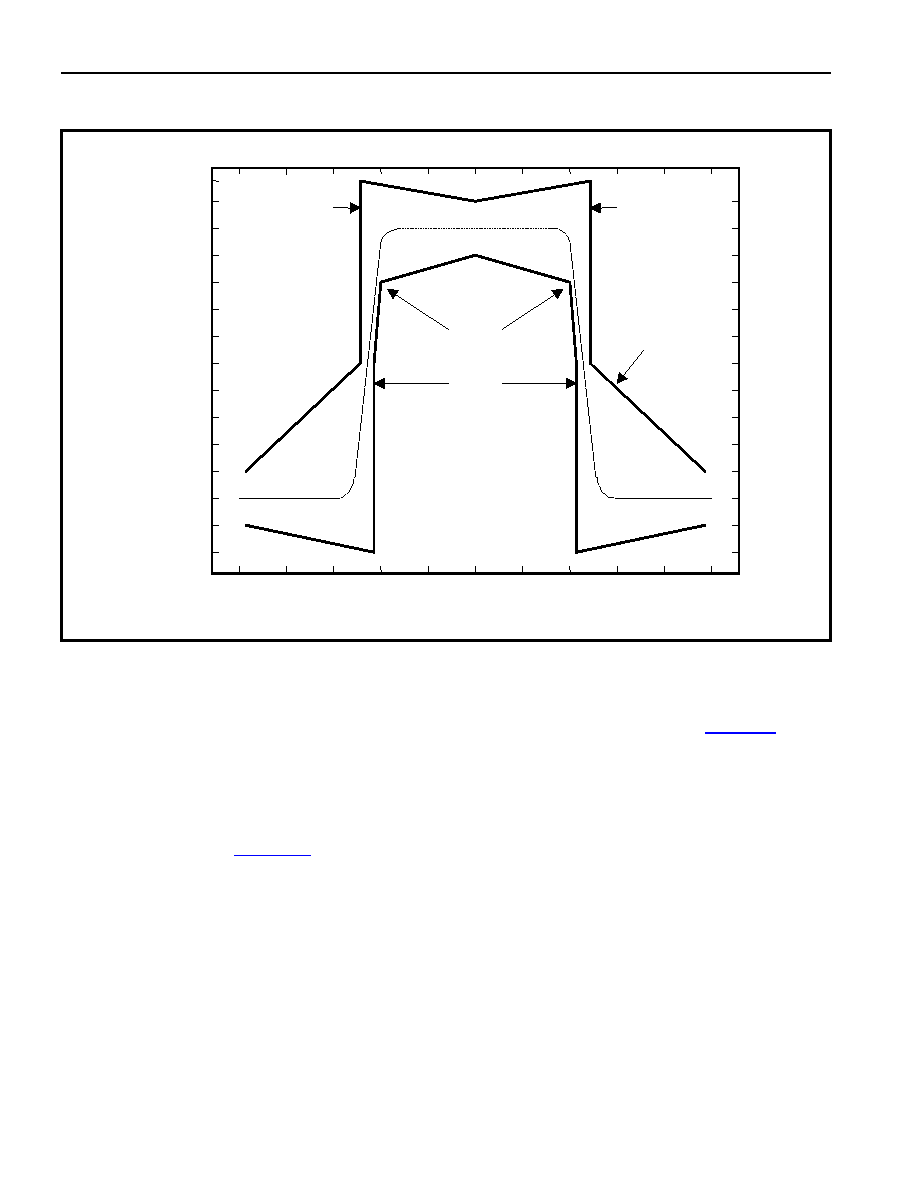

Figure 21-3. Transmit Waveform Template

21.3 Jitter Attenuators

The DS21Q59 contains an on-board clock and data jitter attenuator for each transceiver and a single, undedicated

“clock only” jitter attenuator. This undedicated jitter attenuator is shown in the block diagram (Figure 3-1) as the

alternate jitter attenuator.

21.3.1 Clock and Data Jitter Attenuators

The clock and data jitter attenuators can be mapped into the receive or transmit paths and can be set to buffer

depths of either 32 or 128 bits through the LICR. The 128-bit mode is used in applications where large excursions

of wander are expected. The 32-bit mode is used in delay-sensitive applications. The characteristics of the

attenuators are shown in Figure 21-5. The jitter attenuators can be placed in either the receive path or the transmit

path by appropriately setting or clearing the JAS bit in the LICR. Also, setting the DJA bit in the LICR can disable

the jitter attenuator (in effect, remove it). For the jitter attenuator to operate properly, a 2.048MHz clock (±50ppm)

must be applied at the MCLK pin. On-board circuitry adjusts either the recovered clock from the clock/data

recovery block or the clock applied at the TCLKI pin to create a smooth jitter-free clock that is used to clock data

out of the jitter attenuator FIFO. It is acceptable to provide a gapped/bursty clock at the TCLKI pin if the jitter

attenuator is placed on the transmit side. If the incoming jitter exceeds either 120UIP-P (buffer depth is 128 bits) or

28UIP-P (buffer depth is 32 bits), the DS21Q59 divides the internal nominal 32.768MHz clock by either 15 or 17

instead of the normal 16 to keep the buffer from overflowing. When the device divides by either 15 or 17, it also

sets the jitter attenuator limit trip (JALT) bit in the receive information register (RIR.5).

0

-0.1

-0.2

0.1

0.2

0.3

0.4

0.5

0.6

0.7

0.8

0.9

1.0

1.1

1.2

0

TIME (ns)

SCALED

AM

PLITUDE

50

100

150

200

250

-50

-100

-150

-200

-250

269ns

194ns

219ns

(in

75

W

sy

st

em

s,

1

.0

on

the

sc

al

e=

2.

37

V

peak

in

120

W

sys

te

m

s,

1.

0

on

the

s

ca

le

=

3.

00V

pea

k)

G.703

TEMPLATE

相关PDF资料 |

PDF描述 |

|---|---|

| RCM28DCTH | CONN EDGECARD 56POS DIP .156 SLD |

| EET-ED2D152EA | CAP ALUM 1500UF 200V 20% SNAP |

| RCM28DCTD | CONN EDGECARD 56POS DIP .156 SLD |

| PLE0G681MDO1 | CAP ALUM 680UF 4V 20% RADIAL |

| PLE0E561MCO1 | CAP ALUM 560UF 2.5V 20% RADIAL |

相关代理商/技术参数 |

参数描述 |

|---|---|

| DS21Q59L | 功能描述:网络控制器与处理器 IC Quad E1 Transceiver RoHS:否 制造商:Micrel 产品:Controller Area Network (CAN) 收发器数量: 数据速率: 电源电流(最大值):595 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:PBGA-400 封装:Tray |

| DS21Q59L+ | 功能描述:网络控制器与处理器 IC Quad E1 Transceiver RoHS:否 制造商:Micrel 产品:Controller Area Network (CAN) 收发器数量: 数据速率: 电源电流(最大值):595 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:PBGA-400 封装:Tray |

| DS21Q59LN | 功能描述:网络控制器与处理器 IC Quad E1 Transceiver RoHS:否 制造商:Micrel 产品:Controller Area Network (CAN) 收发器数量: 数据速率: 电源电流(最大值):595 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:PBGA-400 封装:Tray |

| DS21Q59LN+ | 功能描述:网络控制器与处理器 IC Quad E1 Transceiver RoHS:否 制造商:Micrel 产品:Controller Area Network (CAN) 收发器数量: 数据速率: 电源电流(最大值):595 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:PBGA-400 封装:Tray |

| DS21S07A | 制造商:Maxim Integrated Products 功能描述: |

发布紧急采购,3分钟左右您将得到回复。