参数资料

| 型号: | DS33ZH11+ |

| 厂商: | Maxim Integrated Products |

| 文件页数: | 156/172页 |

| 文件大小: | 0K |

| 描述: | IC MAPPER ETHERNET 100CSBGA |

| 产品培训模块: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 标准包装: | 7 |

| 应用: | 数据传输 |

| 接口: | 串行 |

| 电源电压: | 1.8V,2.5V,3.3V |

| 封装/外壳: | 100-LFBGA,CSPBGA |

| 供应商设备封装: | 100-CSBGA(10x10) |

| 包装: | 托盘 |

| 安装类型: | 表面贴装 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页第137页第138页第139页第140页第141页第142页第143页第144页第145页第146页第147页第148页第149页第150页第151页第152页第153页第154页第155页当前第156页第157页第158页第159页第160页第161页第162页第163页第164页第165页第166页第167页第168页第169页第170页第171页第172页

DS33Z11 Ethernet Mapper

84 of 172

9.4 BERT Registers

Register Name:

BCR

Register Description:

BERT Control Register

Register Address:

80h

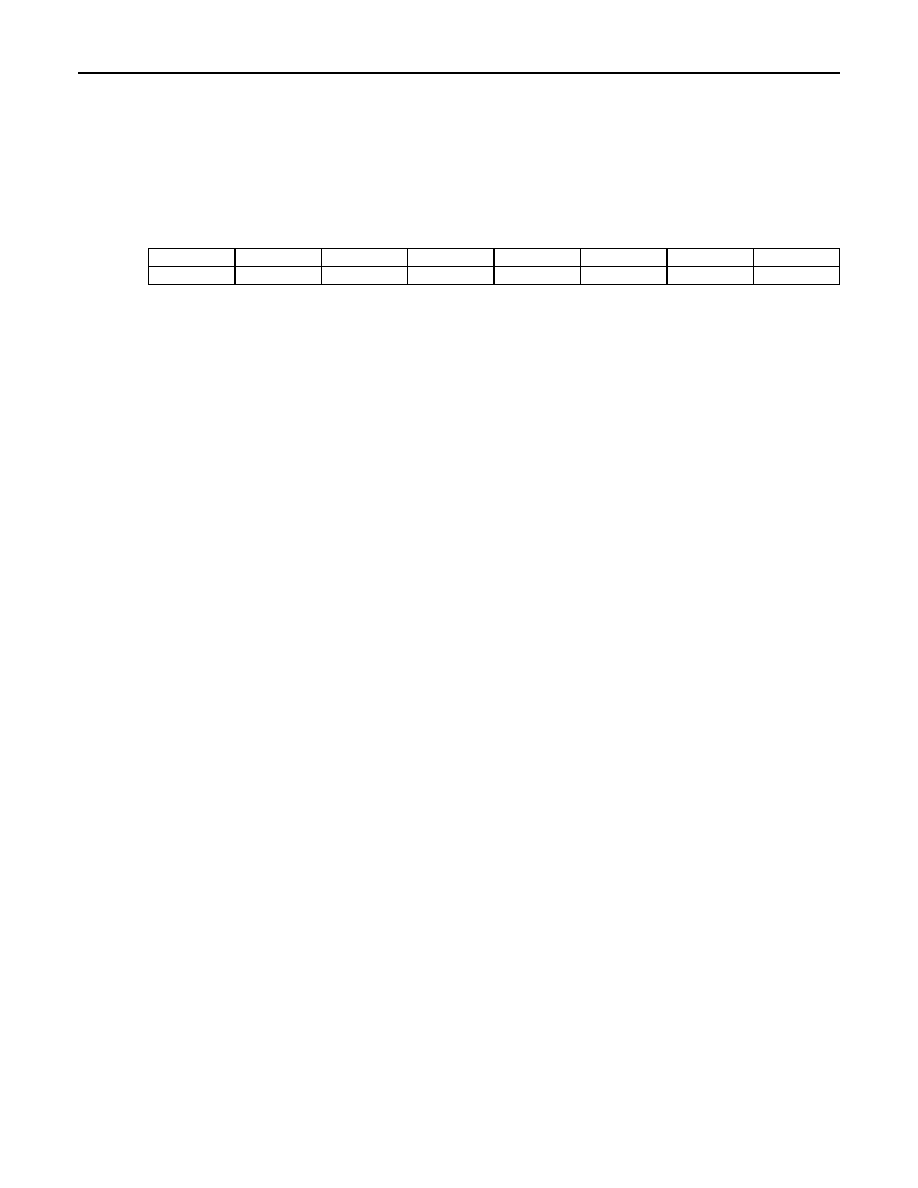

Bit #

7

6

5

4

3

2

1

0

Name

-

PMU

RNPL

RPIC

MPR

APRD

TNPL

TPIC

Default

0

Bit 7: This bit must be kept low for proper operation.

Bit 6: Performance Monitoring Update (PMU) This bit causes a performance monitoring update to be initiated.

A 0 to 1 transition causes the performance monitoring registers to be updated with the latest data, and the

counters reset (0 or 1). For a second performance monitoring update to be initiated, this bit must be set to 0, and

back to 1. If PMU goes low before the PMS bit goes high, an update might not be performed.

Bit 5: Receive New Pattern Load (RNPL) A zero to one transition of this bit will cause the programmed test

pattern (QRSS, PTS, PLF [4:0}, PTF [4:0], and BSP [31:0]) to be loaded in to the receive pattern generator. This

bit must be changed to zero and back to one for another pattern to be loaded. Loading a new pattern will forces

the receive pattern generator out of the “Sync” state which causes a resynchronization to be initiated. Note:

QRSS, PTS, PLF [4:0}, PTF [4:0], and BSP [31:0] must not change from the time this bit transitions from 0 to 1

until four RCLKI clock cycles after this bit transitions from 0 to 1.

Bit 4: Receive Pattern Inversion Control (RPIC) When 0, the receive incoming data stream is not altered.

When 1, the receive incoming data stream is inverted.

Bit 3: Manual Pattern Resynchronization (MPR) A zero to one transition of this bit will cause the receive

pattern generator to resynchronize to the incoming pattern. This bit must be changed to zero and back to one for

another resynchronization to be initiated. Note: A manual resynchronization forces the receive pattern generator

out of the “Sync” state.

Bit 2: Automatic Pattern Resynchronization Disable (APRD) When 0, the receive pattern generator will

automatically resynchronize to the incoming pattern if six or more times during the current 64-bit window the

incoming data stream bit and the receive pattern generator output bit did not match. When 1, the receive pattern

generator will not automatically resynchronize to the incoming pattern. Note: Automatic synchronization is

prevented by not allowing the receive pattern generator to automatically exit the “Sync” state.

Bit 1: Transmit New Pattern Load (TNPL) A zero to one transition of this bit will cause the programmed test

pattern (QRSS, PTS, PLF[4:0}, PTF[4:0], and BSP[31:0]) to be loaded in to the transmit pattern generator. This bit

must be changed to zero and back to one for another pattern to be loaded. Note: QRSS, PTS, PLF[4:0}, PTF[4:0],

and BSP[31:0] must not change from the time this bit transitions from 0 to 1 until four TCLKI clock cycles after this

bit transitions from 0 to 1.

Bit 0: Transmit Pattern Inversion Control (TPIC) When 0, the transmit outgoing data stream is not altered.

When 1, the transmit outgoing data stream is inverted.

相关PDF资料 |

PDF描述 |

|---|---|

| DS34C87TN/NOPB | IC LINE DRIVER QUAD CMOS 16-DIP |

| DS34LV87TMX/NOPB | IC LINE DVR QUAD CMOS DIF 16SOIC |

| DS34S132GN+ | IC TDM OVER PACKET 676-BGA |

| DS34T102GN+ | IC TDM OVER PACKET 484TEBGA |

| DS3501U+H | IC POT NV 128POS HV 10-USOP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| DS33ZH11+ | 功能描述:网络控制器与处理器 IC 10/100 ENETXPORT HMODE MAP IND RoHS:否 制造商:Micrel 产品:Controller Area Network (CAN) 收发器数量: 数据速率: 电源电流(最大值):595 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:PBGA-400 封装:Tray |

| DS34 | 制造商:LUMILEDS 制造商全称:LUMILEDS 功能描述:power light source Luxeon V Emitter |

| DS-3400D UK | 制造商:TRUST 功能描述:DESKTOP WIRELESS OPTICAL TRUST |

| DS3404FP000 | 制造商:Thomas & Betts 功能描述:30A,PLG,3P4W,MG,404,3P480V |

| DS3404FP000/JG63 | 制造商:Thomas & Betts 功能描述:30A,CON,3P4W,MG,404,3P480V,JG63,SC |

发布紧急采购,3分钟左右您将得到回复。