- 您现在的位置:买卖IC网 > PDF目录67672 > GP2021 (Mitel Networks Corporation) GPS 12 channel Correlator Advance Information PDF资料下载

参数资料

| 型号: | GP2021 |

| 厂商: | Mitel Networks Corporation |

| 英文描述: | GPS 12 channel Correlator Advance Information |

| 中文描述: | 全球定位系统12通道相关器研究进展信息 |

| 文件页数: | 20/62页 |

| 文件大小: | 372K |

| 代理商: | GP2021 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页当前第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页

27

GP2021

NOTE: The registers labelled * (the CODE_PHASE_COUNTER and CARRIER_CYCLE_CONTROL) can only be written

to if ‘Test’ mode has been selected by setting bit 3 of the TEST CONTROL register to High.

In both the ACCUM and CNTL sections there are some

addresses labelled ALL or MULTI in place of CHx. Writing to

these addresses will write to all channels or to a selection set

by MULTI_CHANNEL_SELECT in one operation and so may

be used to initialise the system quickly or to load the next

search settings with little bus use. This is a write only function

and the corresponding CHx read functions are not available

at addresses labelled ALL or MULTI.

It can be seen that the addresses in CNTL are used to

control the device in write mode but give the Measurement

Data when in read mode.

Apart from the Code and Carrier DCO increment values

all data transfers are only 16 bit wide. Writes to the Code and

Carrier DCO’s are 32 bit data transfers where the _HIGH word

should be written first and will be retained in the 16 to 32 bit

interface until the _LOW word is written, which must occur as

the next write to the chip. All 32 bits will then be transferred into

the DCO increment register. Data is written to an input buffer

in the 16 to 32 bit interface and will be transferred to its

destination register during the next full cycle of the 7 (or 6)

phase clock. Write cycles should therefore have a period of at

least 300 ns. The X_DCO_INCR_HIGH may be used to write

the high bits of the increment number to any or all DCO’s as

an

alternative

to

using

the

CHx_CODE

CARRIER_DCO_INCR– _HIGH addresses. By using this

address, there is no need to wait 300ns before writing the

_LOW part. For further information refer to General Interface

Timing in Microprocessor Interface section.

The bit assignments for the Correlator registers are given

below, but two write–only registers do not have any data bits,

these are:

(1) A write to the CHx_ACCUM_RESET register (irrespective

of what data is written) will reset the ACCUM_STATUS_A,

ACCUM_STATUS_B, and ACCUM_STATUS_C registers for

that channel.

(2) A write to the STATUS register (irrespective of what data

is written) will latch the state of the various status flags into

ACCUM_STATUS_A,

ACCUM_STATUS_B,

ACCUM_STATUS_C

Registers for all channels. This allows a polling based rather

than Interrupt driven tracking scheme.

The registers are listed in alphabetical order and not in

address order to allow easy reference to each section. Unless

otherwise stated the LSB is bit 0 and the MSB is bit 15 or as

far up the register as there is data. Note that most registers do

not have both read and write functions, and many addresses

are shared between read–only and write–only registers

having different functions.

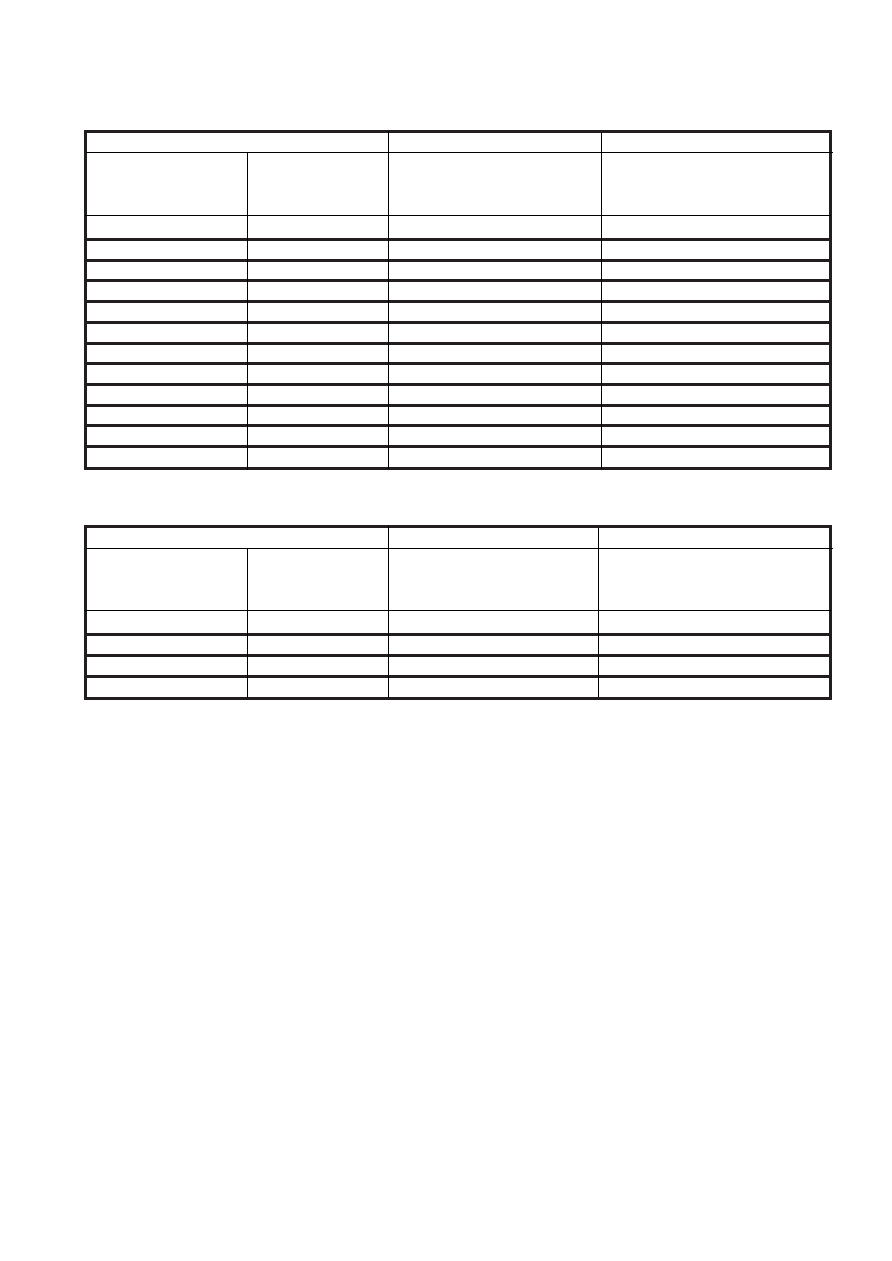

ADDRESS (Hex)

WRITE FUNCTION

READ FUNCTION

ARM SYSTEM

STANDARD

MODE

INTERFACE

MODE

200

80

STATUS

ACCUM_STATUS_C

204

81

not used

MEAS_STATUS_A

208

82

not used

ACCUM_STATUS_A

20C

83

not used

ACCUM_STATUS_B

ADDRESS (Hex)

WRITE FUNCTION

READ FUNCTION

ARM MODE

STANDARD

SYSTEM

INTERFACE

MODE

CNTL

+ 00

CNTL

+ 0

SATCNTL

CODE_SLEW

+ 04

+ 1

CODE PHASE COUNTER*

CODE_PHASE

+ 08

+ 2

CARRIER_CYCLE_COUNTER*

CARRIER_CYCLE_LOW

+ 0C

+ 3

CARRIER_DCO_INCR_HIGH

CARRIER_DCO_PHASE

+ 10

+ 4

CARRIER_DCO_INCR_LOW

EPOCH (Latched0

+ 14

+ 5

CODE_DCO_INCR_HIGH

CODE_DCO_PHASE

+ 18

+ 6

CODE_DCO_INCR_LOW

CARRIER_CYCLE_HIGH

+ 1C

+ 7

EPOCH_COUNT_LOAD

EPOCH_CHECK (Not latched)

ACCUM + 00

ACCUM + 0

CODE_SLEW_COUNTER

I_TRACK

+ 04

+ 1

ACCUM_RESET

Q_TRACK

+ 08

+ 2

not used

I_PROMPT

+ 0C

+ 3

CODE_DCO_PRESET_PHASE

Q_PROMPT

Tracking Channel Registers

相关PDF资料 |

PDF描述 |

|---|---|

| GRM40Y5V105Z16 | Circular Connector; MIL SPEC:MIL-C-26482, Series I, Solder; Body Material:Aluminum; Series:PT06; No. of Contacts:21; Connector Shell Size:22; Connecting Termination:Solder; Circular Shell Style:Straight Plug; Body Style:Straight |

| GRM42-6X5R475K10 | 50/100M SOT-23 CMOS RF LDO REGULATORS |

| GT- 32090 | Highly Integrated Single-Chip System Controller(高集成单片系统控制器) |

| GT-48001A | Switched Ethernet Controller For 10BaseX(10BaseX交换式快速以太网控制器) |

| GT-48002A | Switched Fast Ethernet Controller for 100BaseX(100BaseX交换式快速以太网控制器) |

相关代理商/技术参数 |

参数描述 |

|---|---|

| GP2021IGGQ1R | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Correlator |

| GP202K | 制造商:GTM 制造商全称:GTM 功能描述:SURFACE MOUNT,SWITCHING DIODE |

| GP2030S | 制造商:GTM 制造商全称:GTM 功能描述:N AND P-CHANNEL ENHANCEMENT MODE POWER MOSFET |

| GP2-031X250-50 | 制造商:GROOV-PIN 功能描述: |

| GP204 | 制造商:DEC 制造商全称:DEC 功能描述:2 AMP SOFT GLASS PASSIVATED DIODES |

发布紧急采购,3分钟左右您将得到回复。