- 您现在的位置:买卖IC网 > PDF目录67672 > GP2021 (Mitel Networks Corporation) GPS 12 channel Correlator Advance Information PDF资料下载

参数资料

| 型号: | GP2021 |

| 厂商: | Mitel Networks Corporation |

| 英文描述: | GPS 12 channel Correlator Advance Information |

| 中文描述: | 全球定位系统12通道相关器研究进展信息 |

| 文件页数: | 35/62页 |

| 文件大小: | 372K |

| 代理商: | GP2021 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页当前第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页

40

GP2021

DATA_RETENT

(Write / Read Address)

This is a byte wide Read/Write register which can be used

to store a predetermined value, which can be interrogated in

order to determine whether a total power loss (below the data

retention level ) has occurred.

General Control

IO_CONFIG

(Write / Read Address)

The IO_CONFIG register is a full 16 bit wide read/write

register containing two separate elements: A 16 bit wide read

location which allows the controlling microprocessor to view

the input level on all the Discrete and Multi Function inputs,

and a 16 bit wide write location for configuration of the

Discreteand Multi Function I/O pins.

IO_CONFIG Read: A read of the IO_CONFIG address

will latch the logic level of a number of input pins and output

these levels to the microprocessor via the 16 bit data bus. This

allows the microprocessor to read the input levels on all the

Discrete and Multi Function Inputs from a single location. The

bit allocations are as follows:

Bit

Input Pin

15

RXB

14

RXA

13

DISCOP

12

DISCIP

11

MAG1

10

SIGN1

9

MAG0

8

SIGN0

7

MULTI_FN_IO

6

NBRAM

5

DISCIO

4

NARMSYS

3

NBW/WRPROG

2

NMREQ

1

NOPC/NINTELMOT

0

NRW

It should be noted that the usefulness of a number of these

inputs as Discrete Inputs for System Control is dependant

upon the Interface Mode of the GP2021. For instance it is

possible to use the NOPC/NINTELMOT pin as a Discrete

Input in ARM System mode if the DEBUG function is disabled,

whereas this pin could not be used as a Discrete Input in

Standard Interface Mode. Similarly, NMREQ could be used

as a Discrete Input in Standard Interface Mode but not in ARM

System Mode.

IO_CONFIG Write: The IO_CONFIG write location

allows the configuration of the multi purpose I/O pins DISCIO

and MULTI_FN_IO. The register bit assignments are as

follows:

Bit

Bit Name

15 to 13

Not Used

12

MULTI_FN_IO_SELECT_TIMEMARK

11

MULTI_FN_IO_SELECT_100KHZ

10

MULTI_FN_IO_LEVEL

9 to 8

MULTI_FN_IO_CONFIG

7 to 4

Not Used

3

DISCIO_SELECT_TIMEMARK

2

DISCIO_SELECT_100KHZ

1

DISCIO_LEVEL

0

DISCIO_CONFIG

DISCIO_CONFIG: When set High this bit configures the

DISCIO pin as a Discrete Output, when low the DISCIO pin is

configured as a Discrete Input. A Master Reset sets the

DISCIO_CONFIG bit Low.

DISCIO_SELECT TIMEMARK,

DISCIO_SELECT_100KHZ,

DISCIO_LEVEL:

When configured as an output, the DISCIO pin can be

setup to give a signal as determined by Table 20.

At power on reset, the DISCIO output value = 0 setting is

chosen. The 100kHz square wave is derived from the Master

Clock and is useful for measuring its drift.

MULTI_FN_IO_SELECT TIMEMARK,

MULTI_FN_IO_SELECT_100KHz,

MULTI_FN_IO_LEVEL:

When configured as an output, the MULTI_FN_IO pin

can be setup to give a signal as shown in Table 21

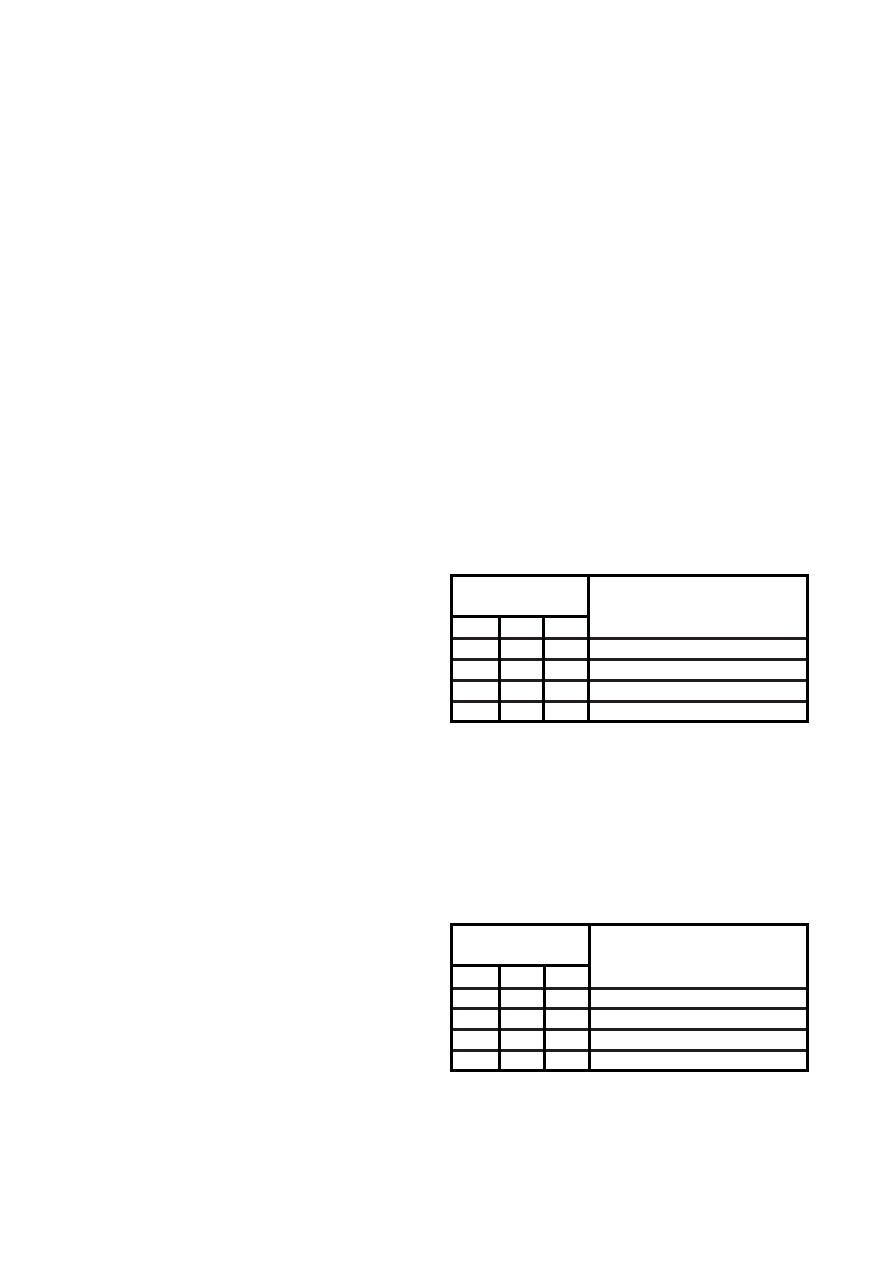

Bit

DISCIO output value

32

1

00

0

00

1

0

1

X

100kHz square wave

0

X

TIMEMARK

Table 20: DISCIO output selection.

Bit

DISCIO output value

12

11

10

00

0

00

1

0

1

X

100kHz square wave

0

X

TIMEMARK

Table 21: MULTI_FN_IO output selection.

相关PDF资料 |

PDF描述 |

|---|---|

| GRM40Y5V105Z16 | Circular Connector; MIL SPEC:MIL-C-26482, Series I, Solder; Body Material:Aluminum; Series:PT06; No. of Contacts:21; Connector Shell Size:22; Connecting Termination:Solder; Circular Shell Style:Straight Plug; Body Style:Straight |

| GRM42-6X5R475K10 | 50/100M SOT-23 CMOS RF LDO REGULATORS |

| GT- 32090 | Highly Integrated Single-Chip System Controller(高集成单片系统控制器) |

| GT-48001A | Switched Ethernet Controller For 10BaseX(10BaseX交换式快速以太网控制器) |

| GT-48002A | Switched Fast Ethernet Controller for 100BaseX(100BaseX交换式快速以太网控制器) |

相关代理商/技术参数 |

参数描述 |

|---|---|

| GP2021IGGQ1R | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Correlator |

| GP202K | 制造商:GTM 制造商全称:GTM 功能描述:SURFACE MOUNT,SWITCHING DIODE |

| GP2030S | 制造商:GTM 制造商全称:GTM 功能描述:N AND P-CHANNEL ENHANCEMENT MODE POWER MOSFET |

| GP2-031X250-50 | 制造商:GROOV-PIN 功能描述: |

| GP204 | 制造商:DEC 制造商全称:DEC 功能描述:2 AMP SOFT GLASS PASSIVATED DIODES |

发布紧急采购,3分钟左右您将得到回复。