- 您现在的位置:买卖IC网 > PDF目录67672 > GP2021 (Mitel Networks Corporation) GPS 12 channel Correlator Advance Information PDF资料下载

参数资料

| 型号: | GP2021 |

| 厂商: | Mitel Networks Corporation |

| 英文描述: | GPS 12 channel Correlator Advance Information |

| 中文描述: | 全球定位系统12通道相关器研究进展信息 |

| 文件页数: | 26/62页 |

| 文件大小: | 372K |

| 代理商: | GP2021 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页当前第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页

32

GP2021

GPS PRN

BIT SETTING

GPS PRN

BIT SETTING

Signal No

9 to 0

Signal No

9 to 0

1

3F6H

24

338H

2

3ECH

25

27OH

3

3D8H

26

OEDH

4

3BOH

27

1COH

5

04BH

28

38OH

6

096H

29

22BH

7

2CBH

30

056H

8

196H

31

OACH

9

32CH

32

158H

10

3BAH

33

2BOH

11

374H

34*

058H

12

1DOH

35

18BH

13

3AOH

36

316H

14

340H

37*

058H

15

280H

201 GIC

2C4H

16

100H1

202 GIC

10AH

17

113H

205 GIC

3E3H

18

226H

206 GIC

OF8H

19

04CH

207 GIC

25FH

20

098H

208 GIC

1E7H

21

130H

209 GIC

2B5H

22

260H

211 GIC

10EH

23

267H

CHx_I_TRACK,

CHx_Q_TRACK,

CHx_I_PROMPT,

CHx_Q_PROMPT

(Read Address)

Bits 15 to 0: Accumulated Data registers, which are used on

each DUMP to store the 16–bit Integrate–and–Dump

accumulator results. The values contained in the registers are

2’s complement values with the valid range of the data from

–2 15 to +(2 15 –1).

These registers are read–only registers which can be

read at any time. Their content is not protected by any

overwrite protection mechanism, so the set of four registers

must be read soon after a ACCUM_INT to be sure that newer

data will not cause an overwrite part way through the set. The

CHx_I_PROMPT and CHx_Q_PROMPT contain the

Accumulated Data from the Prompt arm. The CHx_I_TRACK

and CHx_Q_TRACK contain the Accumulated Data from the

Tracking arm.

To track satellites correctly, only data read with the

CHx_NEW_ACCUM_DATA bit set High should be used. An

overflow or underflow condition cannot be reached.

CHx_SATCNTL,

MULTI_ SATCNTL,

ALL_SATCNTL

(Write Address)

Bit

Bit Name

15

GPS_NGLON

14 to 13

TRACK_SEL

12

PRESET/UPDATEB

11

CODE_OFF/ONB

10

SOURCESEL

9 to 0

G2_LOAD (9 to 0)

CHx_SATCNTL is a write–only register that can be

written into at any time. Any modification to the content is

effective at the next DUMP in UPDATE mode or at the next

TIC in PRESET mode for all bits, apart from PRESET

UPDATEB,which defines whether a channel is in PRESET or

UPDATE mode. It is important to program this register first

when starting the initialisation of a PRESET sequence to get

the channel into PRESET mode, or the other write operations

will act too soon.

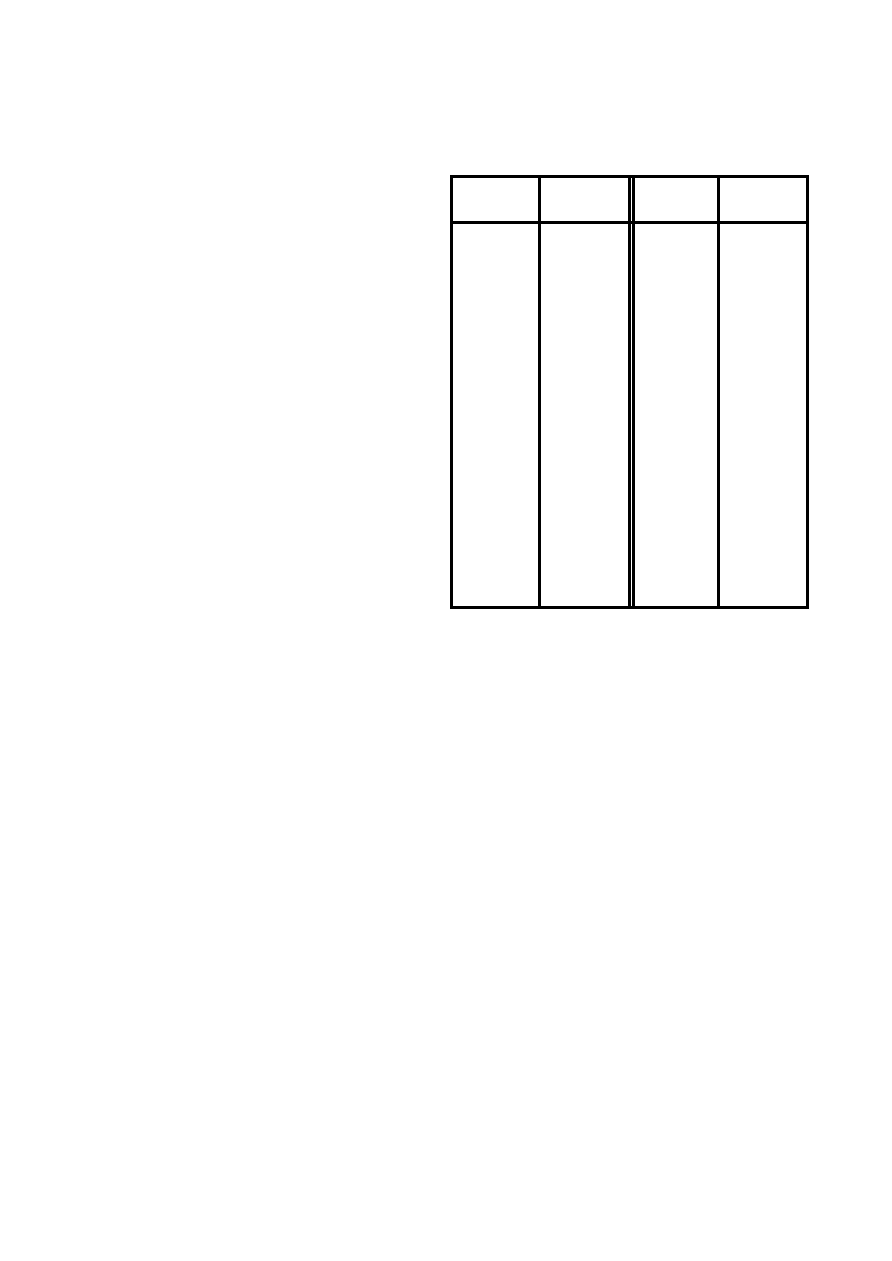

G2_LOAD (9 to 0), bits 9 to 0: C/A CODE SELECTION

FUNCTION: The CHx_SATCNTL register programs the

CODE GENERATOR by setting the G2 register to the

appropriate starting pattern to generate the required GPS or

INMARSAT–GIC codes. The G2_LOAD register may be

programmed at any time but the value is only used when the

code sequence restarts, at the following DUMP in UPDATE

mode, or at the following TIC in PRESET mode. The pattern

to load is the register state for the time of the second code

chip. The following table shows the values required to select

one of the 37 GPS or the 8 INMARSAT–GIC possible PRN

(Pseudo Random Noise) patterns.

In UPDATE mode, the C/A code generated by the CODE

GENERATOR will be changed at the DUMP following the

write to CHx_SATCNTL and at this DUMP the Accumulated

Data will be valid for the previous code selection. Later

DUMPs will be valid for the new code.

If all zeros are loaded into the G2 register it will not clock

out, and the G1 generator code will be seen on the output. This

is an illegal state which is only of use for chip testing.

PRN sequences 201 to 211 are selected for INMARSAT

GIC (GPS Integrity Channel) use.Due to the initialisation of

the Early–Prompt–Late shift register, all codes will always

start with a ”1” for the first bit of the sequence after a Code

change or a Code Slew. Subsequent cycles of the PRN

sequence will be correct for the chosen satellite.

SOURCESEL, bit 10: Selects which input source to be

used by the channel when in Real_Input mode. Low selects

SIGN0 and MAG0, High selects SIGN1 and MAG1.

CODE_OFF/ONB, bit 11: When Low, the code is output

normally, but when High, the Prompt, Early and Late codes

are held High (code mixer outputs exactly follow inputs) and

the Early–minus–late code is held LOW. This is intended for

test purposes only.

PRESET/UPDATEB, bit 12: When High sets the channel

into Preset mode, or when Low, sets the channel into Update

mode. This bit is cleared to Low after the Preset function has

been done, that is after the first TIC following the loading of the

Epoch counters.

TRACK_SEL (1 and 0), bits 14 and 13: Select the

appropriate code to be produced by the Tracking arm output

of the code generator as follows:

Table 9 : G2 LOAD settings required for satellite selection.

*C/A Codes 34 and 37 are equivalent.

Notes: PRN sequences 33 to 37 are reserved for non–satellite

uses (e.g. ground transmitters).

相关PDF资料 |

PDF描述 |

|---|---|

| GRM40Y5V105Z16 | Circular Connector; MIL SPEC:MIL-C-26482, Series I, Solder; Body Material:Aluminum; Series:PT06; No. of Contacts:21; Connector Shell Size:22; Connecting Termination:Solder; Circular Shell Style:Straight Plug; Body Style:Straight |

| GRM42-6X5R475K10 | 50/100M SOT-23 CMOS RF LDO REGULATORS |

| GT- 32090 | Highly Integrated Single-Chip System Controller(高集成单片系统控制器) |

| GT-48001A | Switched Ethernet Controller For 10BaseX(10BaseX交换式快速以太网控制器) |

| GT-48002A | Switched Fast Ethernet Controller for 100BaseX(100BaseX交换式快速以太网控制器) |

相关代理商/技术参数 |

参数描述 |

|---|---|

| GP2021IGGQ1R | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Correlator |

| GP202K | 制造商:GTM 制造商全称:GTM 功能描述:SURFACE MOUNT,SWITCHING DIODE |

| GP2030S | 制造商:GTM 制造商全称:GTM 功能描述:N AND P-CHANNEL ENHANCEMENT MODE POWER MOSFET |

| GP2-031X250-50 | 制造商:GROOV-PIN 功能描述: |

| GP204 | 制造商:DEC 制造商全称:DEC 功能描述:2 AMP SOFT GLASS PASSIVATED DIODES |

发布紧急采购,3分钟左右您将得到回复。