参数资料

| 型号: | HI7188IN |

| 厂商: | Intersil |

| 文件页数: | 11/24页 |

| 文件大小: | 0K |

| 描述: | CONV A/D 16BIT 8:1 MUX 44-MQFP |

| 标准包装: | 96 |

| 位数: | 16 |

| 采样率(每秒): | 240 |

| 数据接口: | QSPI?,串行,SPI? |

| 转换器数目: | 1 |

| 功率耗散(最大): | 50mW |

| 电压电源: | 模拟和数字,双 ± |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 44-QFP |

| 供应商设备封装: | 44-MQFP(10x10) |

| 包装: | 管件 |

| 输入数目和类型: | 8 个差分,单极;8 个差分,双极 |

19

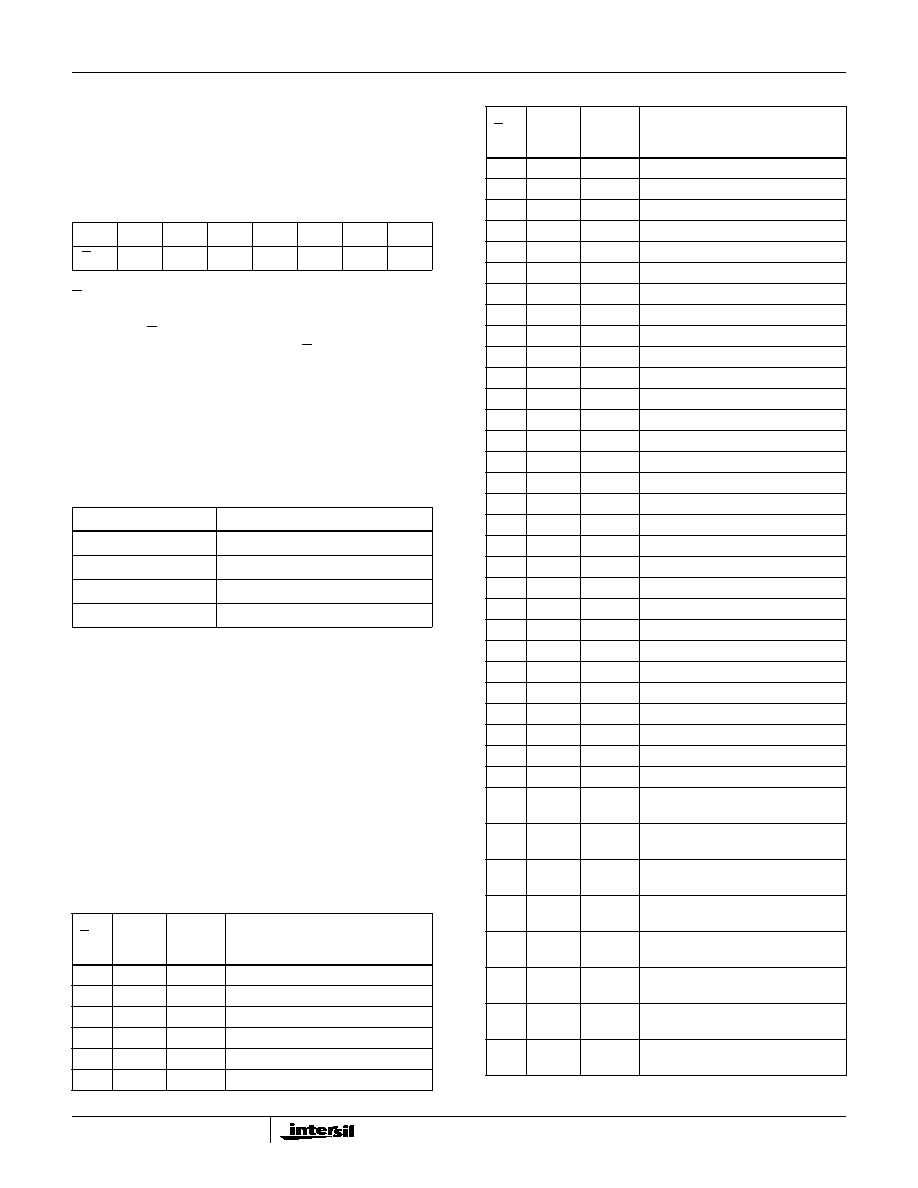

Detailed Register Descriptions

Instruction Register

The instruction register is an 8 bit register which is used

during a communications cycle for setting up read/write

operations. Below are the bit assignments.

R/W - Bit 7 of the Instruction Byte determines whether phase

2 of the communication cycle will be a read or write

operation. If R/W is logic 1, a write transfer will occur in

phase 2 of the communication cycle. If R/W is logic 0, a read

transfer will occur in phase 2 of the communication cycle.

NB1, NB0 - Bits 6 and 5 of the Instruction Byte determine the

number of bytes that will be transferred during phase 2 of a

communication cycle, if a register is selected for I/O access. If a

RAM is selected for IO access, these bits are don’t care. Any

number of bytes from 1 to 4 is allowed. See Tables 6 and 7.

RB - Bit 4 is used to determine the byte order when accessing

a RAM address. When accessing a RAM address, if RB = 1,

the data format is most significant byte first to least significant

byte. When accessing a RAM address, if RB = 0, the data

format is least significant byte first to most significant byte.

When accessing a register address, this bit is a don’t care.

A3, A2, A1, A0 - Bits 3 and 2 (A3 and A2) of the Instruction

Byte determine which of the three internal registers will be

accessed or if both bits are set (11b), that a RAM access is

active. For register addresses, bits 1 and 0 (A1 and A0)

determine which byte of that register will be accessed rst.

For RAM access (A3 = 1, A2 = 1), bits 1 and 0 (A1 and A0)

determine which RAM is the source or destination.

INSTRUCTION REGISTER (BYTE)

MSB

654321

LSB

R/W

NB1

NB0

RB

A3

A2

A1

A0

TABLE 6. MULTIPLE BYTE ACCESS BITS

NB1, NB0 IR [6:5]

DESCRIPTION

00

Transfer 1 Byte

01

Transfer 2 Bytes

10

Transfer 3 Bytes

11

Transfer 4 Bytes

TABLE 7. INTERNAL REGISTER ADDRESS

R/W

IR [7]

NB1,

NB0

IR [6:5]

A3, A2,

A1, A0

IR [3:0]

DESCRIPTION

0/1

00

0000

CR, start byte 0, 1 byte transfer

0/1

01

0000

CR, start byte 0, 2 byte transfer

0/1

00

0001

CR, start byte 1, 1 byte transfer

0/1

01

0001

CR, start byte 1, 2 byte transfer

0/1

00

0100

CCR #1, start byte 0, 1 byte transfer

0/1

00

0101

CCR #1, start byte 1, 1 byte transfer

0/1

00

0110

CCR #1, start byte 2, 1 byte transfer

0/1

00

0111

CCR #1, start byte 3, 1 byte transfer

0/1

01

0100

CCR #1, start byte 0, 2 byte transfer

0/1

01

0101

CCR #1, start byte 1, 2 byte transfer

0/1

01

0110

CCR #1, start byte 2, 2 byte transfer

0/1

01

0111

CCR #1, start byte 3, 2 byte transfer

0/1

10

0100

CCR #1, start byte 0, 3 byte transfer

0/1

10

0101

CCR #1, start byte 1, 3 byte transfer

0/1

10

0110

CCR #1, start byte 2, 3 byte transfer

0/1

10

0111

CCR #1, start byte 3, 3 byte transfer

0/1

11

0100

CCR #1, start byte 0, 4 byte transfer

0/1

11

0101

CCR #1, start byte 1, 4 byte transfer

0/1

11

0110

CCR #1, start byte 2, 4 byte transfer

0/1

11

0111

CCR #1, start byte 3, 4 byte transfer

0/1

00

1000

CCR #2, start byte 0, 1 byte transfer

0/1

00

1001

CCR #2, start byte 1, 1 byte transfer

0/1

00

1010

CCR #2, start byte 2, 1 byte transfer

0/1

00

1011

CCR #2, start byte 3, 1 byte transfer

0/1

01

1000

CCR #2, start byte 0, 2 byte transfer

0/1

01

1001

CCR #2, start byte 1, 2 byte transfer

0/1

01

1010

CCR #2, start byte 2, 2 byte transfer

0/1

01

1011

CCR #2, start byte 3, 2 byte transfer

0/1

10

1000

CCR #2, start byte 0, 3 byte transfer

0/1

10

1001

CCR #2, start byte 1, 3 byte transfer

0/1

10

1010

CCR #2, start byte 2, 3 byte transfer

0/1

10

1011

CCR #2, start byte 3, 3 byte transfer

0/1

11

1000

CCR #2, start byte 0, 4 byte transfer

0/1

11

1001

CCR #2, start byte 1, 4 byte transfer

0/1

11

1010

CCR #2, start byte 2, 4 byte transfer

0/1

11

1011

CCR #2, start byte 3, 4 byte transfer

0

xx

1100

Data

RAM

burst

transfer,

least

signicant byte rst, READ ONLY

0

xx

1100

Data

RAM

burst

transfer,

most

signicant byte rst, READ ONLY

0/1

xx

1101

Offset

RAM

burst

transfer,

least

signicant byte rst.

0/1

xx

1101

Offset

RAM

burst

transfer,

most

signicant byte rst.

0/1

xx

1110

Positive full scale RAM burst transfer,

least signicant byte rst.

0/1

xx

1110

Positive full scale RAM burst transfer,

most signicant byte rst.

0/1

xx

1111

Negative full scale RAM burst transfer,

least signicant byte rst.

0/1

xx

1111

Negative full scale RAM burst transfer,

most signicant byte rst.

TABLE 7. INTERNAL REGISTER ADDRESS (Continued)

R/W

IR [7]

NB1,

NB0

IR [6:5]

A3, A2,

A1, A0

IR [3:0]

DESCRIPTION

HI7188

相关PDF资料 |

PDF描述 |

|---|---|

| HI7190IP | IC ADC 24BIT PROGBL SER 20-PDIP |

| HI7191IP | IC ADC 24BIT PROGBL SER 20-PDIP |

| HI9P5701K-5 | CONV A/D 6BIT 30MSPS 18-SOIC |

| HMC700LP4E | IC FRACT-N PLL 16BIT 24QFN |

| HMC703LP4E | IC FRACT-N PLL W/SWEEPR 24QFN |

相关代理商/技术参数 |

参数描述 |

|---|---|

| HI7188IP | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Analog Devices 功能描述:IC 16BIT ADC 7188 DIP40 制造商:Harris Corporation 功能描述: |

| HI7190 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:null24-Bit, High Precision, Sigma Delta A/D Converter |

| HI7190 WAF | 制造商:Harris Corporation 功能描述: |

| HI7190_06 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:24-Bit, High Precision, Sigma Delta A/D Converter |

| HI7190EVAL | 功能描述:EVALUATION PLATFORM HI7190 RoHS:否 类别:编程器,开发系统 >> 评估板 - 模数转换器 (ADC) 系列:- 产品培训模块:Obsolescence Mitigation Program 标准包装:1 系列:- ADC 的数量:1 位数:12 采样率(每秒):94.4k 数据接口:USB 输入范围:±VREF/2 在以下条件下的电源(标准):- 工作温度:-40°C ~ 85°C 已用 IC / 零件:MAX11645 已供物品:板,软件 |

发布紧急采购,3分钟左右您将得到回复。