参数资料

| 型号: | HI7188IN |

| 厂商: | Intersil |

| 文件页数: | 22/24页 |

| 文件大小: | 0K |

| 描述: | CONV A/D 16BIT 8:1 MUX 44-MQFP |

| 标准包装: | 96 |

| 位数: | 16 |

| 采样率(每秒): | 240 |

| 数据接口: | QSPI?,串行,SPI? |

| 转换器数目: | 1 |

| 功率耗散(最大): | 50mW |

| 电压电源: | 模拟和数字,双 ± |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 44-QFP |

| 供应商设备封装: | 44-MQFP(10x10) |

| 包装: | 管件 |

| 输入数目和类型: | 8 个差分,单极;8 个差分,双极 |

7

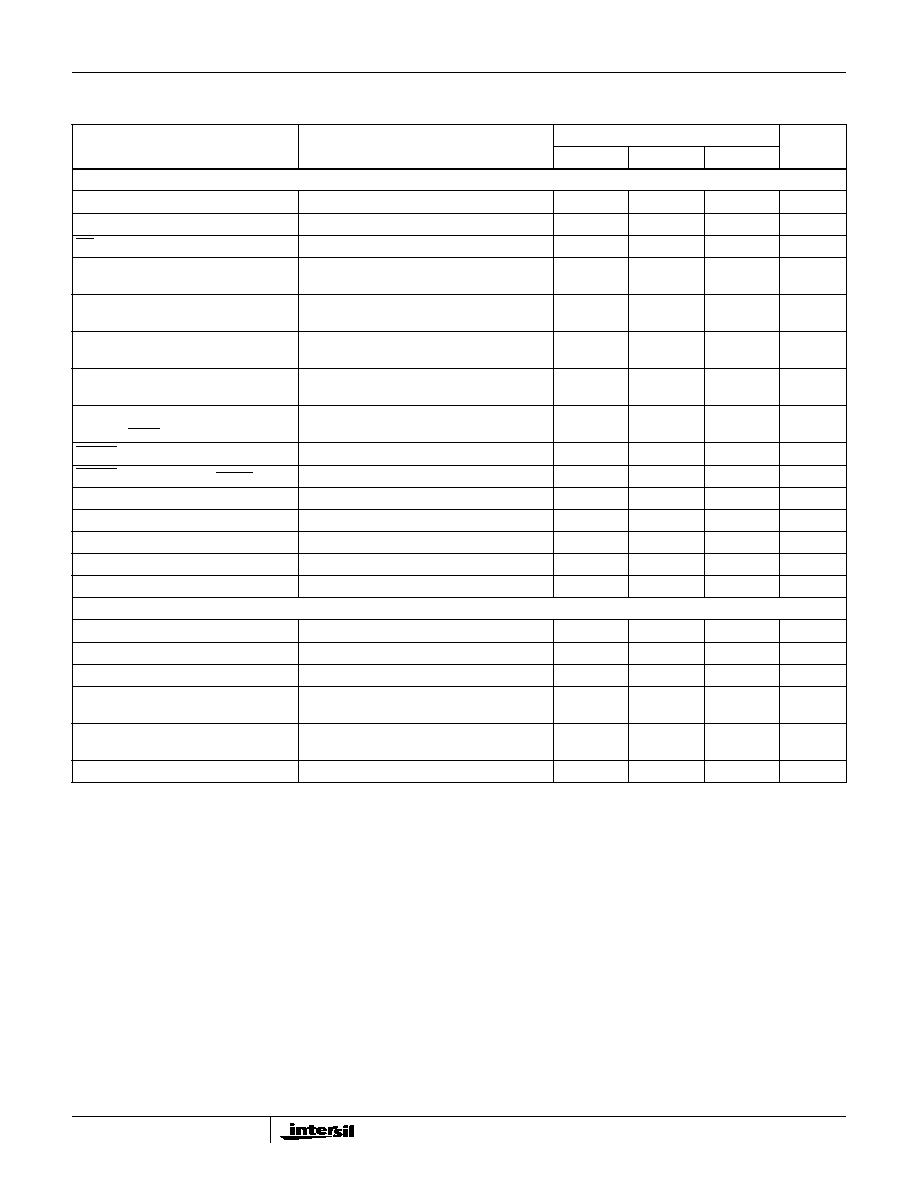

TIMING CHARACTERISTICS

SCLK Minimum Cycle Time, tSCLK

(Notes 2, 7)

200

-

ns

SCLK Minimum Pulse Width, tSCLKPW

(Notes 2, 7)

60

-

ns

CS to SCLK Precharge Time, tPRE

(Notes 2, 7)

50

-

ns

Data Setup to SCLK Rising Edge (Write),

tDSU

(Notes 2, 7)

50

-

ns

Data Hold from SCLK Rising Edge

(Write), tDHLD

(Notes 2, 7)

0

-

ns

Data Read Access from Instruction Byte

Write, tACC

(Notes 2, 7)

-

40

ns

Read Bit Valid from SCLK Falling Edge,

tDV

(Notes 2, 7)

-

40

ns

Last Data Transfer to Data Ready

Inactive, tDRDY

(Notes 2, 7)

-

50

-

ns

RESET Low Pulse Width tRESET

(Notes 2, 7)

100

-

ns

RSTI/O Low Pulse Width tRSTI/O

(Notes 2, 7)

100

-

ns

MUX High Pulse Width tMUX

(Notes 2, 7)

14

-

s

CADDR Valid to MUX High

(Notes 2, 7)

-

75

ns

Oscillator Clock Frequency

(Notes 2, 7)

-

3.6864

-

MHz

Output Rise/Fall Time

(Notes 2, 7)

-

30

ns

Input Rise/Fall Time

(Notes 2, 7)

-

1

s

POWER SUPPLY CHARACTERISTICS

IAVDD

AVDD = +5V, OSC1 = 3.6864MHz (Note 3)

-

1.8

3.0

mA

IAVSS

AVSS = -5V, OSC1 = 3.6864MHz (Note 3)

-

1.8

3.0

mA

IDVDD

DVDD = +5V, SCLK = 4MHz

-

2.0

4.0

mA

Power Dissipation, Active PDA

AVDD = +5V, AVSS = -5V, SLP = ‘0’

(Notes 3, 9)

-28

50

mW

Power Dissipation, Sleep PDS

AVDD = +5V, AVSS = -5V, SLP = ‘1’

(Notes 3, 9)

-5-

mW

PSRR (

Vsupply = 0.25V)

PSRR = 20log (

Vsupply / VOS) (Note 3)

-

75

-

dB

NOTES:

2. Parameter guaranteed by design or characterization, not production tested.

3. DC PSRR is measured on all supplies individually and applies to both Bipolar and Unipolar Input Ranges.

4. These errors can be removed by re-calibrating at the desired operating temperature.

5. Applies after system calibration.

6. Fully differential input signal source is used.

7. See Load Test Circuit, Figure 1, R1 = 10k, CL = 50pF (Includes Stray and Jig Capacitance).

8. For Line Noise Rejection, 3.6864MHz is required to develop internal clocks to reject 50/60Hz.

9. SLP is the sleep mode enable bit defined in bit 3 of the Control Register (CR <3>).

Electrical Specications

AVDD = +5V, AVSS = -5V, DVDD = +5V, VRHI = +2.5V, VRLO = AGND, VCM = AGND, PGIA Gain = 1,

OSCIN = 3.6864MHz, Bipolar Input Range Selected (Continued)

PARAMETER

TEST CONDITION

-40oC TO 85oC

UNITS

MIN

TYP

MAX

HI7188

相关PDF资料 |

PDF描述 |

|---|---|

| HI7190IP | IC ADC 24BIT PROGBL SER 20-PDIP |

| HI7191IP | IC ADC 24BIT PROGBL SER 20-PDIP |

| HI9P5701K-5 | CONV A/D 6BIT 30MSPS 18-SOIC |

| HMC700LP4E | IC FRACT-N PLL 16BIT 24QFN |

| HMC703LP4E | IC FRACT-N PLL W/SWEEPR 24QFN |

相关代理商/技术参数 |

参数描述 |

|---|---|

| HI7188IP | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Analog Devices 功能描述:IC 16BIT ADC 7188 DIP40 制造商:Harris Corporation 功能描述: |

| HI7190 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:null24-Bit, High Precision, Sigma Delta A/D Converter |

| HI7190 WAF | 制造商:Harris Corporation 功能描述: |

| HI7190_06 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:24-Bit, High Precision, Sigma Delta A/D Converter |

| HI7190EVAL | 功能描述:EVALUATION PLATFORM HI7190 RoHS:否 类别:编程器,开发系统 >> 评估板 - 模数转换器 (ADC) 系列:- 产品培训模块:Obsolescence Mitigation Program 标准包装:1 系列:- ADC 的数量:1 位数:12 采样率(每秒):94.4k 数据接口:USB 输入范围:±VREF/2 在以下条件下的电源(标准):- 工作温度:-40°C ~ 85°C 已用 IC / 零件:MAX11645 已供物品:板,软件 |

发布紧急采购,3分钟左右您将得到回复。