参数资料

| 型号: | HI7188IN |

| 厂商: | Intersil |

| 文件页数: | 15/24页 |

| 文件大小: | 0K |

| 描述: | CONV A/D 16BIT 8:1 MUX 44-MQFP |

| 标准包装: | 96 |

| 位数: | 16 |

| 采样率(每秒): | 240 |

| 数据接口: | QSPI?,串行,SPI? |

| 转换器数目: | 1 |

| 功率耗散(最大): | 50mW |

| 电压电源: | 模拟和数字,双 ± |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 44-QFP |

| 供应商设备封装: | 44-MQFP(10x10) |

| 包装: | 管件 |

| 输入数目和类型: | 8 个差分,单极;8 个差分,双极 |

22

CS. Chip Select. This signal is an active low input that allows

more than one device on the same serial communication

lines. The SDO and SDIO will go to a high impedance state

when this signal is high. If driven high during any

communication cycle, that cycle will be suspended until CS

reactivation. Chip select can be tied low in systems that

maintain control of SCLK.

EOS. End Of Scan. Signals the end of a logical channel

scan (all programmed logical channels have been

converted) and data is available for reading. EOS is useful

as an edge or level sensitive interrupt signal to a

microprocessor or microcontroller. EOS low indicates that

new data is available and the Data RAM can be read. EOS

will return high upon completion of a complete Data RAM

read cycle. Please refer to the Data RAM section for details.

CA. Calibration Active. This pin is high if any active logical

channel is in the calibration mode and stays high for the

entire scan period. CA checks only those channels that are

actively being converted on. For example, if the HI7188 is

programmed to convert only two channels and any of the

CCR bytes of the six nonactive channels are in the

calibration mode, CA will NOT go active. The user can

monitor the CA output to determine when all active channels

have completed calibration.

MODE. Mode. This input is used to select between

Synchronous Self Clocking Mode (high) or the Synchronous

External Clocking Mode (low).

RSTI/O. Reset I/O. This active low asynchronous input is

used to reset the serial interface state machine. This reset

only affects the I/O logic and does not affect the Control

Register, Channel Configuration Register or Calibration

RAMs. This effectively aborts any communication cycle

and places the device in a standby mode awaiting the next IR

cycle.

Serial Interface Communication

It is useful to think of the HI7188 interface in terms of

communication cycles. Each communication cycle happens in

2 phases. The first phase is the writing of an instruction byte

while the second phase is the data transfer as described by the

instruction byte. It is important to note that phase 2 of the

communication cycle can be a single byte or a multi-byte

transfer of data including a Burst RAM read/write. It is up to the

user to maintain synchronism with respect to data transfers. If

the system processor “gets lost”, during an I/O operation, the

only way to recover is to reset the Serial Interface via a RSTI/O.

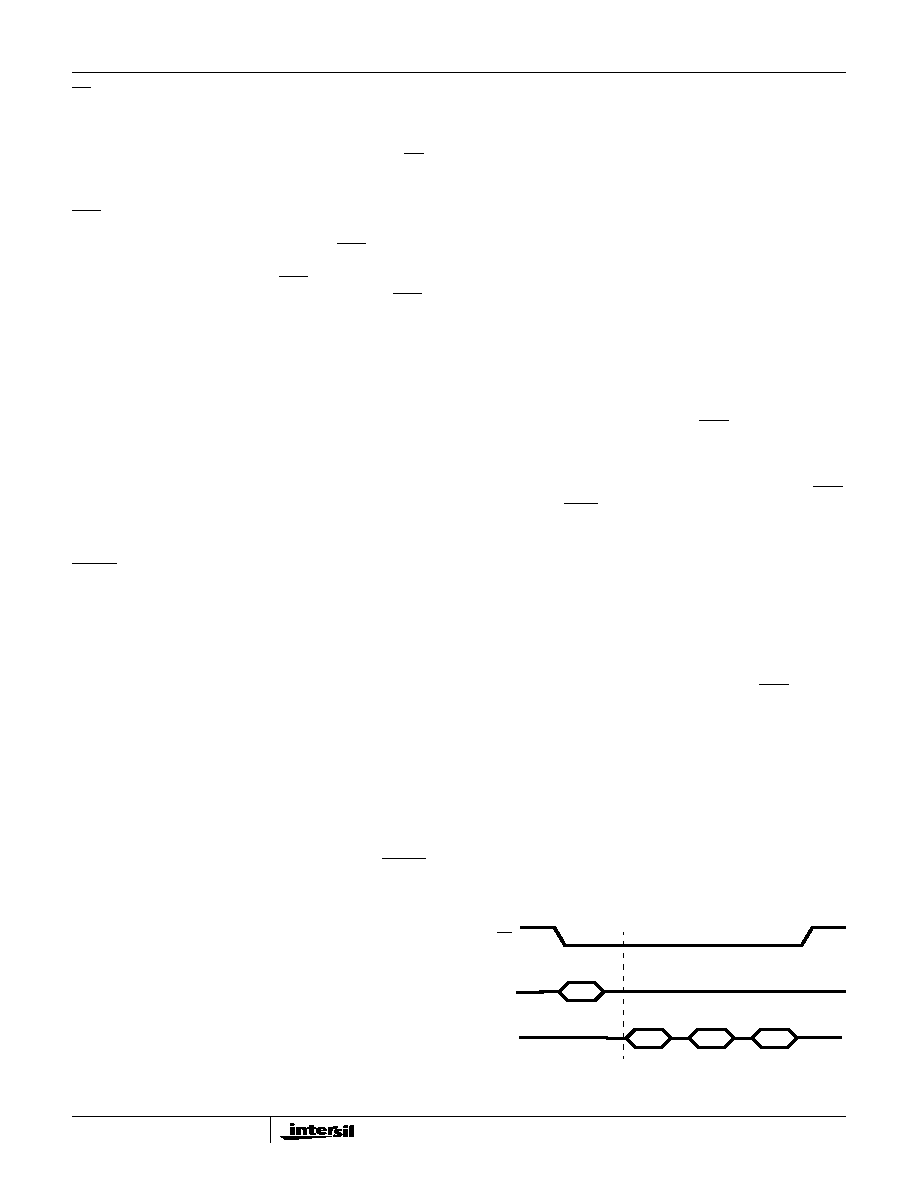

Figure 15 shows both a 2-wire and a 3-wire data transfer.

Instruction Byte Phase

The instruction byte phase initiates a data transfer

sequence. The processor writes an eight bit byte to the

“Instruction Register”, known as the “Instruction Byte”. The

instruction byte informs the HI7188 about the Data cycle

phase activities and includes the following information:

Read or Write Cycle

Number of Bytes to be Transferred

Which Register and Starting Byte to be Accessed

Data Cycle Phase

In the data cycle phase, data transfer takes place as dened

by the Instruction Register Byte. See Write Operation and

Read Operation sections for detailed descriptions. It is

important to note that phase 2 of the communication cycle

can be a multi-byte transfer of data.

For example, the 4 byte Channel Configuration register can be

read using one multi-byte communication cycle rather than four

single byte communication cycles. After phase 2 is completed

the HI7188 I/O logic enters a standby mode while waiting to

receive a new instruction byte. It is up to the user to maintain

synchronism with respect to data transfers. If the system

processor “gets lost” the only way to recover is to reset the

HI7188.

Serial Interface Format

Several formats are available for reading from and writing to

the HI7188 registers in both the 2-wire and 3-wire protocols.

Please refer to Figure 15. A portion of these formats is

controlled by the CR<2:1> (BD and MSB) bits which control

the byte direction and bit order of a data transfer

respectively. These two bits can be written in any

combination but only the two most useful will be discussed

here. The rst combination is to reset both the BD and MSB

bits (BD = 0, MSB = 0). This sets up the interface for

descending byte order and MSB rst format. When this

combination is used the user should always write the

instruction register such that the starting byte is the most

signicant byte address. For example, read three bytes of

data starting with the most significant byte. The first byte

read will be the most significant in MSB to LSB format. The

next byte will be the next least significant (recall descending

byte order) again in MSB to LSB order. The last byte will be

the next lesser significant byte in MSB to LSB order. THE

ENTIRE WORD WAS READ MSB TO LSB format. The

second combination is to set both the BD and MSB bits to 1.

This sets up the interface for ascending byte order and LSB

rst format. When this combination is used the user should

always write the instruction register such that the starting

byte is the least signicant byte address. For example, read

three bytes of data starting with the least signicant byte.

The rst byte read will be the least signicant in LSB to MSB

format. The next byte will be the next greater signicant

(recall ascending byte order) again in LSB to MSB order.

The last byte will be the next greater signicant byte in LSB

to MSB order. THE ENTIRE WORD WAS READ LSB TO

MSB format. After completion of each communication cycle,

The HI7188 interface enters a standby mode while waiting to

receive a new instruction byte.

INSTRUCTION

BYTE

DATA

BYTE 1

DATA

BYTE 2

DATA

BYTE 3

INSTRUCTION

DATA CYCLE

CYCLE

CS

SDIO

SDO

FIGURE 15. 3-WIRE, 3 BYTE READ TRANSFER

HI7188

相关PDF资料 |

PDF描述 |

|---|---|

| HI7190IP | IC ADC 24BIT PROGBL SER 20-PDIP |

| HI7191IP | IC ADC 24BIT PROGBL SER 20-PDIP |

| HI9P5701K-5 | CONV A/D 6BIT 30MSPS 18-SOIC |

| HMC700LP4E | IC FRACT-N PLL 16BIT 24QFN |

| HMC703LP4E | IC FRACT-N PLL W/SWEEPR 24QFN |

相关代理商/技术参数 |

参数描述 |

|---|---|

| HI7188IP | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Analog Devices 功能描述:IC 16BIT ADC 7188 DIP40 制造商:Harris Corporation 功能描述: |

| HI7190 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:null24-Bit, High Precision, Sigma Delta A/D Converter |

| HI7190 WAF | 制造商:Harris Corporation 功能描述: |

| HI7190_06 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:24-Bit, High Precision, Sigma Delta A/D Converter |

| HI7190EVAL | 功能描述:EVALUATION PLATFORM HI7190 RoHS:否 类别:编程器,开发系统 >> 评估板 - 模数转换器 (ADC) 系列:- 产品培训模块:Obsolescence Mitigation Program 标准包装:1 系列:- ADC 的数量:1 位数:12 采样率(每秒):94.4k 数据接口:USB 输入范围:±VREF/2 在以下条件下的电源(标准):- 工作温度:-40°C ~ 85°C 已用 IC / 零件:MAX11645 已供物品:板,软件 |

发布紧急采购,3分钟左右您将得到回复。