参数资料

| 型号: | HI7188IN |

| 厂商: | Intersil |

| 文件页数: | 20/24页 |

| 文件大小: | 0K |

| 描述: | CONV A/D 16BIT 8:1 MUX 44-MQFP |

| 标准包装: | 96 |

| 位数: | 16 |

| 采样率(每秒): | 240 |

| 数据接口: | QSPI?,串行,SPI? |

| 转换器数目: | 1 |

| 功率耗散(最大): | 50mW |

| 电压电源: | 模拟和数字,双 ± |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 44-QFP |

| 供应商设备封装: | 44-MQFP(10x10) |

| 包装: | 管件 |

| 输入数目和类型: | 8 个差分,单极;8 个差分,双极 |

5

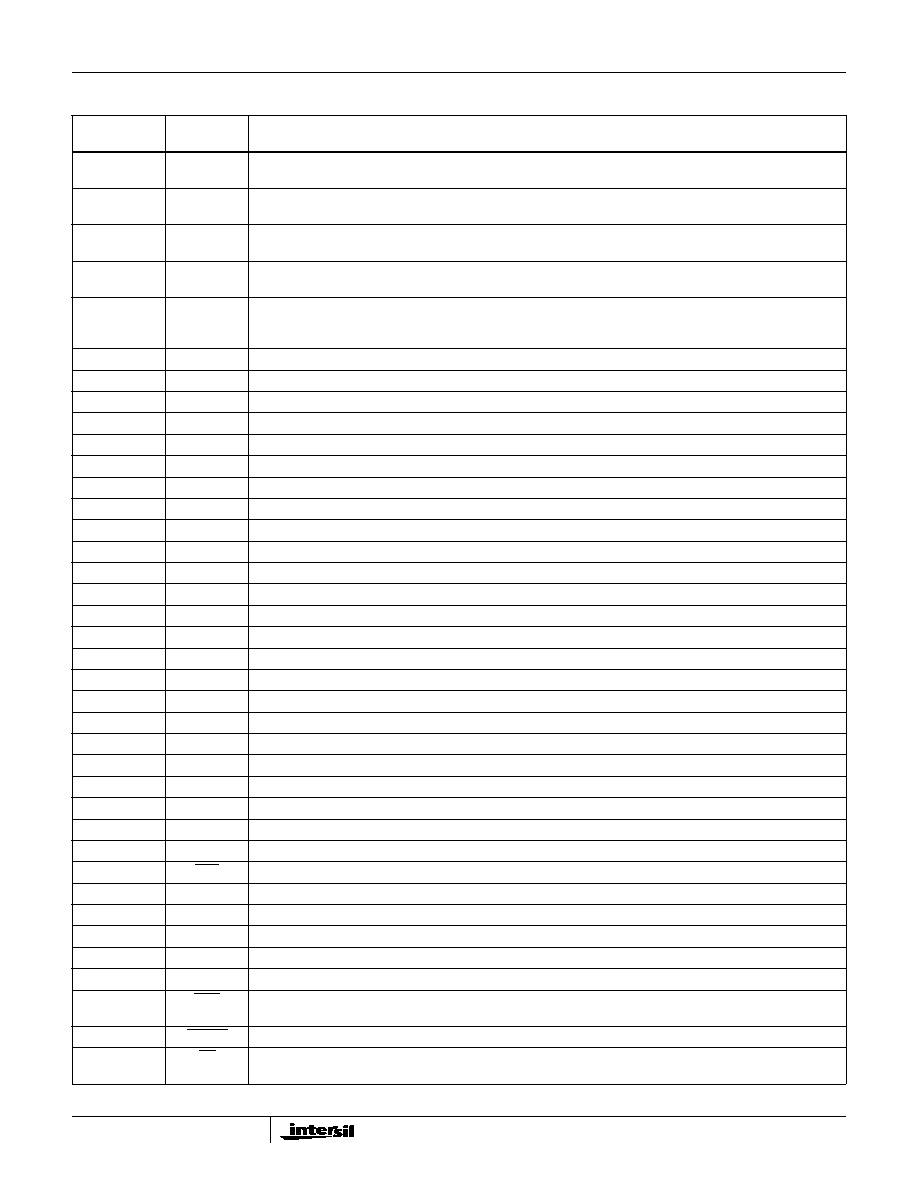

Pin Descriptions

44 LEAD

MQFP

PIN NAME

PIN DESCRIPTION

41

MODE

Mode input. Used to select between Synchronous Self Clocking (MODE = 1) or Synchronous External Clocking

(MODE = 0) for the Serial Port.

42

SCLK

Serial interface clock. Synchronizes serial data transfers. Data is input on the rising edge and output on the falling

edge.

43

SDO

Serial Data Out. Serial data is read from this line when using a 3-wire serial protocol such as the Motorola Serial

Peripheral Interface.

44

SDIO

Serial Data IN or OUT. This line is bidirectional programmable and interfaces directly to the Intel Standard Serial

Interface using a 2-wire serial protocol.

1

OSC1

Oscillator clock input for the device. A crystal connected between OSC1 and OSC2 will provide a clock to the

device, or an external oscillator can drive OSC1. The oscillator frequency should be 3.6864MHz to maintain Line

Noise Rejection.

2

OSC2

Used to connect a crystal source between OSC1 and OSC2. Leave open otherwise.

3, 30

DVDD

Positive Digital supply (+5V).

4, 29, 39

DGND

Digital supply ground.

5, 6, 27, 28

AVSS

Negative analog power supply (-5V).

7VINL1

Analog input low for Channel 1.

8VINH1

Analog input high for Channel 1.

9VINL2

Analog input low for Channel 2.

10

VINH2

Analog input high for Channel 2.

11

VINL3

Analog input low for Channel 3.

12

VINH3

Analog input high for Channel 3.

13

VINL4

Analog input low for Channel 4.

14

VINH4

Analog input high for Channel 4.

15

VINL5

Analog input low for Channel 5.

16

VINH5

Analog input high for Channel 5.

17

VINL6

Analog input low for Channel 6.

18

VINH6

Analog input high for Channel 6.

19

VINL7

Analog input low for Channel 7.

20

VINH7

Analog input high for Channel 7.

21

VINL8

Analog input low for Channel 8.

22

VINH8

Analog input high for Channel 8.

23

VCM

Common mode voltage. Must be tied to the mid point of AVDD and AVSS.

24

VRLO

External reference input. Should be negative referenced to VRHI.

25

VRHI

External reference input. Should be positive referenced to VRLO.

26

AVDD

Positive analog power supply (+5V).

31

RST

Active low Reset pin. Used to initialize modulator, lter, RAMs, registers and state machines.

32

CA

Calibration active output. Indicates that at least one active channel is in a calibration mode.

33

MXC

Multiplexer control output. Indicates that the conversion for the active channel is complete.

34

A0

Logical channel count output (LSB).

35

A1

Logical channel count output.

36

A2

Logical channel count output (MSB).

37

EOS

End of scan output. Signals the end of a channel scan (all active channels have been converted) and data is

available to be read. Remains low until data RAM is read.

38

RSTI/O

I/O reset (active low) input. Resets serial interface state machine only.

40

CS

Active low chip select pin. Used to select a serial data transfer cycle. When high the SDO and SDIO pins are

three-state.

HI7188

相关PDF资料 |

PDF描述 |

|---|---|

| HI7190IP | IC ADC 24BIT PROGBL SER 20-PDIP |

| HI7191IP | IC ADC 24BIT PROGBL SER 20-PDIP |

| HI9P5701K-5 | CONV A/D 6BIT 30MSPS 18-SOIC |

| HMC700LP4E | IC FRACT-N PLL 16BIT 24QFN |

| HMC703LP4E | IC FRACT-N PLL W/SWEEPR 24QFN |

相关代理商/技术参数 |

参数描述 |

|---|---|

| HI7188IP | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Analog Devices 功能描述:IC 16BIT ADC 7188 DIP40 制造商:Harris Corporation 功能描述: |

| HI7190 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:null24-Bit, High Precision, Sigma Delta A/D Converter |

| HI7190 WAF | 制造商:Harris Corporation 功能描述: |

| HI7190_06 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:24-Bit, High Precision, Sigma Delta A/D Converter |

| HI7190EVAL | 功能描述:EVALUATION PLATFORM HI7190 RoHS:否 类别:编程器,开发系统 >> 评估板 - 模数转换器 (ADC) 系列:- 产品培训模块:Obsolescence Mitigation Program 标准包装:1 系列:- ADC 的数量:1 位数:12 采样率(每秒):94.4k 数据接口:USB 输入范围:±VREF/2 在以下条件下的电源(标准):- 工作温度:-40°C ~ 85°C 已用 IC / 零件:MAX11645 已供物品:板,软件 |

发布紧急采购,3分钟左右您将得到回复。