- 您现在的位置:买卖IC网 > PDF目录98009 > MAX14830ETM+ (MAXIM INTEGRATED PRODUCTS INC) SERIAL COMM CONTROLLER, QCC48 PDF资料下载

参数资料

| 型号: | MAX14830ETM+ |

| 厂商: | MAXIM INTEGRATED PRODUCTS INC |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | SERIAL COMM CONTROLLER, QCC48 |

| 封装: | 7 X 7 MM, ROHS COMPLIANT, TQFN-48 |

| 文件页数: | 26/68页 |

| 文件大小: | 2356K |

| 代理商: | MAX14830ETM+ |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页当前第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页

MAX14830

Quad Serial UART with 128-Word FIFOs

and Internal Oscillator

32

ISR—Interrupt Status Register

The Interrupt Status Register provides an overview of all interrupts generated in the MAX14830. These interrupts are

cleared upon reading the ISR. When the MAX14830 is operated in polled mode, the ISR can be polled to establish

the UART’s status. In interrupt-driven mode, IRQ interrupts are enabled through the appropriate IRQEn bits. The ISR

contents give direct information on the cause for the interrupt or point to other registers that contain more detailed

information.

Bit 7: CTSInt

The CTSInt is set when a logic state transition occurs at the CTS_ input. This bit is cleared after ISR is read. The current

logic state of the CTS_ input can be read out through LSR[7]: CTS bit.

Bit 6: RFifoEmptyInt

The RFifoEmptyInt is set when the Receive FIFO is empty. This bit is cleared after ISR is read. Its meaning can be

inverted by setting the MODE2[3]: RxEmtyInt bit.

Bit 5: TFifoEmptyInt

The TFifoEmptyInt bit is set when the Transmit FIFO is empty. This bit is cleared once ISR is read.

Bit 4: TFifoTrigInt

The TFifoTrigInt bit is set when the number of characters in the Transmit FIFO is equal to or greater than the Transmit

FIFO trigger level defined in FIFOTrigLvl[3:0]. TFifoTrigInt is cleared when the Transmit FIFO level falls below the trigger

level or after the ISR is read. It can be used as a warning that the Transmit FIFO is nearing overflow.

Bit 3: RFifoTrigInt

The RFifoTrigInt bit is set when the Receive FIFO fill level reaches the Receive FIFO trigger level, as defined in

FIFOTrigLvl[7:4]. This can be used as an indication that the Receive FIFO is nearing overrun. It can also be used to

report that a known number of words are available that can be read out in one block. The meaning of RFifoTrigInt can

be inverted through MODE2[2]. RFifoTrigInt is cleared when ISR is read.

Bit 2: STSInt

The STSInt bit is set high when any bit in the STSInt register that is enabled through a STSIntEn bit is high. The STSInt

bit is cleared upon reading ISR.

Bit 1: SpCharInt

The SpCharInt bit is set high when a special character is received, a line BREAK is detected or an address character is

received in multidrop mode. The cause for the SpCharInt interrupt can be read from the SpclCharInt register, if enabled

through the SpclChrIntEn bits. The SpCharInt interrupt is cleared when the ISR is read.

Bit 0: LSRErrInt

The LSRErrInt bit is set high when any LSR bits, which are enabled through the LSRIntEn, are set. This bit is cleared

after the ISR is read.

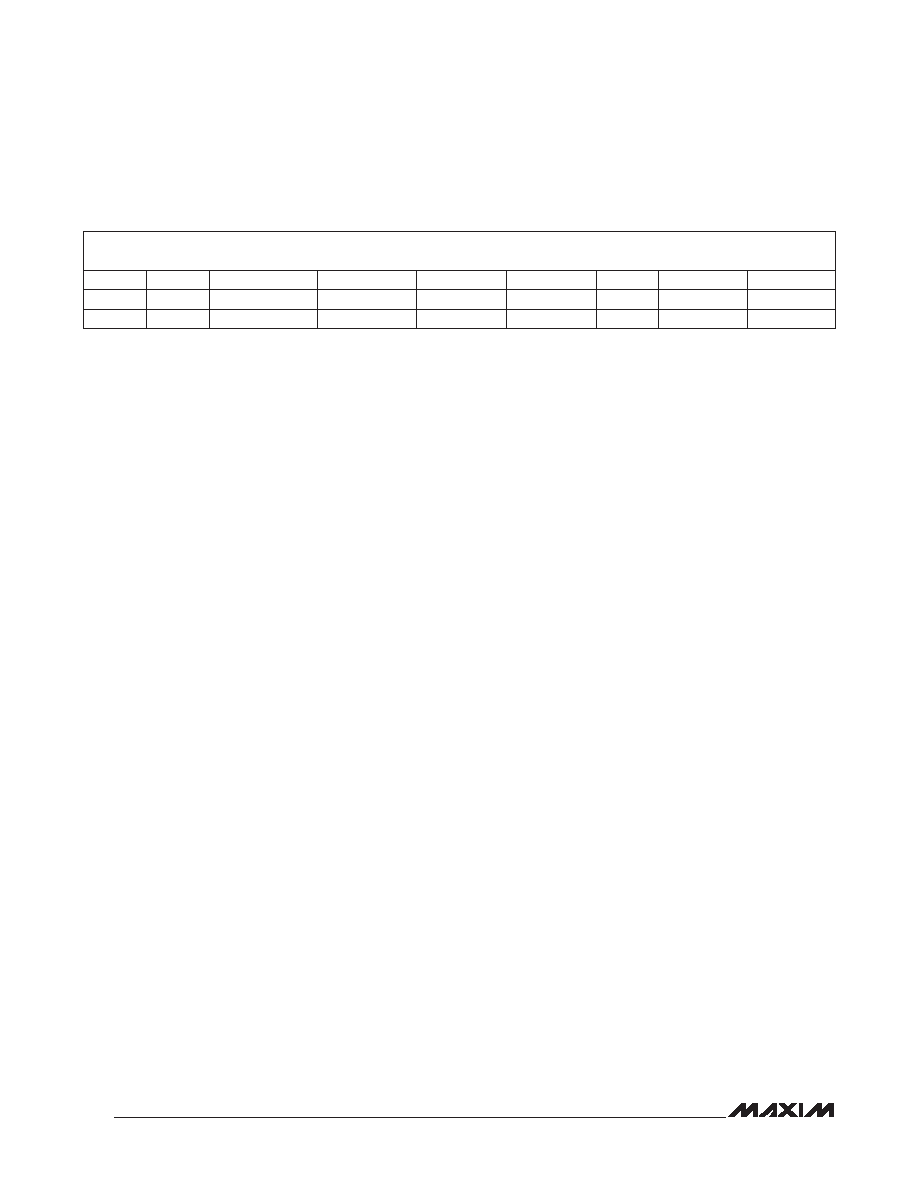

ADDRESS:

0x02

MODE:

COR

BIT

7

6

5

4

3

2

1

0

NAME

CTSInt

RFifoEmptyInt

TFifoEmptyInt

TFifoTrigInt

RFifoTrigInt

STSInt

SpCharInt

LSRErrInt

RESET

0

1

0

相关PDF资料 |

PDF描述 |

|---|---|

| MAX3624AETJ+ | 312.5 MHz, OTHER CLOCK GENERATOR, QCC32 |

| MAX3638ETM+ | 800 MHz, OTHER CLOCK GENERATOR, QCC48 |

| MAX3679CTJ+ | 625 MHz, OTHER CLOCK GENERATOR, QCC32 |

| MAX7329AUP+ | 8 I/O, PIA-GENERAL PURPOSE, PDSO20 |

| MAX7329AAP+ | 8 I/O, PIA-GENERAL PURPOSE, PDSO20 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MAX14830ETM+ | 功能描述:UART 接口集成电路 Quad Serial UART w/128-Word FIFOs RoHS:否 制造商:Texas Instruments 通道数量:2 数据速率:3 Mbps 电源电压-最大:3.6 V 电源电压-最小:2.7 V 电源电流:20 mA 最大工作温度:+ 85 C 最小工作温度:- 40 C 封装 / 箱体:LQFP-48 封装:Reel |

| MAX14830ETM+T | 功能描述:UART 接口集成电路 Quad Serial UART w/128-Word FIFOs RoHS:否 制造商:Texas Instruments 通道数量:2 数据速率:3 Mbps 电源电压-最大:3.6 V 电源电压-最小:2.7 V 电源电流:20 mA 最大工作温度:+ 85 C 最小工作温度:- 40 C 封装 / 箱体:LQFP-48 封装:Reel |

| MAX14830EVKIT# | 功能描述:界面开发工具 MAX14830 Eval Kit RoHS:否 制造商:Bourns 产品:Evaluation Boards 类型:RS-485 工具用于评估:ADM3485E 接口类型:RS-485 工作电源电压:3.3 V |

| MAX14830EVKIT+ | 制造商:Maxim Integrated Products 功能描述:QUAD UART EV-KIT WITH IO-LINK AND MULTIPROTOCOL - Boxed Product (Development Kits) |

| MAX1483C/D+ | 功能描述:RS-485接口IC low-power transceivers for RS-485 and RS-422 communication RoHS:否 制造商:Texas Instruments 数据速率:250 Kbps 工作电源电压:3.3 V 电源电流:750 uA 工作温度范围:- 40 C to + 125 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-8 封装:Tube |

发布紧急采购,3分钟左右您将得到回复。