- 您现在的位置:买卖IC网 > PDF目录189002 > NAND256W3A2CZA1E (NUMONYX) 32M X 8 FLASH 3V PROM, 35 ns, PBGA55 PDF资料下载

参数资料

| 型号: | NAND256W3A2CZA1E |

| 厂商: | NUMONYX |

| 元件分类: | PROM |

| 英文描述: | 32M X 8 FLASH 3V PROM, 35 ns, PBGA55 |

| 封装: | 8 X 10 MM, 1 MM HEIGHT, 0.80 MM PITCH, ROHS COMPLIANT, VFBGA-55 |

| 文件页数: | 9/57页 |

| 文件大小: | 916K |

| 代理商: | NAND256W3A2CZA1E |

第1页第2页第3页第4页第5页第6页第7页第8页当前第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页

17/57

NAND128-A, NAND256-A, NAND512-A, NAND01G-A

BUS OPERATIONS

There are six standard bus operations that control

the memory. Each of these is described in this

section, see Table 5., Bus Operations, for a sum-

mary.

Command Input

Command Input bus operations are used to give

commands to the memory. Command are accept-

ed when Chip Enable is Low, Command Latch En-

able is High, Address Latch Enable is Low and

Read Enable is High. They are latched on the ris-

ing edge of the Write Enable signal.

Only I/O0 to I/O7 are used to input commands.

See Figure 23. and Table 20. for details of the tim-

ings requirements.

Address Input

Address Input bus operations are used to input the

memory address. Three bus cycles are required to

input the addresses for the 128Mb and 256Mb de-

vices and four bus cycles are required to input the

addresses for the 512Mb and 1Gb devices (refer

The addresses are accepted when Chip Enable is

Low, Address Latch Enable is High, Command

Latch Enable is Low and Read Enable is High.

They are latched on the rising edge of the Write

Enable signal. Only I/O0 to I/O7 are used to input

addresses.

See Figure 24. and Table 20. for details of the tim-

ings requirements.

Data Input

Data Input bus operations are used to input the

data to be programmed.

Data is accepted only when Chip Enable is Low,

Address Latch Enable is Low, Command Latch

Enable is Low and Read Enable is High. The data

is latched on the rising edge of the Write Enable

signal. The data is input sequentially using the

Write Enable signal.

tails of the timings requirements.

Data Output

Data Output bus operations are used to read: the

data in the memory array, the Status Register, the

Electronic Signature and the Serial Number.

Data is output when Chip Enable is Low, Write En-

able is High, Address Latch Enable is Low, and

Command Latch Enable is Low.

The data is output sequentially using the Read En-

able signal.

See Figure 26. and Table 21. for details of the tim-

ings requirements.

Write Protect

Write Protect bus operations are used to protect

the memory against program or erase operations.

When the Write Protect signal is Low the device

will not accept program or erase operations and so

the contents of the memory array cannot be al-

tered. The Write Protect signal is not latched by

Write Enable to ensure protection even during

power-up.

Standby

When Chip Enable is High the memory enters

Standby mode, the device is deselected, outputs

are disabled and power consumption is reduced.

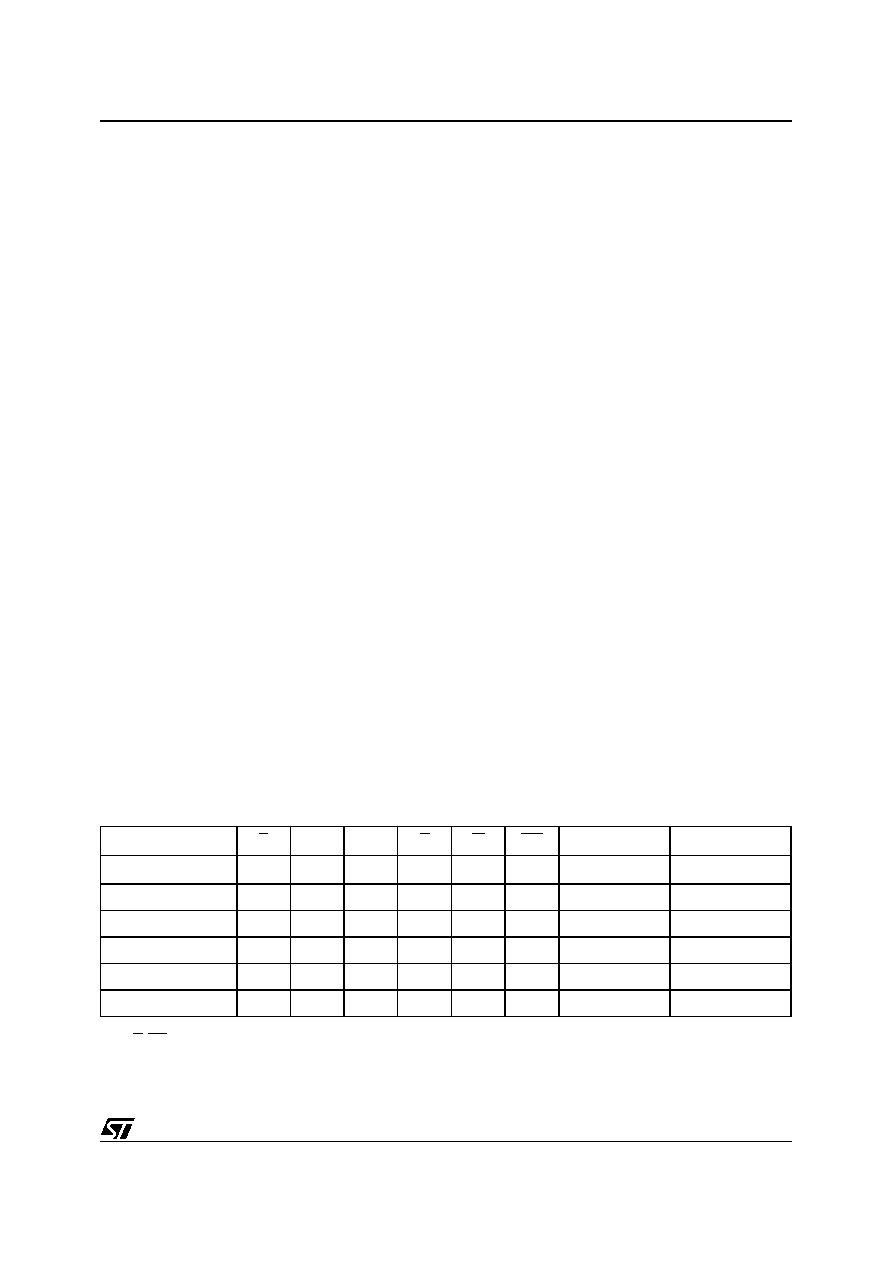

Table 5. Bus Operations

Note: 1. Only for x16 devices.

2. WP must be VIH when issuing a program or erase command.

Bus Operation

E

AL

CL

R

W

WP

I/O0 - I/O7

I/O8 - I/O15(1)

Command Input

VIL

VIH

Rising

X(2)

Command

X

Address Input

VIL

VIH

VIL

VIH

Rising

X

Address

X

Data Input

VIL

VIH

Rising

X

Data Input

Data Output

VIL

Falling

VIH

X

Data Output

Write Protect

X

VIL

XX

Standby

VIH

XX

X

相关PDF资料 |

PDF描述 |

|---|---|

| NAND01GR4A2AZB6 | 64M X 16 FLASH 1.8V PROM, 35 ns, PBGA63 |

| NAND01GW3B2CN1E | 128M X 8 FLASH 3V PROM, 25000 ns, PDSO48 |

| NAND04GR3B3AN6 | 512M X 8 FLASH 1.8V PROM, 35 ns, PDSO48 |

| NAND512W3B3BZA1F | 64M X 8 FLASH 3V PROM, 35 ns, PBGA63 |

| NAND512W3B3CV1 | 64M X 8 FLASH 3V PROM, 35 ns, PDSO48 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| NAND256W4A0AN6E | 功能描述:闪存 NAND & S.MEDIA FLASH RoHS:否 制造商:ON Semiconductor 数据总线宽度:1 bit 存储类型:Flash 存储容量:2 MB 结构:256 K x 8 定时类型: 接口类型:SPI 访问时间: 电源电压-最大:3.6 V 电源电压-最小:2.3 V 最大工作电流:15 mA 工作温度:- 40 C to + 85 C 安装风格:SMD/SMT 封装 / 箱体: 封装:Reel |

| NAND32GAH0HZA5E | 制造商:Micron Technology Inc 功能描述:NAND EMMC - Trays |

| NAND32GAH0HZA5F | 制造商:Micron Technology Inc 功能描述:NAND EMMC - Tape and Reel |

| NAND32GAH0PZA5E | 制造商:Micron Technology Inc 功能描述:EMMC 4.3 4GB 12X16 41NM - Trays |

| NAND32GAH0PZA5F | 制造商:Micron Technology Inc 功能描述:NAND EMMC - Tape and Reel |

发布紧急采购,3分钟左右您将得到回复。