- 您现在的位置:买卖IC网 > PDF目录367934 > PH28F640L18T85 (INTEL CORP) StrataFlash Wireless Memory PDF资料下载

参数资料

| 型号: | PH28F640L18T85 |

| 厂商: | INTEL CORP |

| 元件分类: | PROM |

| 英文描述: | StrataFlash Wireless Memory |

| 中文描述: | 4M X 16 FLASH 1.8V PROM, 85 ns, PBGA56 |

| 封装: | 0.75 MM PITCH, LEAD FREE, VFBGA-56 |

| 文件页数: | 74/106页 |

| 文件大小: | 1272K |

| 代理商: | PH28F640L18T85 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页当前第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页

Intel StrataFlash Wireless Memory (L18)

April 2005

74

Intel StrataFlash Wireless Memory (L18)

Order Number: 251902, Revision: 009

Datasheet

To read data from a block in other partition and the other partition already in read array mode, a

new block address must be issued. However, if the other partition is

not

already in read array mode,

issuing a read array command will cause the buffered program operation to abort and a command

sequence error would be posted in the Status Register. See

Figure 41, “Buffer Program Flowchart”

on page 87

for more details.

Note:

Simultaneous read-while-Buffered EFP is not supported.

14.3

Simultaneous Operation Restrictions

Since the Intel StrataFlash Wireless Memory (L18) supports simultaneous read from one

partition while programming or erasing in another partition, certain features like the Protection

Registers and CFI Query data have special requirements with respect to simultaneous operation

capability. (

Table 15

provides details on restrictions during simultaneous operations.)

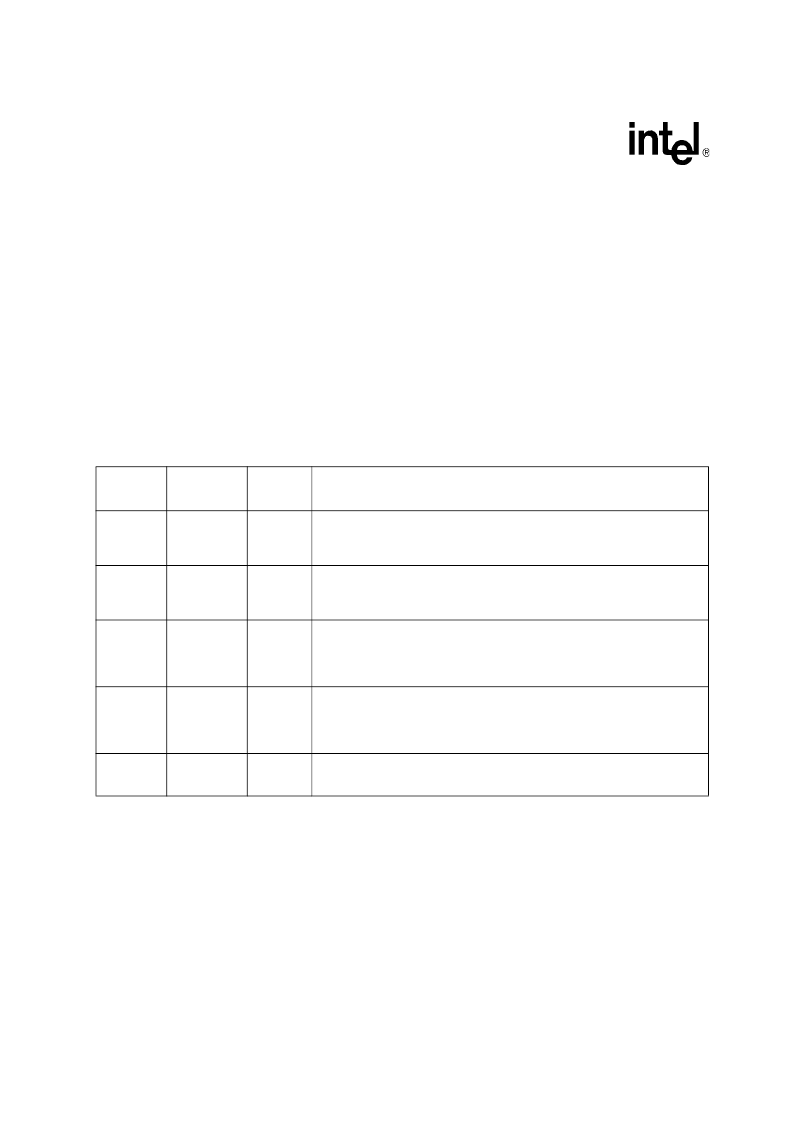

Table 15.

Simultaneous Operation Restrictions

Protection

Register or

CFI data

Parameter

Partition

Array Data

Other

Partitions

Notes

Read

(See Notes)

Write/Erase

While programming or erasing in a main partition, the Protection Register or CFI

data may be read from any other partition.

Reading the parameter partition array data is not allowed if the Protection Register

or Query data is being read from addresses within the parameter partition.

While programming or erasing in a main partition, read operations are allowed in the

parameter partition.

Accessing the Protection Registers or CFI data from parameter partition addresses

is not allowed when reading array data from the parameter partition.

While programming or erasing in a main partition, read operations are allowed in the

parameter partition.

Accessing the Protection Registers or CFI data in a partition that is

different

from the

one being programed/erased, and also

different

from the parameter partition is

allowed.

While programming the Protection Register, reads are only allowed in the other

main partitions.

Access to array data in the parameter partition is not allowed. Programming of the

Protection Register can only occur in the parameter partition, which means this

partition is in Read Status.

While programming or erasing the parameter partition, reads of the Protection

Registers or CFI data are not allowed in

any

partition.

Reads in partitions other than the parameter partition are supported.

(See Notes)

Read

Write/Erase

Read

Read

Write/Erase

Write

No Access

Allowed

Read

No Access

Allowed

Write/Erase

Read

相关PDF资料 |

PDF描述 |

|---|---|

| PH2907A | PNP switching transistor |

| PH2907 | PNP switching transistor |

| PH2931-135S | Rail-to-Rail, Very Low Noise Universal Dual Filter Building Block; Package: SO; No of Pins: 16; Temperature Range: -40°C to +85°C |

| PH2931-I3 | Radar Pulsed Power Transistor, 135W, 20ms Pulse, 1% Duty 2.9 - 3.1 GHz |

| PH2931-20M | Radar Pulsed Power Transistor, 20W,100ms Pulse, 10% Duty 2.9-3.1 GHz |

相关代理商/技术参数 |

参数描述 |

|---|---|

| PH28F640W18BD60 | 制造商:Micron Technology Inc 功能描述:PH28F640W18BD60S L785 |

| PH28F640W18BD60B | 制造商:Micron Technology Inc 功能描述:NUMPH28F640W18BD60B PH28F640W18BD60S L78 |

| PH28F640W18TE60B | 制造商:Micron Technology Inc 功能描述:64MB, CRYSTAL .75 VFBGA 1.8 LF - Tape and Reel |

| PH28F640W30BD70A | 制造商:Micron Technology Inc 功能描述:NOR Flash Parallel/Serial 1.8V 64Mbit 4M x 16bit 70ns 56-Pin VFBGA Tray 制造商:Micron Technology Inc 功能描述:NUMPH28F640W30BD70A MM#862859FLASH 28F64 |

| PH2-8-SGA | 制造商:Adam Technologies Inc 功能描述:PH2 Series Dual Row 8 Position Straight 2.54 mm Centerline Pin Header |

发布紧急采购,3分钟左右您将得到回复。