- 您现在的位置:买卖IC网 > PDF目录98069 > S1R72803F00A100 1 CHANNEL(S), 400M bps, SERIAL COMM CONTROLLER, PQFP100 PDF资料下载

参数资料

| 型号: | S1R72803F00A100 |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 1 CHANNEL(S), 400M bps, SERIAL COMM CONTROLLER, PQFP100 |

| 封装: | 0.40 MM PITCH, PLASTIC, QFP20-184 |

| 文件页数: | 67/115页 |

| 文件大小: | 833K |

| 代理商: | S1R72803F00A100 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页当前第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页

S1R72803F00A

EPSON

51

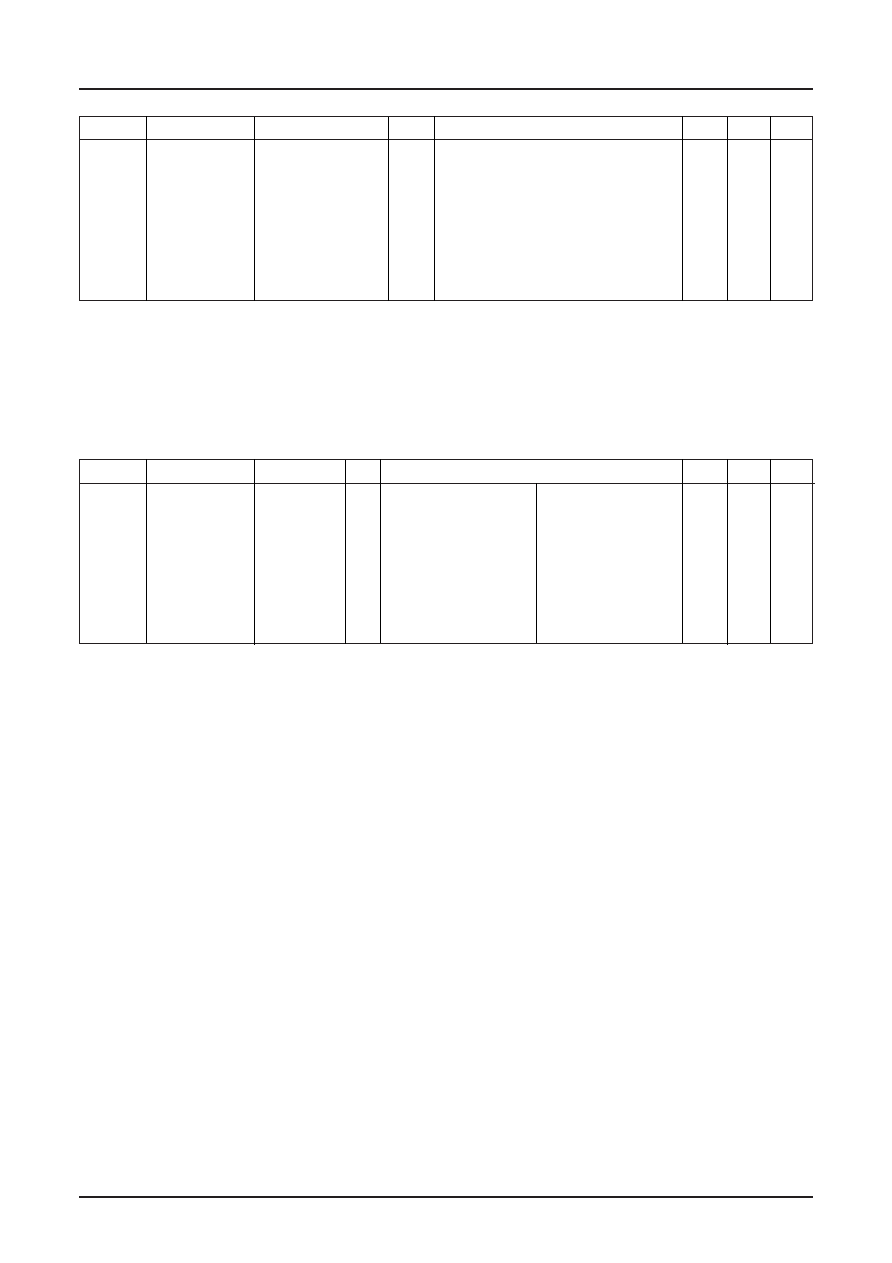

Address Register Name

Bit Symbol

R/W

Description

H.Rst S.Rst B.Rst

0x11

HW_Revision

7: HW_Revision[7]

6: HW_Revision[6]

5: HW_Revision[5]

4: HW_Revision[4]

R

Indicate Hard Ware Revison Number

0x03

3: HW_Revision[3]

2: HW_Revision[2]

1: HW_Revision[1]

0: HW_Revision[0]

Hardware Revision Register

The HW_Revision Register indicates the revision number of a chip.

Address Register Name

Bit Symbol

R/W

Description

H.Rst S.Rst B.Rst

0x18

LinkCtl_H

7: PassSelfID

0: Non PassSelfID

1: Self–ID to DMA FIFO

6: PassPhyPkt

0: Non Pass PHY Packet

1: PHY Pkt to DMA FIFO

5: PassBrPkt

0: Non Pass BusRst Packet

1: BusRst Pkt to DMA FIFO

4: EnPosWB

R/W 0: Disable Posted WB

1: Enable Posted WB

0x00

–

3: EnPosWQ

0: Disable Poosted WQ

1: Enable Posted WQ

2: APHY

0: PHY 1394.a uncorrespond 1: PHY 1394.a correspond

1: EnAcc

0: Ack Acceleration Disable 1: Ack Acceleration Enable

0: Cmstr

0: Cycle Master Not Capabl 1: Cycle Master Capable

LINK Core Control Register Higher Rank

This register controls the functions of the LINK core.

Bit7 Pass Self-ID Packet

Setting this bit to “1” captures a Self-ID packet received by the LINK core into the buffer.

Bit6 Pass PHY Packet

When requesting the PHY Register for a register write, this bit is set to “1”. After the execution, this bit is

cleared.

Bit5 Pass BusReset Packet

Setting this bit to “1” captures a BusReset packet received by the LINK core into the buffer.

Bit4 Enable Posted Block Write

Setting this bit to “1” enables the Posted Write function for a Block Write Request.

Bit3 Enable Posted Quadlet Write

Setting this bit to “1” enables the Posted Write function for a Quadlet Write Request.

Bit2 APHY

Indicates whether the PHY conforms to 1394.a or not.

1: Conforms to PHY 1394.a

0: Does not conform to PHY 1394.a

Bit1 Enable Ack Acceleration

Indicates the setting of Ack Acceleration.

1: Ack Acceleration enable

0: Ack Acceleration disable

Bit0 cmstr

When the self node is Cycle Master capable and a root, this bit becomes “1”.

If the self node does not become a root in the Self-ID processing when this bit is set after the Bus Reset, this

bit is cleared.

相关PDF资料 |

PDF描述 |

|---|---|

| S1R72C05B08 | UNIVERSAL SERIAL BUS CONTROLLER, PBGA121 |

| S1R72C05B10 | UNIVERSAL SERIAL BUS CONTROLLER, PBGA121 |

| S1R72V17B00A | UNIVERSAL SERIAL BUS CONTROLLER, PBGA60 |

| S1R72V18B10 | UNIVERSAL SERIAL BUS CONTROLLER, PBGA121 |

| S1R72V27B05 | UNIVERSAL SERIAL BUS CONTROLLER, PBGA60 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| S1R72803F00A200 | 功能描述:IC LINK CTRLR 1394 IDE-66 184QFP RoHS:否 类别:集成电路 (IC) >> 接口 - 控制器 系列:- 标准包装:4,900 系列:- 控制器类型:USB 2.0 控制器 接口:串行 电源电压:3 V ~ 3.6 V 电流 - 电源:135mA 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:36-VFQFN 裸露焊盘 供应商设备封装:36-QFN(6x6) 包装:* 其它名称:Q6396337A |

| S1R72805F00A2 | 功能描述:IC LINK CTRLR 1394 IDE100 100QFP RoHS:否 类别:集成电路 (IC) >> 接口 - 控制器 系列:- 标准包装:4,900 系列:- 控制器类型:USB 2.0 控制器 接口:串行 电源电压:3 V ~ 3.6 V 电流 - 电源:135mA 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:36-VFQFN 裸露焊盘 供应商设备封装:36-QFN(6x6) 包装:* 其它名称:Q6396337A |

| S1R72901F00A | 功能描述:IC LINK CTRLR/PHY 1394 100-QFP RoHS:否 类别:集成电路 (IC) >> 接口 - 控制器 系列:- 标准包装:4,900 系列:- 控制器类型:USB 2.0 控制器 接口:串行 电源电压:3 V ~ 3.6 V 电流 - 电源:135mA 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:36-VFQFN 裸露焊盘 供应商设备封装:36-QFN(6x6) 包装:* 其它名称:Q6396337A |

| S1R72901F00A200 | 功能描述:IC PHY CONT 2PORT 1394A 100-QFP RoHS:否 类别:集成电路 (IC) >> 接口 - 控制器 系列:- 标准包装:4,900 系列:- 控制器类型:USB 2.0 控制器 接口:串行 电源电压:3 V ~ 3.6 V 电流 - 电源:135mA 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:36-VFQFN 裸露焊盘 供应商设备封装:36-QFN(6x6) 包装:* 其它名称:Q6396337A |

| S1R72C05 | 制造商:EPSON 制造商全称:EPSON 功能描述:Support for control, bulk, interrupt, and isochronous transfers |

发布紧急采购,3分钟左右您将得到回复。