- 您现在的位置:买卖IC网 > PDF目录199479 > TSB43AA82GGW (TEXAS INSTRUMENTS INC) 2 CHANNEL(S), 400M bps, SERIAL COMM CONTROLLER, PBGA176 PDF资料下载

参数资料

| 型号: | TSB43AA82GGW |

| 厂商: | TEXAS INSTRUMENTS INC |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 2 CHANNEL(S), 400M bps, SERIAL COMM CONTROLLER, PBGA176 |

| 封装: | PLASTIC, BGA-176 |

| 文件页数: | 145/146页 |

| 文件大小: | 770K |

| 代理商: | TSB43AA82GGW |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页第137页第138页第139页第140页第141页第142页第143页第144页当前第145页第146页

86

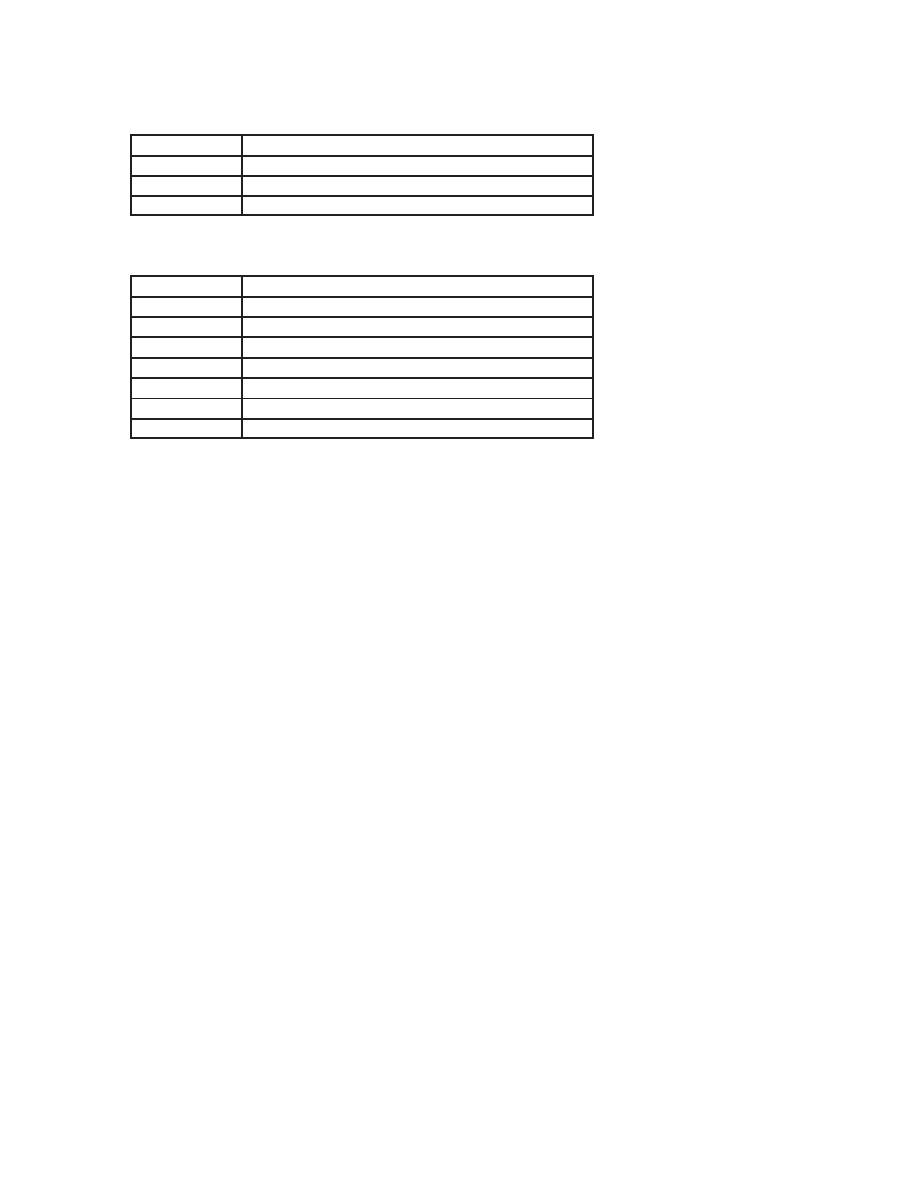

8-Bit Bulky

BDIF[2:0]

COMMENT

011

8-bit bulky mode

101

Reset

111

8-bit data of last block on packet

NOTES:

1. Any signal setting not included in the table is reserved.

2. Signal values should not be modified during data transfer.

16-Bit Bulky

BDIF[2:0]

COMMENT

000

8-bit data except last block on packet (lower)

010

16-bit bulky mode

011

8-bit bulky mode

100

8-bit data of last block on packet (lower)

110

16-bit data of last block on packet

101

Reset

111

8-bit data of last block on packet

NOTES:

1. Any signal setting not included in the table is reserved.

2. Signal values should not be modified during data transfer.

A written packet is automatically divided into the length specified by DTx header3, and is packetized.

Addresses specified on DTx header[1:2] are increased by the length of the data on each transmission. Also,

the last 3 bits of tLabel are incremented.

Each time an auto-divided packet transmission completes, DTAval is set and an appropriate

acknowledgement is displayed on DTxAck.

When a packetizer stops at the completion of all block data transmission or with some error, a DTFEnd

interrupt is created and its result is displayed on DTFSt(B0h).

8.4.2

Packet Receipt With DRF

By clearing the DRDSel bit on DMA control (90h), a packet stored in the DRF can be received. Data can not be read

with the DMA I/F in this case. When DRHStr in DMA control (90h) is set, the header of the packet is detached, and

the host reads only the data section with DRF data (ACh). The detached header is stored in DRF header[0:3]

(D0hDCh). When DRHStr is not set, the entire packet is read. The format for this is the same as reading from ARF.

Types of packets received by the DRF are:

Self-ID packet

Ordinary packet

Response packets to request packets from the DTF

Write request with specified address (direct mode)

Packetizer

Specified as a default

8.4.2.1 Self-ID Packet

Set both RXSId (08h, bit 1) and RSIsel (08h, bit 2) to 1 for the DRF to receive self-ID packets.

8.4.2.2 Response Packet to Request Packets From the DTF

To receive response packets to request packets from the DTF, set DTSpDis (90h, bit 7) to 0. This automatically sets

the expected values of the response packets. The DRF receives responses accordingly.

相关PDF资料 |

PDF描述 |

|---|---|

| TSB43DA42GHCR | PCI BUS CONTROLLER, PBGA196 |

| TSB500SK02 | 30 A, BARRIER STRIP TERMINAL BLOCK, 1 ROW, 1 DECK |

| TSB500SK10MDS | 30 A, BARRIER STRIP TERMINAL BLOCK, 1 ROW, 1 DECK |

| TSB5000331DS | 30 A, BARRIER STRIP TERMINAL BLOCK, 1 ROW, 1 DECK |

| TSB5000831 | 30 A, BARRIER STRIP TERMINAL BLOCK, 1 ROW, 1 DECK |

相关代理商/技术参数 |

参数描述 |

|---|---|

| TSB43AA82GHH | 制造商:Texas Instruments 功能描述: |

| TSB43AA82I | 制造商:TI 制造商全称:Texas Instruments 功能描述:1394 INTEGRATED PHY AND LINK LAYER CONTROLLER |

| TSB43AA82IGGW | 功能描述:1394 接口集成电路 2Port Hi Perf Integ Phy&Link Layer Chip RoHS:否 制造商:Texas Instruments 类型:Link Layer Controller 工作电源电压: 封装 / 箱体:LQFP 封装:Tray |

| TSB43AA82PGE | 功能描述:1394 接口集成电路 2Port Hi Perf Integ Phy&Link Layer Chip RoHS:否 制造商:Texas Instruments 类型:Link Layer Controller 工作电源电压: 封装 / 箱体:LQFP 封装:Tray |

| TSB43AA82PGEG4 | 功能描述:1394 接口集成电路 2Port Hi Per Int Phy & Link Layer Chip RoHS:否 制造商:Texas Instruments 类型:Link Layer Controller 工作电源电压: 封装 / 箱体:LQFP 封装:Tray |

发布紧急采购,3分钟左右您将得到回复。