- 您现在的位置:买卖IC网 > PDF目录3974 > UPD44647366AF5-E25-FQ1 (Renesas Electronics America)SRAM QDRII 72MBIT 165-PBGA PDF资料下载

参数资料

| 型号: | UPD44647366AF5-E25-FQ1 |

| 厂商: | Renesas Electronics America |

| 文件页数: | 11/42页 |

| 文件大小: | 0K |

| 描述: | SRAM QDRII 72MBIT 165-PBGA |

| 标准包装: | 1 |

| 格式 - 存储器: | RAM |

| 存储器类型: | SRAM - 同步,QDR II+ |

| 存储容量: | 72M(2M x 36) |

| 速度: | 400MHz |

| 接口: | 并联 |

| 电源电压: | 1.7 V ~ 1.9 V |

| 工作温度: | 0°C ~ 70°C |

| 封装/外壳: | 165-LBGA |

| 供应商设备封装: | 165-PBGA(13x15) |

| 包装: | 散装 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页当前第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页

�� �

�

�

�μ� PD44647094A-A,� 44647184A-A,� 44647364A-A,� 44647096A-A,� 44647186A-A,� 44647366A-A�

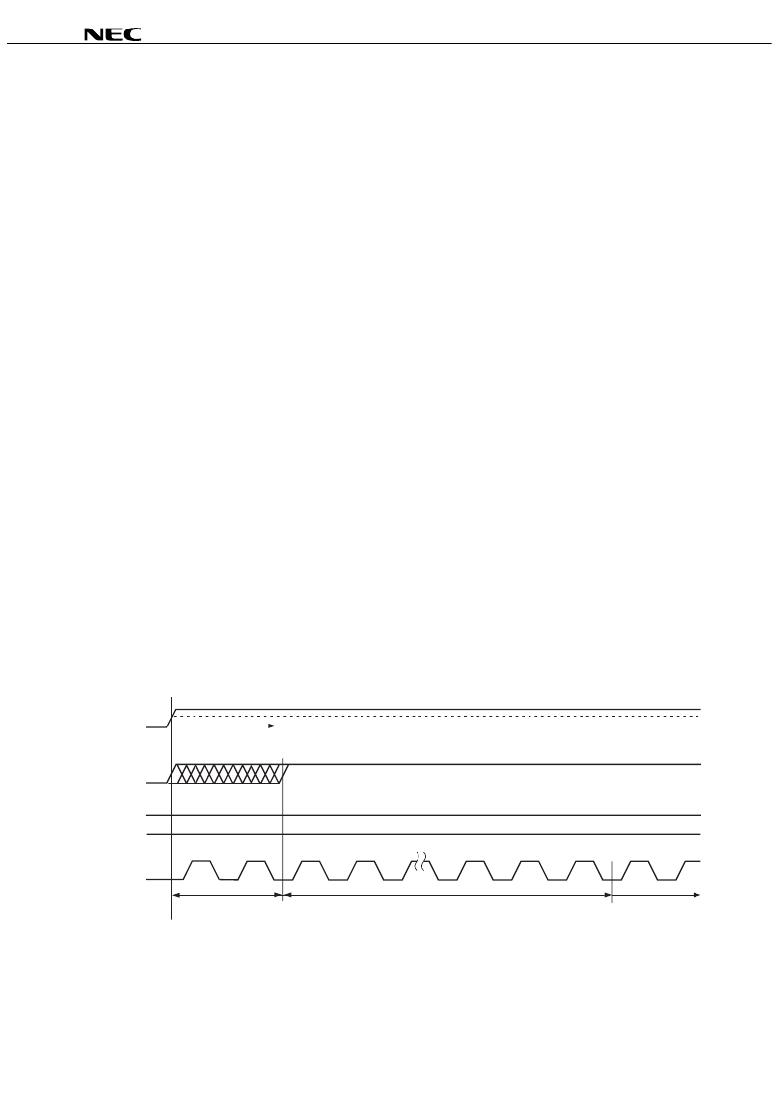

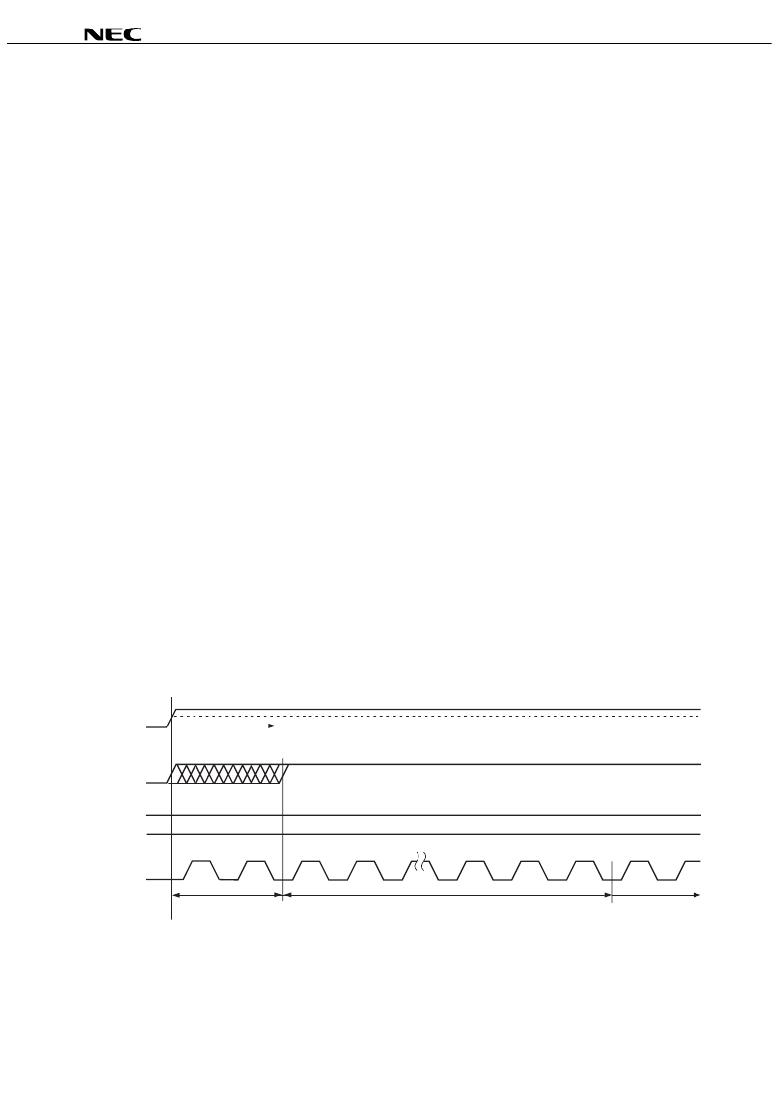

�Power-On� Sequence� in� QDR� II+� SRAM�

�QDR� II+� SRAMs� must� be� powered� up� and� initialized� in� a� predefined� manner� to� prevent� undefined� operations.�

�The� following� timing� charts� show� the� recommended� power-on� sequence.�

�The� following� power-up� supply� voltage� application� is� recommended:� V� SS� ,� V� DD� ,� V� DD� Q,� V� REF� ,� then� V� IN� .� V� DD� and� V� DD� Q�

�can� be� applied� simultaneously,� as� long� as� V� DD� Q� does� not� exceed� V� DD� by� more� than� 0.5� V� during� power-up.� The�

�following� power-down� supply� voltage� removal� sequence� is� recommended:� V� IN� ,� V� REF� ,� V� DD� Q,� V� DD� ,� V� SS� .� V� DD� and� V� DD� Q�

�can� be� removed� simultaneously,� as� long� as� V� DD� Q� does� not� exceed� V� DD� by� more� than� 0.5� V� during� power-down.�

�Power-On� Sequence�

�Apply� power� and� tie� DLL#� to� HIGH.�

�-� Apply� V� DD� before� V� DD� Q.�

�-� Apply� V� DD� Q� before� V� REF� or� at� the� same� time� as� V� REF.�

�Select� ODT� ON/OFF.�

�Provide� stable� clock� for� more� than� 20� μ� s� to� lock� the� DLL/PLL.�

�DLL/PLL� Constraints�

�The� DLL/PLL� uses� K� clock� as� its� synchronizing� input� and� the� input� should� have� low� phase� jitter� which� is� specified�

�as� TKC� var.� The� DLL/PLL� can� cover� 190� MHz� as� the� lowest� frequency.� If� the� input� clock� is� unstable� and� the�

�DLL/PLL� is� enabled,� then� the� DLL/PLL� may� lock� onto� an� undesired� clock� frequency.�

�ODT� initialization�

�The� ODT� ON/OFF� is� set� at� power-on� sequence.� When� the� ODT� Control� pin� is� HIGH� before� applying� stable� clock,�

�the� ODT� function� is� turn� on.� When� the� ODT� Control� pin� is� LOW� or� No� Connect,� the� ODT� function� is� off.� The� ODT�

�can� not� change� the� state� after� power-on.�

�Power-On� Waveforms�

�V� DD� /V� DD� Q�

�DLL#�

�ODT�

�Clock�

�V� DD� /V� DD� Q� Stable� (<� ±0.1� V� DC� per� 50� ns)�

�Fix� HIGH� (or� tied� to� V� DD� Q)�

�Fix� HIGH� or� LOW� (or� No� Connect)�

�Unstable� Clock�

�20� μ� s� or� more�

�Stable� Clock�

�Data� Sheet� M19962EJ2V0DS�

�Normal� Operation�

�Start�

�9�

�相关PDF资料 |

PDF描述 |

|---|---|

| MC7448HX1400NC | IC MPU RISC 32BIT 360-FCCBGA |

| UPD44647186AF5-E25-FQ1-A | SRAM QDRII 72MBIT 165-PBGA |

| UPD44647186AF5-E25-FQ1 | SRAM QDRII 72MBIT 165-PBGA |

| UPD44646363AF5-E25-FQ1-A | SRAM DDRII 72MBIT 165-PBGA |

| UPD44646363AF5-E25-FQ1 | SRAM DDRII 72MBIT 165-PBGA |

相关代理商/技术参数 |

参数描述 |

|---|---|

| UPD44647366AF5-E25-FQ1-A | 功能描述:SRAM QDRII 72MBIT 165-PBGA RoHS:是 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:3,000 系列:- 格式 - 存储器:EEPROMs - 串行 存储器类型:EEPROM 存储容量:8K (1K x 8) 速度:400kHz 接口:I²C,2 线串口 电源电压:1.7 V ~ 5.5 V 工作温度:-40°C ~ 85°C 封装/外壳:8-SOIC(0.154",3.90mm 宽) 供应商设备封装:8-SOIC 包装:带卷 (TR) |

| UPD446C-2L | 制造商:NEC Electronics Corporation 功能描述:2K X 8 STANDARD SRAM, 200 ns, PDIP24 |

| UPD446G-20L | 制造商:NEC Electronics Corporation 功能描述:2K X 8 STANDARD SRAM, 200 ns, PDFP24 |

| UPD45128163G5 | 制造商:Renesas Electronics Corporation 功能描述:128 MBIT SDRAM |

| UPD45128163G5-A75-9JF | 制造商:Elpida Memory Inc 功能描述:8M X 16 SYNCHRONOUS DRAM, 5.4 ns, PDSO54 |

发布紧急采购,3分钟左右您将得到回复。