- 您现在的位置:买卖IC网 > PDF目录3974 > UPD44647366AF5-E25-FQ1 (Renesas Electronics America)SRAM QDRII 72MBIT 165-PBGA PDF资料下载

参数资料

| 型号: | UPD44647366AF5-E25-FQ1 |

| 厂商: | Renesas Electronics America |

| 文件页数: | 20/42页 |

| 文件大小: | 0K |

| 描述: | SRAM QDRII 72MBIT 165-PBGA |

| 标准包装: | 1 |

| 格式 - 存储器: | RAM |

| 存储器类型: | SRAM - 同步,QDR II+ |

| 存储容量: | 72M(2M x 36) |

| 速度: | 400MHz |

| 接口: | 并联 |

| 电源电压: | 1.7 V ~ 1.9 V |

| 工作温度: | 0°C ~ 70°C |

| 封装/外壳: | 165-LBGA |

| 供应商设备封装: | 165-PBGA(13x15) |

| 包装: | 散装 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页当前第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页

�� �

�

�

�μ� PD44647094A-A,� 44647184A-A,� 44647364A-A,� 44647096A-A,� 44647186A-A,� 44647366A-A�

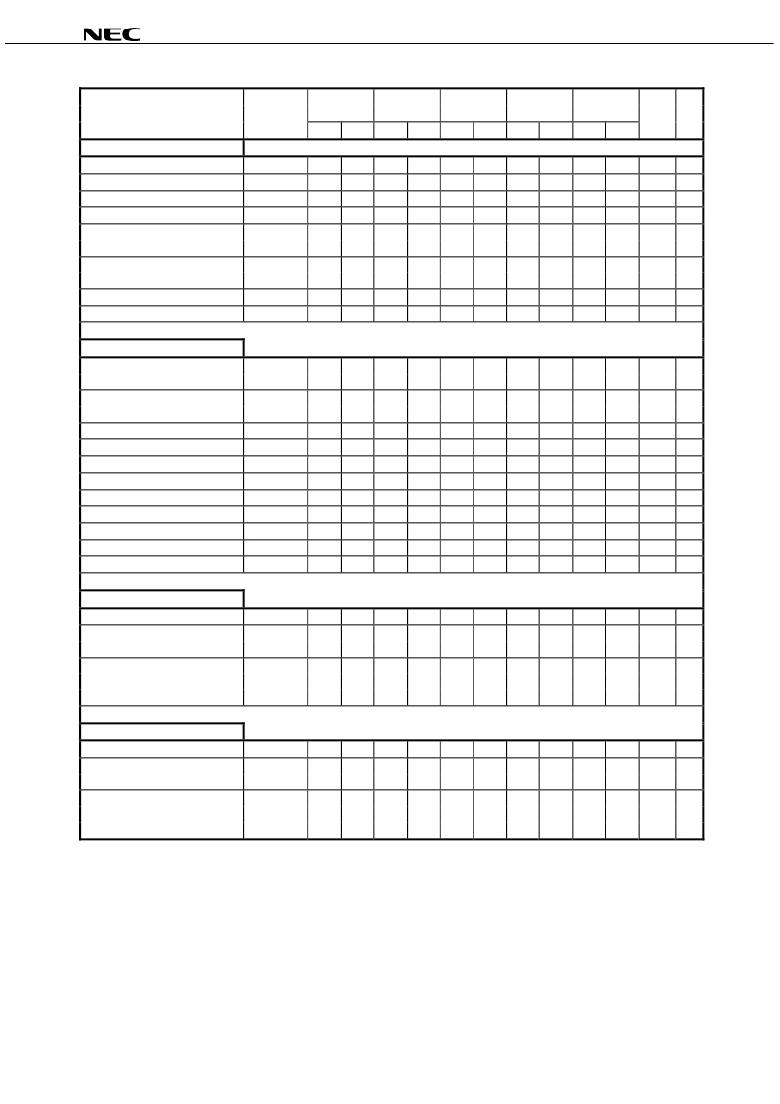

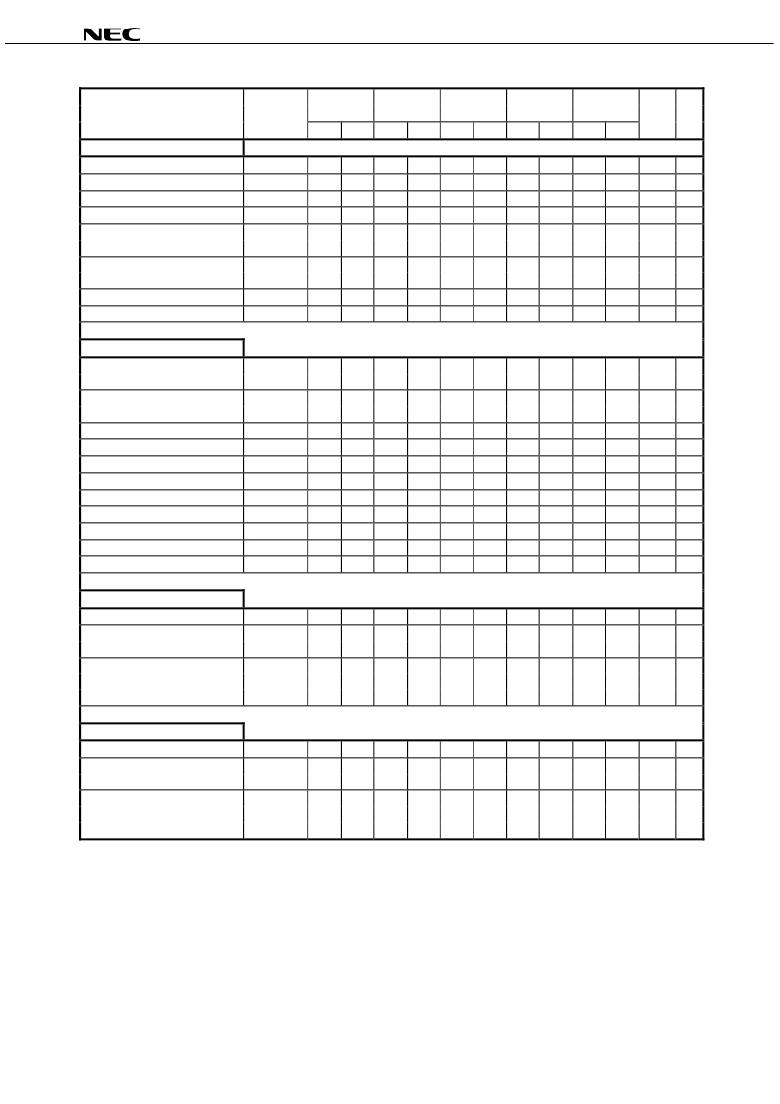

�Read� and� Write� Cycle�

�Parameter�

�Symbol�

�-E20�

�Note1�

�-E22�

�Note1�

�-E25�

�-E30�

�-E33�

�Unit�

�Note�

�(500� MHz)�

�(450� MHz)�

�(400� MHz)�

�(333� MHz)�

�(300� MHz)�

�MIN.� MAX.� MIN.� MAX.� MIN.� MAX.� MIN.� MAX.� MIN.� MAX.�

�Clock�

�Average Clock cycle time (K, K#)�

�TKHKH�

�2.0�

�5.25�

�2.2�

�5.25�

�2.5�

�5.25�

�3.0�

�5.25�

�3.3�

�5.25�

�ns�

�2�

�Clock� phase� jitter� (K,� K#)�

�Clock� HIGH� time� (K,� K#)�

�Clock� LOW� time� (K,� K#)�

�Clock� HIGH� to� Clock#� HIGH�

�TKC� var�

�TKHKL�

�TKLKH�

�TKHK#H�

�0.4�

�0.4�

�0.85�

�0.15�

�0.4�

�0.4�

�0.95�

�0.15�

�0.4�

�0.4�

�1.06�

�0.20�

�0.4�

�0.4�

�1.28�

�0.20�

�0.4�

�0.4�

�1.40�

�0.20�

�ns�

�TKHKH�

�TKHKH�

�ns�

�3�

�(K� →� K#)�

�Clock#� HIGH� to� Clock� HIGH�

�TK#HKH�

�0.85�

�0.95�

�1.06�

�1.28�

�1.40�

�ns�

�(K#� →� K)�

�DLL/PLL� lock� time� (K)�

�K� static� to� DLL/PLL� reset�

�TKC� lock�

�TKC� reset�

�20�

�30�

�20�

�30�

�20�

�30�

�20�

�30�

�20�

�30�

�μ� s�

�ns�

�4�

�5�

�Output� Times�

�CQ� HIGH� to� CQ#� HIGH�

�TCQHCQ#H�

�0.6�

�0.7�

�0.81�

�1.03�

�1.15�

�ns�

�6�

�(CQ� →� CQ#)�

�CQ#� HIGH� to� CQ� HIGH�

�TCQ#HCQH�

�0.6�

�0.7�

�0.81�

�1.03�

�1.15�

�ns�

�6�

�(CQ#� →� CQ)�

�K,� K#� HIGH� to� output� valid�

�K,� K#� HIGH� to� output� hold�

�K,� K#� HIGH� to� echo� clock� valid�

�K,� K#� HIGH� to� echo� clock� hold�

�TKHQV�

�TKHQX�

�TKHCQV�

�TKHCQX�

�– 0.45�

�– 0.45�

�0.45�

�0.45�

�– 0.45�

�– 0.45�

�0.45�

�0.45�

�– 0.45�

�– 0.45�

�0.45�

�0.45�

�– 0.45�

�– 0.45�

�0.45�

�0.45�

�– 0.45�

�– 0.45�

�0.45�

�0.45�

�ns�

�ns�

�ns�

�ns�

�CQ,� CQ#� HIGH� to� output� valid�

�CQ,� CQ#� HIGH� to� output� hold�

�K� HIGH� to� output� High-Z�

�K� HIGH� to� output� Low-Z�

�TCQHQV�

�TCQHQX�

�TKHQZ�

�TKHQX1�

�– 0.15�

�– 0.45�

�0.15�

�0.45�

�– 0.15�

�– 0.45�

�0.15�

�0.45�

�– 0.20�

�– 0.45�

�0.20�

�0.45�

�– 0.20�

�– 0.45�

�0.20�

�0.45�

�– 0.20�

�– 0.45�

�0.20�

�0.45�

�ns�

�ns�

�ns�

�ns�

�7�

�7�

�CQ,� CQ#� HIGH� to� QVLD� valid�

�Setup� Times�

�TCQHQVLD� –� 0.15� 0.15� –� 0.15� 0.15� –� 0.20� 0.20� –� 0.20� 0.20� –� 0.20� 0.20�

�ns�

�Address� valid� to� K� rising� edge�

�Control� inputs� (R#,� W#)� valid� to�

�TAVKH�

�TIVKH�

�0.33�

�0.33�

�0.4�

�0.4�

�0.4�

�0.4�

�0.4�

�0.4�

�0.4�

�0.4�

�ns�

�ns�

�8�

�8�

�K� rising� edge�

�Data� inputs� and� write� data� select�

�TDVKH�

�0.25�

�0.28�

�0.28�

�0.28�

�0.28�

�ns�

�8�

�inputs� (BWx#)� valid� to�

�K,� K#� rising� edge�

�Hold� Times�

�K� rising� edge� to� address� hold�

�K� rising� edge� to� control� inputs�

�TKHAX�

�TKHIX�

�0.33�

�0.33�

�0.4�

�0.4�

�0.4�

�0.4�

�0.4�

�0.4�

�0.4�

�0.4�

�ns�

�ns�

�8�

�8�

�(R#,� W#)� hold�

�K,� K#� rising� edge� to� data� inputs�

�TKHDX�

�0.25�

�0.28�

�0.28�

�0.28�

�0.28�

�ns�

�8�

�and� write� data� select� inputs�

�(BWx#)� hold�

�Notes� 1.� -E20� and� -E22� are� valid� for� 2.5� Clock� Cycles� Read� Latency� products.�

�2.� When� debugging� the� system� or� board,� these� products� can� operate� at� a� clock� frequency� slower� than� TKHKH�

�(MAX.)� without� the� DLL/PLL� circuit� being� used,� if� DLL#� =� LOW.� Read� latency� (RL)� is� changed� to� 1.0� clock�

�cycle� regardless� of� RL� =� 2.0� and� 2.5� clock� cycles� products� in� this� operation.� The� AC/DC� characteristics�

�cannot� be� guaranteed,� however.�

�3.� Clock� phase� jitter� is� the� variance� from� clock� rising� edge� to� the� next� expected� clock� rising� edge.� TKC� var�

�(MAX.)� indicates� a� peak-to-peak� value.�

�18�

�Data� Sheet� M19962EJ2V0DS�

�相关PDF资料 |

PDF描述 |

|---|---|

| MC7448HX1400NC | IC MPU RISC 32BIT 360-FCCBGA |

| UPD44647186AF5-E25-FQ1-A | SRAM QDRII 72MBIT 165-PBGA |

| UPD44647186AF5-E25-FQ1 | SRAM QDRII 72MBIT 165-PBGA |

| UPD44646363AF5-E25-FQ1-A | SRAM DDRII 72MBIT 165-PBGA |

| UPD44646363AF5-E25-FQ1 | SRAM DDRII 72MBIT 165-PBGA |

相关代理商/技术参数 |

参数描述 |

|---|---|

| UPD44647366AF5-E25-FQ1-A | 功能描述:SRAM QDRII 72MBIT 165-PBGA RoHS:是 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:3,000 系列:- 格式 - 存储器:EEPROMs - 串行 存储器类型:EEPROM 存储容量:8K (1K x 8) 速度:400kHz 接口:I²C,2 线串口 电源电压:1.7 V ~ 5.5 V 工作温度:-40°C ~ 85°C 封装/外壳:8-SOIC(0.154",3.90mm 宽) 供应商设备封装:8-SOIC 包装:带卷 (TR) |

| UPD446C-2L | 制造商:NEC Electronics Corporation 功能描述:2K X 8 STANDARD SRAM, 200 ns, PDIP24 |

| UPD446G-20L | 制造商:NEC Electronics Corporation 功能描述:2K X 8 STANDARD SRAM, 200 ns, PDFP24 |

| UPD45128163G5 | 制造商:Renesas Electronics Corporation 功能描述:128 MBIT SDRAM |

| UPD45128163G5-A75-9JF | 制造商:Elpida Memory Inc 功能描述:8M X 16 SYNCHRONOUS DRAM, 5.4 ns, PDSO54 |

发布紧急采购,3分钟左右您将得到回复。