- 您现在的位置:买卖IC网 > PDF目录11831 > XR16C2852IJTR-F (Exar Corporation)IC UART FIFO 128B 44PLCC PDF资料下载

参数资料

| 型号: | XR16C2852IJTR-F |

| 厂商: | Exar Corporation |

| 文件页数: | 6/51页 |

| 文件大小: | 0K |

| 描述: | IC UART FIFO 128B 44PLCC |

| 标准包装: | 500 |

| 特点: | * |

| 通道数: | 2,DUART |

| FIFO's: | 128 字节 |

| 规程: | RS232,RS485 |

| 电源电压: | 2.97 V ~ 5.5 V |

| 带自动流量控制功能: | 是 |

| 带IrDA 编码器/解码器: | 是 |

| 带故障启动位检测功能: | 是 |

| 带调制解调器控制功能: | 是 |

| 带CMOS: | 是 |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 44-LCC(J 形引线) |

| 供应商设备封装: | 44-PLCC(16.59x16.59) |

| 包装: | 带卷 (TR) |

第1页第2页第3页第4页第5页当前第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页

XR16C2852

xr

2.97V TO 5.5V DUAL UART WITH 128-BYTE FIFOS

REV. 2.1.1

14

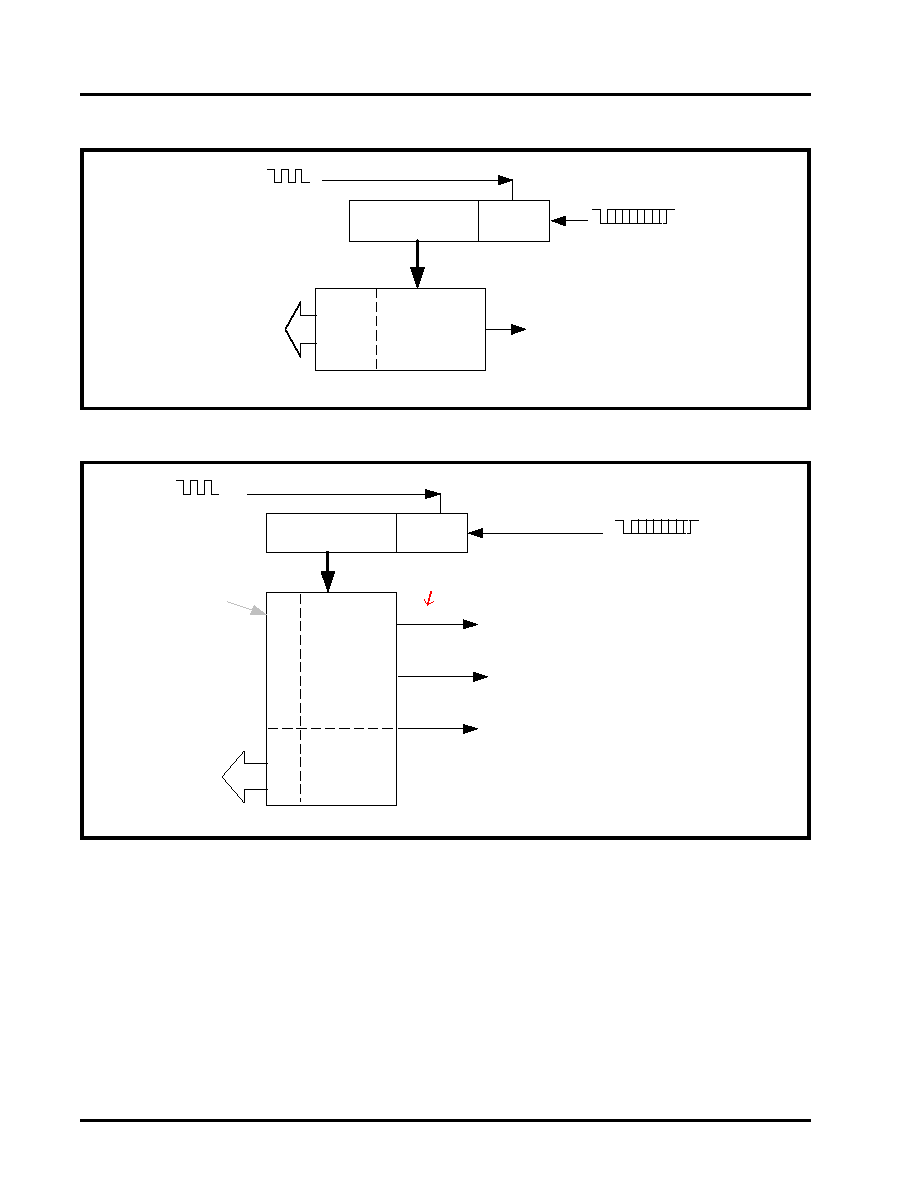

FIGURE 9. RECEIVER OPERATION IN NON-FIFO MODE

FIGURE 10. RECEIVER OPERATION IN FIFO AND AUTO RTS FLOW CONTROL MODE

Receive Data Shift

Register (RSR)

Receive

Data Byte

and Errors

RHR Interrupt (ISR bit-2)

Receive Data

Holding Register

(RHR)

RXFIFO1

16X Clock

Receive Data Characters

Data Bit

Validation

Error

Tags in

LSR bits

4:2

Receive Data Shift

Register (RSR)

RXFIFO1

16X Clock

E

rro

rT

ags

(1

28-

sets)

E

rror

T

ags

in

LS

R

b

its

4:

2

128 bytes by 11-bit

wide FIFO

Receive Data Characters

FIFO Trigger=16

Example:

- RX FIFO trigger level selected at 16 bytes

(See Note Below)

Data fills to 24

Data falls to 8

Data Bit

Validation

Receive

Data FIFO

Receive

Data

Receive Data

Byte and Errors

RHR Interrupt (ISR bit-2) programmed for

desired FIFO trigger level.

FIFO is Enabled by FCR bit-0=1

RTS# de-asserts when data fills above the flow

control trigger level to suspend remote transmitter.

Enable by EFR bit-6=1, MCR bit-2.

RTS# re-asserts when data falls below the flow

control trigger level to restart remote transmitter.

Enable by EFR bit-6=1, MCR bit-2.

相关PDF资料 |

PDF描述 |

|---|---|

| XR16C2850IJTR-F | IC UART FIFO 128B 44PLCC |

| XR16V554IV-F | IC UART FIFO 16B QUAD 64LQFP |

| VE-B5L-IW-F1 | CONVERTER MOD DC/DC 28V 100W |

| VE-B5L-IX-F4 | CONVERTER MOD DC/DC 28V 75W |

| VE-B5L-IX-F2 | CONVERTER MOD DC/DC 28V 75W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XR-16C450CJ | 制造商:未知厂家 制造商全称:未知厂家 功能描述:UART |

| XR-16C450CP | 制造商:未知厂家 制造商全称:未知厂家 功能描述:UART |

| XR-16C452CJ | 制造商:未知厂家 制造商全称:未知厂家 功能描述:UART |

| XR-16C550CJ | 制造商:未知厂家 制造商全称:未知厂家 功能描述:UART |

| XR-16C550CP | 制造商:未知厂家 制造商全称:未知厂家 功能描述:UART |

发布紧急采购,3分钟左右您将得到回复。