参数资料

| 型号: | XRD98L63AIV-F |

| 厂商: | Exar Corporation |

| 文件页数: | 40/41页 |

| 文件大小: | 0K |

| 描述: | IC CCD DIGITIZER 12BIT 48TQFP |

| 标准包装: | 250 |

| 位数: | 12 |

| 通道数: | 1 |

| 电压 - 电源,模拟: | 2.7 V ~ 3.6 V |

| 电压 - 电源,数字: | 2.7 V ~ 3.6 V |

| 封装/外壳: | 48-TQFP |

| 供应商设备封装: | 48-TQFP(7x7) |

| 包装: | 托盘 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页当前第40页第41页

XRD98L63

8

Rev.1.01

SERIAL INTERFACE

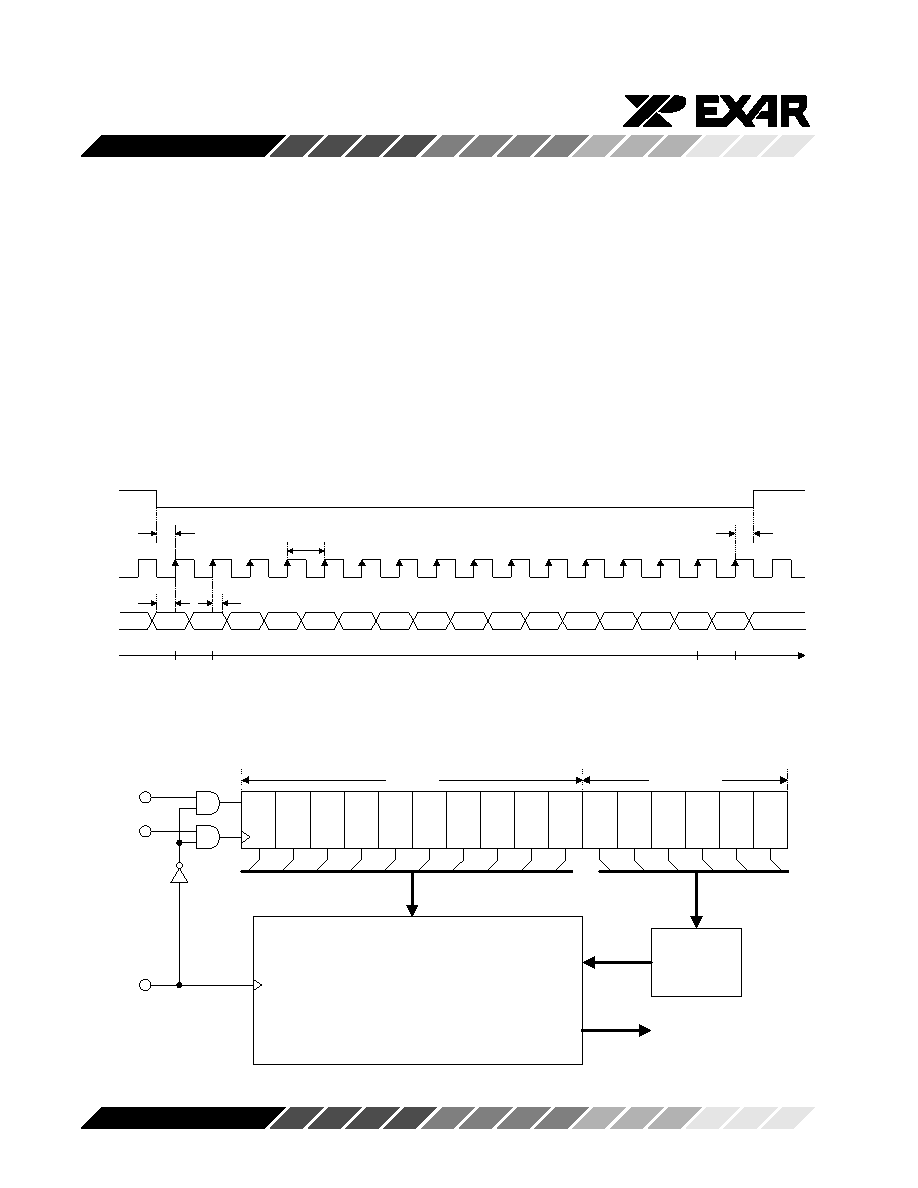

The XRD98L63 uses a three wire serial interface

(LOAD, SDI & SCLK) to access the programmable

features and controls of the chip. The serial interface

uses a 16-bit shift register. The first 6 bits shifted in are

the address bits, the next 10 bits are the data bits. The

address bits select which of the internal registers will

receive the 10 data bits.

The interface will only load data from the shift register

into the register array if there are exactly 16 rising edges

of SCLK while LOAD is low. If more or less rising edges

are present, the data is discarded. There is no checking

of the address bits to ensure a valid register is written

to. If the address bits select an undefined register, the

SCLK

SDI

LOAD

Time

A3

A2

A1

A0

D7

D6

D5

D4

D3

D2

D1

D0

t1

t2

t16

t15

…

t

L1

t

L2

t

SCLK

t

set

t

hold

MSB

LSB

D8

D9

A5

A4

data will be discarded. There is a readback function

(see the Serial Interface Read Back section) that

outputs the contents of a selected register on pins

DB[11:2] of the digital output bus.

The following is the procedure for writing to the serial

interface:

1)

Force LOAD pin low to enable shift register.

2)

Shift in 16 bits, 6 address bits (msb first),

followed by 10 data bits (msb first).

3)

Force LOAD pin high to transfer data from the

shift register to the serial interface register array.

Note: There must be exactly 16 rising edges of

SCLK while LOAD is low.

Figure 4. Serial Interface Timing Diagram

Register Array

SD I

SCLK

LOAD

Register

Select

Da ta Input

Address

Decoder

Address Bits

Da ta Bits

D0

D1

D2

D3

D4

D5

D6

D7

A0

A1

A2

A3

MSB

LSB

A4

A5

D8

D9

Read Back

Output Bus

to DB[11:2]

Figure 5. Serial Interface Block Diagram

相关PDF资料 |

PDF描述 |

|---|---|

| XRT71D00IQ-F | IC JITTER ATTENUATOR SGL 32TQFP |

| XRT71D03IV-F | IC JITTER ATTENUATOR 3CH 64TQFP |

| XRT71D04IV | IC JITTER ATTENUATOR 4CH 80TQFP |

| XRT8000IP-F | IC WAN CLOCK E1/E1 DUAL 18PDIP |

| XRT8001IP-F | IC WAN CLOCK E1/E1 DUAL 18PDIP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XRD98L63AIVTR-F | 制造商:Exar Corporation 功能描述:AFE General Purpose 1ADC 12-Bit 3V 48-Pin TQFP T/R 制造商:Exar Corporation 功能描述:XRD98L63AIVTR-F |

| XRD98L63EVAL | 功能描述:数据转换 IC 开发工具 Eval Board for XRD98L63AIV RoHS:否 制造商:Texas Instruments 产品:Demonstration Kits 类型:ADC 工具用于评估:ADS130E08 接口类型:SPI 工作电源电压:- 6 V to + 6 V |

| XRD98L63ZEVAL | 功能描述:数据转换 IC 开发工具 Eval Board (Solder) XRD98L63AIV RoHS:否 制造商:Texas Instruments 产品:Demonstration Kits 类型:ADC 工具用于评估:ADS130E08 接口类型:SPI 工作电源电压:- 6 V to + 6 V |

| XRDAN27 | 制造商:EXAR 制造商全称:EXAR 功能描述:Compensating for Zero Order Hold Effects |

| XRDAN28 | 制造商:EXAR 制造商全称:EXAR 功能描述:Frequency Response Effects of Overampling and Averaging on A/D Output Data |

发布紧急采购,3分钟左右您将得到回复。