参数资料

| 型号: | ZL6105ALAFTR5546 |

| 厂商: | Intersil |

| 文件页数: | 15/35页 |

| 文件大小: | 0K |

| 描述: | IC REG CTRLR BUCK PWM VM 36-QFN |

| 标准包装: | 100 |

| PWM 型: | 电压模式 |

| 输出数: | 1 |

| 频率 - 最大: | 1.4MHz |

| 占空比: | 95% |

| 电源电压: | 3 V ~ 14 V |

| 降压: | 是 |

| 升压: | 无 |

| 回扫: | 无 |

| 反相: | 无 |

| 倍增器: | 无 |

| 除法器: | 无 |

| Cuk: | 无 |

| 隔离: | 无 |

| 工作温度: | -40°C ~ 85°C |

| 封装/外壳: | 36-VFQFN 裸露焊盘 |

| 包装: | 托盘 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页当前第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页

�� �

�

�

�ZL6105�

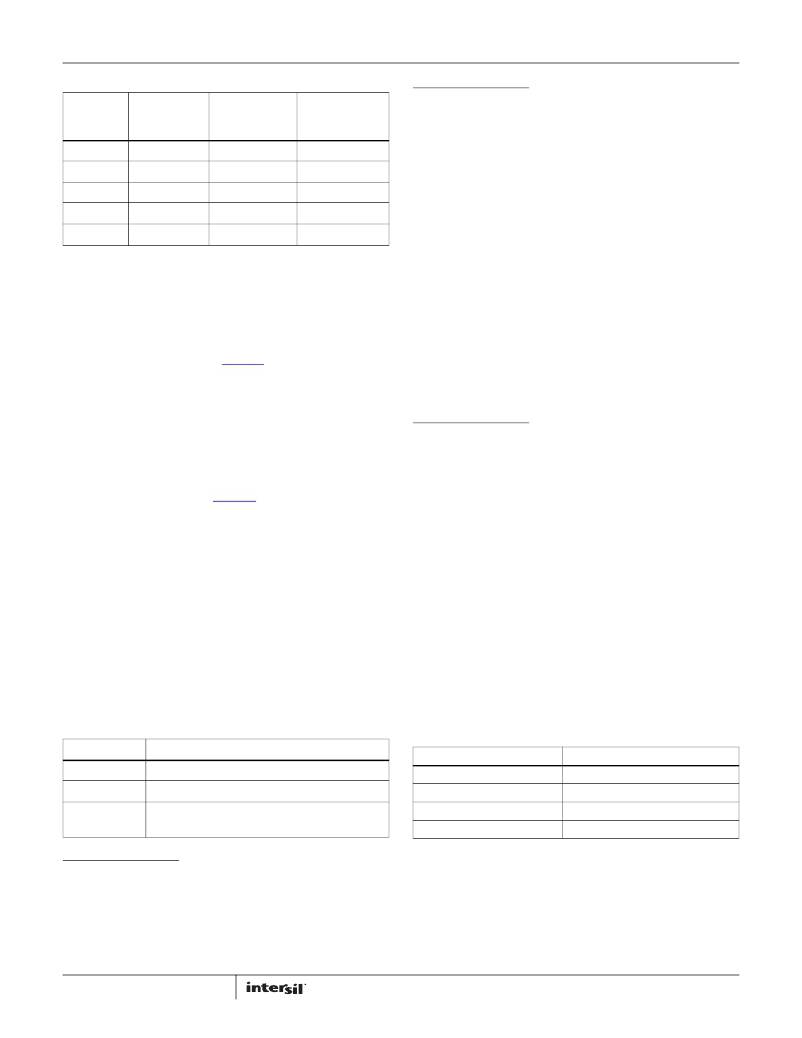

�TABLE� 8.� MINIMUM� TON� DELAY� vs� OPERATING� MODE�

�Min.�

�CONFIGURATION B:� SYNC� INPUT�

�When� the� SYNC� pin� is� configured� as� an� input� (CFG1� pin� is� tied� LOW)� and�

�Current�

�Low-Power�

�TON_DELAY�

�the� device� is� in� Monitor� Mode� or� self-enabled� (EN� tied� to� V25� or�

�Sharing�

�X�

�Disabled�

�Disabled�

�Enabled�

�Enabled�

�AutoComp�

�Disabled�

�Enabled�

�X�

�Disabled�

�Enabled�

�Standby�

�False�

�False�

�True�

�True�

�X�

�(ms)�

�5�

�5�

�10�

�15�

�15�

�ON_OFF_CONFIG[4]� =� 0),� the� device� will� check� for� a� clock� signal� on� the�

�SYNC� pin� immediately� after� power-up.� In� this� case,� the� incoming� clock�

�signal� must� be� in� the� range� of� 200kHz� to� 1.4MHz� and� must� be� stable�

�within� 10μs� after� V25� rises� above� 2.25V.� When� the� SYNC� pin� is�

�configured� as� an� input� (CFG1� pin� is� tied� LOW)� and� the� device� is� in� Low�

�Power� Mode,� the� device� will� check� for� a� clock� signal� on� the� SYNC� pin�

�immediately� after� EN� goes� true.� In� this� case,� the� incoming� clock� signal�

�must� be� in� range� and� stable� before� EN� goes� true.� The� ZL6105's�

�oscillator� will� then� synchronize� with� the� rising� edge� of� the� external� clock.�

�Power-Good�

�The� ZL6105� provides� a� Power-Good� (PG)� signal� that� indicates� the�

�output� voltage� is� within� a� specified� tolerance� of� its� target� level�

�and� no� fault� condition� exists.� By� default,� the� PG� pin� will� assert� if�

�the� output� is� within� -10%� of� the� target� voltage.� These� limits� and�

�the� polarity� of� the� pin� may� be� changed� via� the� I� 2� C/SMBus�

�interface.� See� Application� Note� AN2033� for� details.�

�A� PG� delay� period� is� defined� as� the� time� from� when� all� conditions�

�within� the� ZL6105� for� asserting� PG� are� met� to� when� the� PG� pin� is�

�actually� asserted.� This� feature� is� commonly� used� instead� of� using�

�an� external� reset� controller� to� control� external� digital� logic.� By�

�default,� the� ZL6105� PG� delay� is� set� equal� to� the� soft-start� ramp�

�time� setting.� Therefore,� if� the� soft-start� ramp� time� is� set� to� 10ms,�

�the� PG� delay� will� be� set� to� 10ms.� The� PG� delay� may� be� set�

�independently� of� the� soft-start� ramp� using� the� I� 2� C/SMBus� as�

��If� Auto� Comp� is� enabled,� the� PG� timing� is� further� controlled� by�

�the� PG� Assert� parameter,� as� described� in� “Loop� Compensation”�

��Switching� Frequency� and� PLL�

�The� ZL6105� incorporates� an� internal� phase-locked� loop� (PLL)� to� clock�

�the� internal� circuitry.� The� PLL� can� be� driven� by� an� external� clock� source�

�connected� to� the� SYNC� pin.� When� using� the� internal� oscillator,� the� SYNC�

�pin� can� be� configured� as� a� clock� source� for� other� Zilker� Labs� devices.�

�The� SYNC� pin� is� a� unique� pin� that� can� perform� multiple� functions�

�depending� on� how� it� is� configured.� The� CFG1� pin� is� used� to� select�

�the� operating� mode� of� the� SYNC� pin� as� shown� in� Table� 9.�

�Figure� 13� illustrates� the� typical� connections� for� each� mode.�

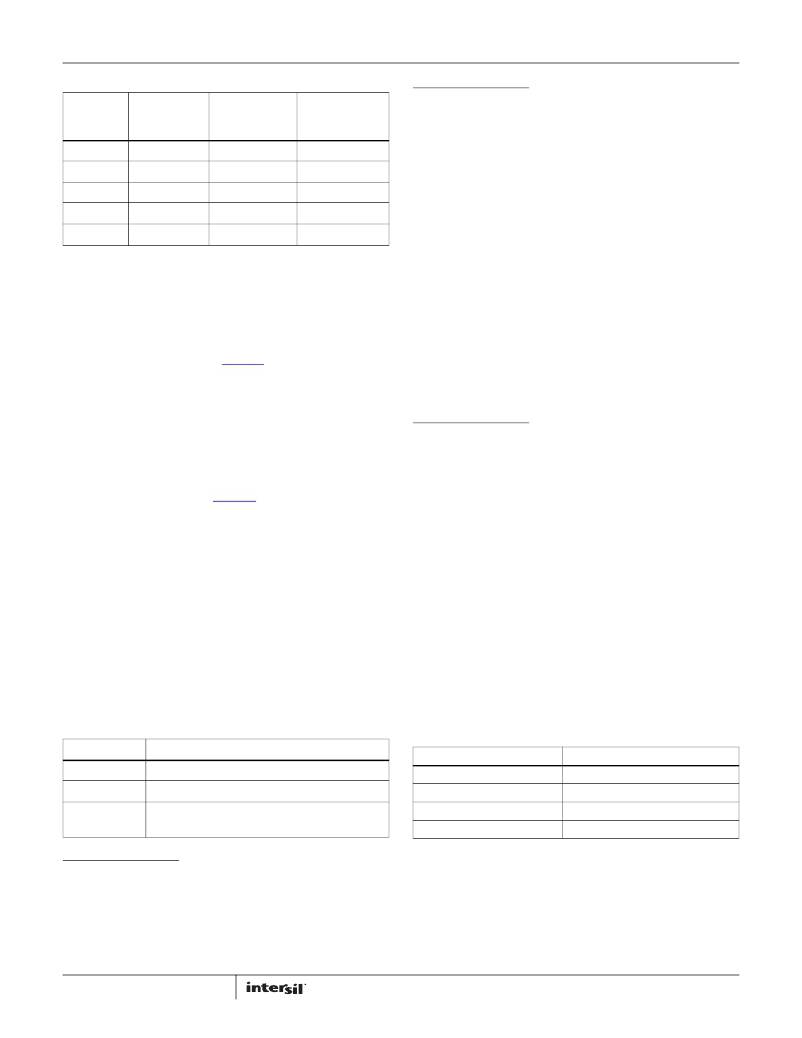

�TABLE� 9.� SYNC� PIN� FUNCTION� SELECTION�

�The� incoming� clock� signal� must� be� in� the� range� of� 200kHz� to�

�1.4MHz� and� must� be� stable� when� the� enable� pin� is� asserted.� The�

�clock� signal� must� also� exhibit� the� necessary� performance�

�requirements� (see� “Electrical� Specifications”� on� page� 8).� In� the�

�event� of� a� loss� of� the� external� clock� signal,� the� output� voltage�

�may� show� transient� over/undershoot.�

�If� this� happens,� the� ZL6105� will� automatically� switch� to� its�

�internal� oscillator� and� switch� at� a� frequency� close� to� the� previous�

�incoming� frequency.�

�CONFIGURATION C:� SYNC� AUTO� DETECT�

�When� the� SYNC� pin� is� configured� in� auto� detect� mode� (CFG1� pin� is� left�

�OPEN)� and� the� device� is� in� Monitor� Mode� or� self-enabled� (EN� tied� to� V25�

�or� ON_OFF_CONFIG[4]� =� 0),� the� device� will� check� for� a� clock� signal� on�

�the� SYNC� pin� immediately� after� power-up.� In� this� case,� the� incoming�

�clock� signal� must� be� in� the� range� of� 200kHz� to� 1.4MHz� and� must� be�

�stable� within� 10μs� after� V25� rises� above� 2.25V.� When� the� SYNC� pin� is�

�configured� in� auto� detect� mode� (CFG1� pin� is� left� OPEN)� and� the� device� is�

�in� Low� Power� Mode,� the� device� will� check� for� a� clock� signal� on� the� SYNC�

�pin� immediately� after� EN� goes� true.� In� this� case,� the� incoming� clock�

�signal� must� be� in� range� and� stable� before� EN� goes� true.�

�If� a� clock� signal� is� present,� the� ZL6105's� oscillator� will� then�

�synchronize� with� the� rising� edge� of� the� external� clock.� Refer� to�

��If� no� incoming� clock� signal� is� present,� the� ZL6105� will� configure�

�the� switching� frequency� according� to� the� state� of� the� SYNC� pin� as�

�listed� in� Table� 10.� In� SYNC� AutoDetect� mode,� the� ZL6105� will�

�only� read� the� SYNC� pin� connection� during� the� first� start-up�

�sequence;� changes� to� SYNC� pin� connections� will� not� affect� f� SW�

�until� the� power� (VDD)� is� cycled� off� and� on.�

�TABLE� 10.� SWITCHING� FREQUENCY� PIN-STRAP� SETTINGS�

�CFG1� PIN�

�LOW�

�OPEN�

�HIGH�

�SYNC� PIN� FUNCTION�

�SYNC� is� configured� as� an� input�

�Auto� Detect� mode�

�SYNC� is� configured� as� an� output�

�f� SW� =� 400kHz�

�SYNC� PIN�

�LOW�

�OPEN�

�HIGH�

�Resistor�

�FREQUENCY�

�200kHz�

�400kHz�

�1MHz�

�See� Table� 11�

�CONFIGURATION A:� SYNC� OUTPUT�

�When� the� SYNC� pin� is� configured� as� an� output� (CFG1� pin� is� tied� HIGH),�

�the� device� will� run� from� its� internal� oscillator� and� will� drive� the� resulting�

�internal� oscillator� signal� (preset� to� 400kHz)� onto� the� SYNC� pin� so� other�

�devices� can� be� synchronized� to� it.� The� SYNC� pin� will� not� be� checked� for�

�an� incoming� clock� signal� while� in� this� mode.�

�15�

�If� the� user� wishes� to� run� the� ZL6105� at� a� frequency� not� listed� in�

�Figure� 10,� the� switching� frequency� can� be� set� using� an� external�

�resistor,� R� SYNC� ,� connected� between� SYNC� and� SGND� using� Table� 11.�

�FN6906.5�

�December� 19,� 2013�

�相关PDF资料 |

PDF描述 |

|---|---|

| ZLDO1117G25TA | IC REG LDO 2.5V 1A SOT223-3 |

| ZLDO330T8TA | IC REG LDO 3.3V .3A SOT223-8 |

| ZLDO485T8TA | IC REG LDO 4.85V .3A SOT223-8 |

| ZLDO500T8TA | IC REG LDO 5V .3A SOT223-8 |

| ZM331643GTC | IC MONITOR 2.68V SUPPLY SOT223 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ZL62034UBJA | 制造商:TE Connectivity 功能描述:4x6.25 Gb/s TIA/LA Receiver D |

| ZL62B | 制造商:YEASHIN 制造商全称:YEASHIN 功能描述:500 mW DO-35 Hermetically Sealed Glass Zener Voltage Regulators |

| ZL68B | 制造商:YEASHIN 制造商全称:YEASHIN 功能描述:500 mW DO-35 Hermetically Sealed Glass Zener Voltage Regulators |

| ZL6V2B | 制造商:YEASHIN 制造商全称:YEASHIN 功能描述:500 mW DO-35 Hermetically Sealed Glass Zener Voltage Regulators |

| ZL6V8B | 制造商:YEASHIN 制造商全称:YEASHIN 功能描述:500 mW DO-35 Hermetically Sealed Glass Zener Voltage Regulators |

发布紧急采购,3分钟左右您将得到回复。