参数资料

| 型号: | ZL6105ALAFTR5546 |

| 厂商: | Intersil |

| 文件页数: | 9/35页 |

| 文件大小: | 0K |

| 描述: | IC REG CTRLR BUCK PWM VM 36-QFN |

| 标准包装: | 100 |

| PWM 型: | 电压模式 |

| 输出数: | 1 |

| 频率 - 最大: | 1.4MHz |

| 占空比: | 95% |

| 电源电压: | 3 V ~ 14 V |

| 降压: | 是 |

| 升压: | 无 |

| 回扫: | 无 |

| 反相: | 无 |

| 倍增器: | 无 |

| 除法器: | 无 |

| Cuk: | 无 |

| 隔离: | 无 |

| 工作温度: | -40°C ~ 85°C |

| 封装/外壳: | 36-VFQFN 裸露焊盘 |

| 包装: | 托盘 |

第1页第2页第3页第4页第5页第6页第7页第8页当前第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页

�� �

�

�

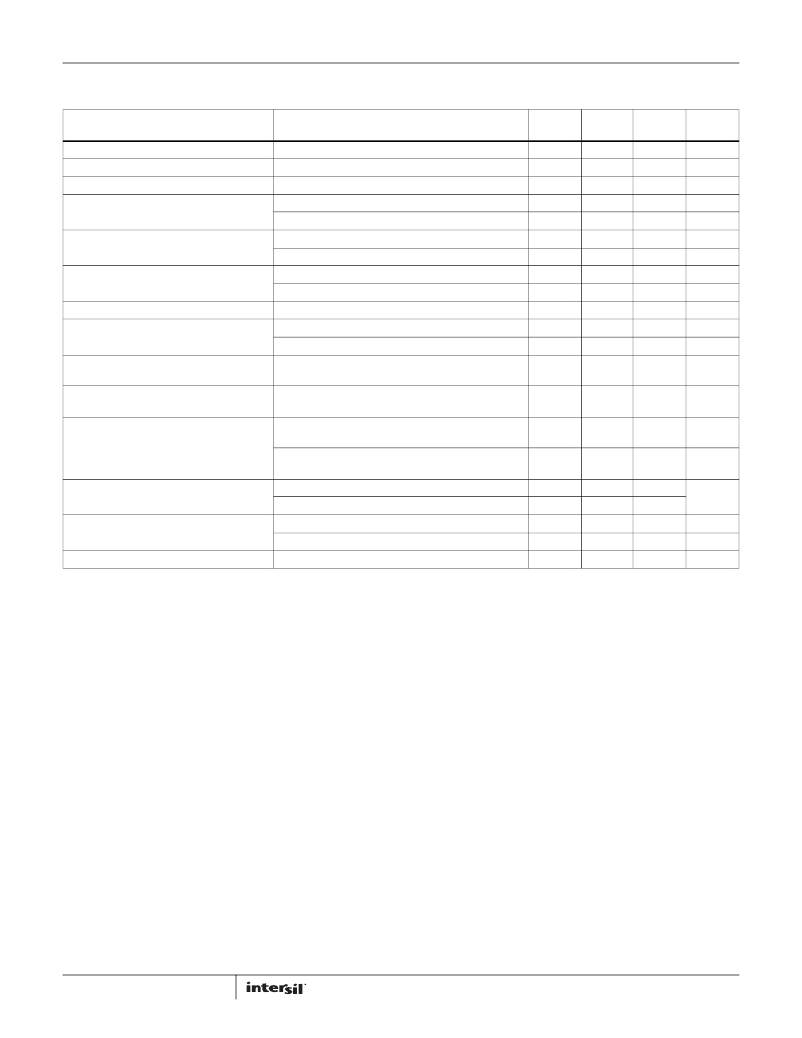

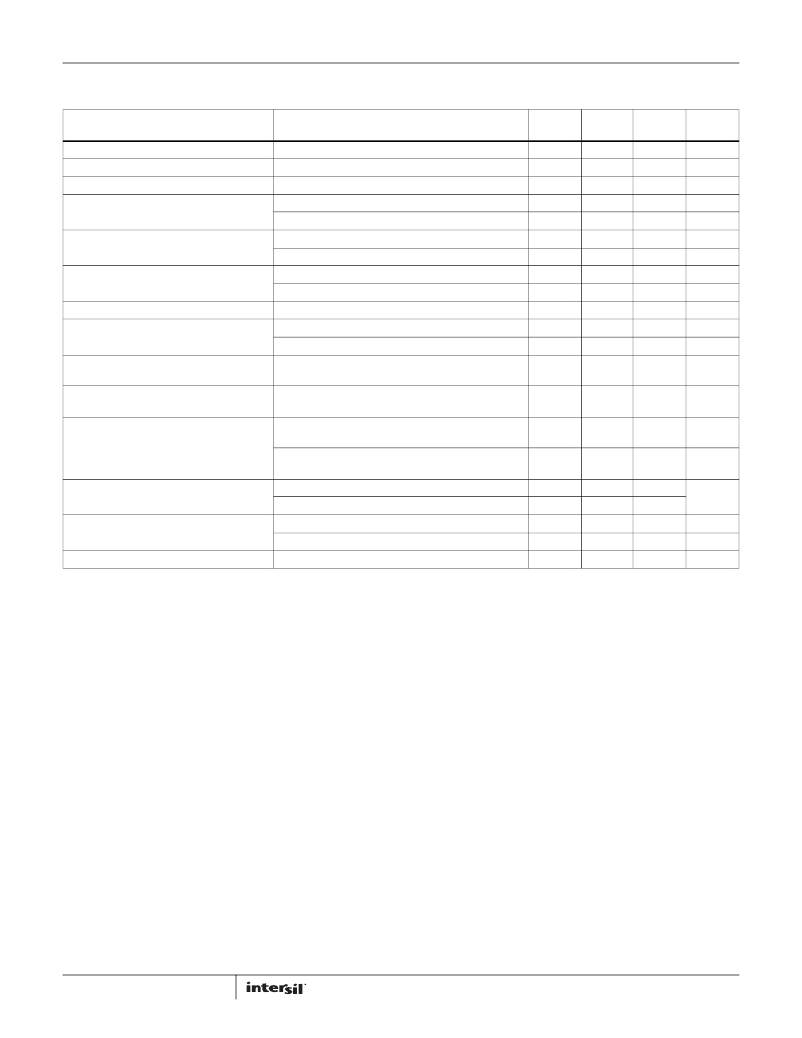

�ZL6105�

�Electrical� Specifications� V� DD� =� 12V,� T� A� =� -40°C� to� +85°C� unless� otherwise� noted.� Typical� values� are� at� T� A� =� +25°C.� Boldface� limits� apply� over�

�the� operating� temperature� range,� -40°C� to� +85°C.� (Continued)�

�MIN�

�MAX�

�PARAMETER�

�UVLO� Delay�

�Power� Good� V� OUT� Threshold�

�Power� Good� V� OUT� Hysteresis�

�Power� Good� Delay�

�VSEN� Undervoltage� Threshold�

�VSEN� Overvoltage� Threshold�

�CONDITIONS�

�Factory� default�

�Factory� default�

�Using� pin-strap� or� resistor� (Note� 16)�

�Configurable� via� I� 2� C/SMBus�

�Factory� default�

�Configurable� via� I� 2� C/SMBus�

�Factory� default�

�(Note� 19)�

�–�

�–�

�–�

�0�

�0�

�–�

�0�

�–�

�TYP�

�2.5�

�90�

�5�

�–�

�–�

�85�

�–�

�115�

�(Note� 19)�

�-�

�–�

�–�

�200�

�500�

�–�

�110�

�–�

�UNIT�

�μs�

�%� V� OUT�

�%�

�ms�

�s�

�%� V� OUT�

�%� V� OUT�

�%� V� OUT�

�VSEN� Undervoltage� Hysteresis�

�Configurable� via�

�I� 2� C/SMBus�

�0�

�–�

�–�

�5�

�115�

�–�

�%� V� OUT�

�%� V� OUT�

�VSEN� Undervoltage/Overvoltage�

�Fault� Response� Time�

�Current� Limit� Set-point� Accuracy�

�Factory� default�

�Configurable� via� I� 2� C/SMBus�

�–�

�5�

�–�

�16�

�–�

�±10�

�–�

�60�

�–�

�μs�

�μs�

�%� FS�

�(V� OUT� Referenced)�

�(Note� 17)�

�Current� Limit� Set-point� Accuracy�

�–�

�±10�

�–�

�%� FS�

�(Ground� Referenced)�

�(Note� 17)�

�Current� Limit� Protection� Delay�

�Temperature� Compensation� of�

�Current� Limit� Protection� Threshold�

�Thermal� Protection� Threshold�

�(Junction� Temperature)�

�Thermal� Protection� Hysteresis�

�Factory� default�

�Configurable� via� I� 2� C/SMBus�

�Factory� default�

�I� 2� C/SMBus�

�Configurable� via�

�Factory� default�

�Configurable� via� I� 2� C/SMBus�

�–�

�1�

�100�

�–�

�-40�

�–�

�10�

�–�

�4400�

�125�

�–�

�15�

�–�

�32�

�12700�

�–�

�125�

�–�

�t� SW�

�(Note� 18)�

�t� SW�

�(Note� 18)�

�ppm/°C�

�°C�

�°C�

�°C�

�NOTES:�

�12.� Does� not� include� margin� limits.�

�13.� Percentage� of� Full� Scale� (FS)� with� temperature� compensation� applied.�

�14.� V� OUT� measured� at� the� termination� of� the� VSEN+� and� VSEN-sense� points.�

�15.� The� device� requires� a� minimum� delay� period� following� an� enable� signal� and� prior� to� ramping� its� output� as� described� in� “Soft-Start� Delay� and� Ramp�

��16.� Factory� default� Power� Good� delay� is� set� to� the� same� value� as� the� soft-start� ramp� time.� Refer� to� “Soft-Start� Delay� and� Ramp� Times”� on� page� 14� for�

�further� restrictions� on� PG� Delay.�

�17.� Percentage� of� Full� Scale� (FS)� with� temperature� compensation� applied�

�18.� t� SW� =� 1/f� SW� ,� where� f� SW� is� the� switching� frequency.�

�19.� Compliance� to� datasheet� limits� is� assured� by� one� or� more� methods:� production� test,� characterization� and/or� design.�

�20.� Nominal� capacitance� of� logic� pins� is� 5pF.�

�9�

�FN6906.5�

�December� 19,� 2013�

�相关PDF资料 |

PDF描述 |

|---|---|

| ZLDO1117G25TA | IC REG LDO 2.5V 1A SOT223-3 |

| ZLDO330T8TA | IC REG LDO 3.3V .3A SOT223-8 |

| ZLDO485T8TA | IC REG LDO 4.85V .3A SOT223-8 |

| ZLDO500T8TA | IC REG LDO 5V .3A SOT223-8 |

| ZM331643GTC | IC MONITOR 2.68V SUPPLY SOT223 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ZL62034UBJA | 制造商:TE Connectivity 功能描述:4x6.25 Gb/s TIA/LA Receiver D |

| ZL62B | 制造商:YEASHIN 制造商全称:YEASHIN 功能描述:500 mW DO-35 Hermetically Sealed Glass Zener Voltage Regulators |

| ZL68B | 制造商:YEASHIN 制造商全称:YEASHIN 功能描述:500 mW DO-35 Hermetically Sealed Glass Zener Voltage Regulators |

| ZL6V2B | 制造商:YEASHIN 制造商全称:YEASHIN 功能描述:500 mW DO-35 Hermetically Sealed Glass Zener Voltage Regulators |

| ZL6V8B | 制造商:YEASHIN 制造商全称:YEASHIN 功能描述:500 mW DO-35 Hermetically Sealed Glass Zener Voltage Regulators |

发布紧急采购,3分钟左右您将得到回复。