- 您现在的位置:买卖IC网 > PDF目录298744 > A42MX24-3VQ100A (Electronic Theatre Controls, Inc.) 40MX and 42MX FPGA Families PDF资料下载

参数资料

| 型号: | A42MX24-3VQ100A |

| 厂商: | Electronic Theatre Controls, Inc. |

| 英文描述: | 40MX and 42MX FPGA Families |

| 中文描述: | 40MX和42MX FPGA系列 |

| 文件页数: | 17/93页 |

| 文件大小: | 854K |

| 代理商: | A42MX24-3VQ100A |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页当前第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页

24

Data Device Corporation

www.ddc-web.com

BU-6474X/6484X/6486X

J-07/05-0

BC MESSAGE SEQUENCE CONTROL

The Mini-ACE Mark3 BC message sequence control capability

enables a high degree of offloading of the host processor. This

includes using the various timing functions to enable

autonomous structuring of major and minor frames. In addition,

by implementing conditional jumps and subroutine calls, the

message sequence control processor greatly simplifies the

insertion of asynchronous, or "out-of-band" messages.

EXECUTE AND FLIP OPERATION

The Mini-ACE Mark3 BC's XQF, or "Execute and Flip" operation,

provides some unique capabilities. Following execution of this

unconditional instruction, if the condition code tests TRUE, the

BC will modify the value of the current XQF instruction's pointer

parameter by toggling bit 4 of the pointer. That is, if the selected

condition flag tests true, the value of the parameter will be

updated to the value = old address XOR 0010h. As a result, the

next time that this line in the instruction list is executed, the

Message Control/Status Block at the updated address (old

address XOR 0010h) will be processed, rather than the one at

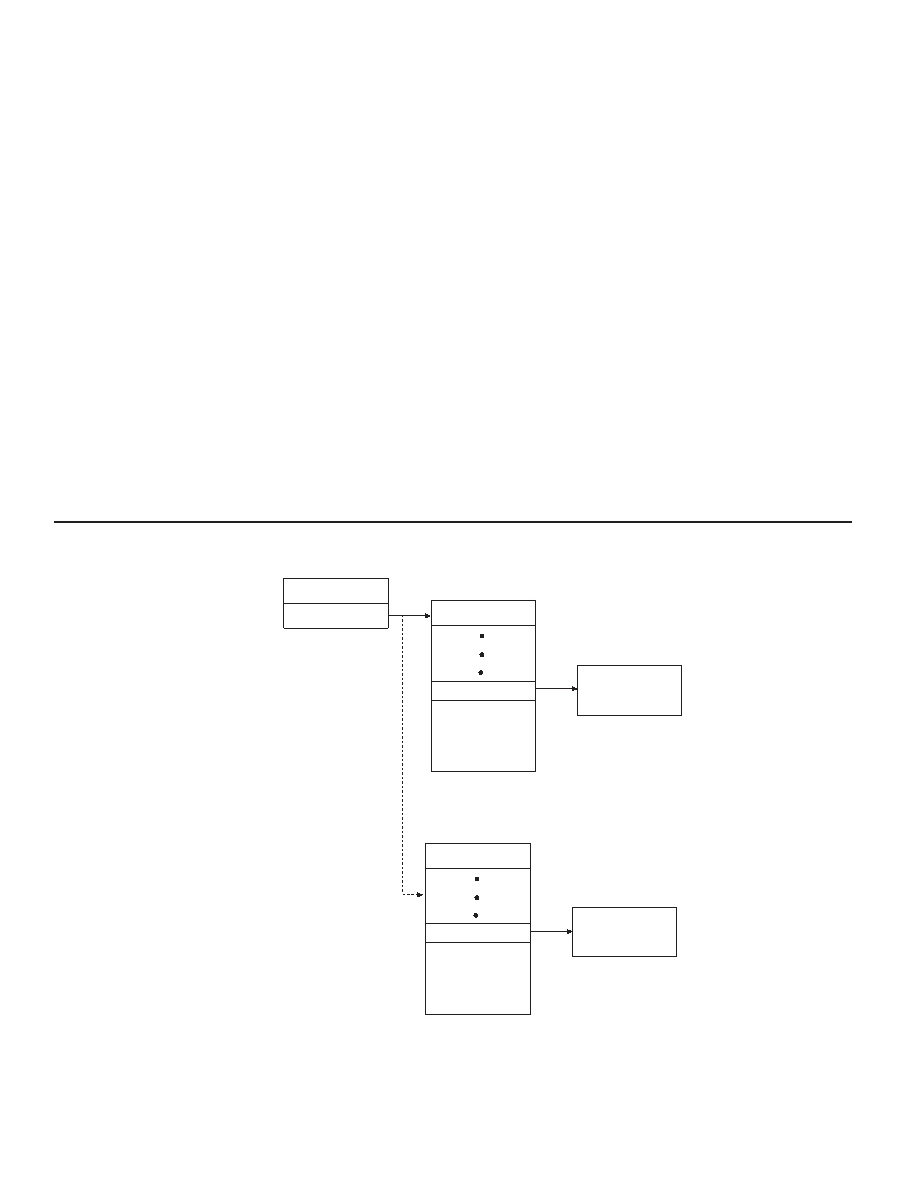

the old address. The operation of the XQF instruction is illustrat-

ed in FIGURE 4.

There are multiple ways of utilizing the "execute and flip" instruc-

tion. One is to facilitate the implementation of a double buffering

data scheme for individual messages. This allows the message

sequence control processor to "ping-pong" between a pair of

data buffers for a particular message. By doing so, the host

processor can access one of the two Data Word blocks, while the

BC reads or writes the alternate Data Word block.

A second application of the "execute and flip" capability is in con-

junction with message retries. This allows the BC to not only

switch buses when retrying a failed message, but to automati-

cally switch buses permanently for all future times that the same

message is to be processed. This not only provides a high

degree of autonomy from the host CPU, but saves BC band-

width, by eliminating the need for future attempts to process

messages on an RT's failed channel.

XQF

POINTER

XX00h

(part of) BC INSTRUCTION LIST

MESSAGE

CONTROL/STATUS

BLOCK 0

DATA BLOCK 0

XX00h

MESSAGE

CONTROL/STATUS

BLOCK 1

DATA BLOCK 1

POINTER

FIGURE 4. EXECUTE and FLIP (XQF) OPERATION

相关PDF资料 |

PDF描述 |

|---|---|

| A42MX24-3VQ100B | 40MX and 42MX FPGA Families |

| A42MX36-2PQ100B | 40MX and 42MX FPGA Families |

| A42MX36-2PQ100ES | 40MX and 42MX FPGA Families |

| A42MX36-2TQ100 | 40MX and 42MX FPGA Families |

| A42MX36-2TQ100A | 40MX and 42MX FPGA Families |

相关代理商/技术参数 |

参数描述 |

|---|---|

| A42MX24-FPL84 | 功能描述:IC FPGA MX SGL CHIP 36K 84-PLCC RoHS:否 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:MX 标准包装:40 系列:SX-A LAB/CLB数:6036 逻辑元件/单元数:- RAM 位总计:- 输入/输出数:360 门数:108000 电源电压:2.25 V ~ 5.25 V 安装类型:表面贴装 工作温度:0°C ~ 70°C 封装/外壳:484-BGA 供应商设备封装:484-FPBGA(27X27) |

| A42MX24-FPLG84 | 功能描述:IC FPGA MX SGL CHIP 36K 84-PLCC RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:MX 标准包装:40 系列:SX-A LAB/CLB数:6036 逻辑元件/单元数:- RAM 位总计:- 输入/输出数:360 门数:108000 电源电压:2.25 V ~ 5.25 V 安装类型:表面贴装 工作温度:0°C ~ 70°C 封装/外壳:484-BGA 供应商设备封装:484-FPBGA(27X27) |

| A42MX24-FPQ160 | 功能描述:IC FPGA MX SGL CHIP 36K 160-PQFP RoHS:否 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:MX 标准包装:40 系列:SX-A LAB/CLB数:6036 逻辑元件/单元数:- RAM 位总计:- 输入/输出数:360 门数:108000 电源电压:2.25 V ~ 5.25 V 安装类型:表面贴装 工作温度:0°C ~ 70°C 封装/外壳:484-BGA 供应商设备封装:484-FPBGA(27X27) |

| A42MX24-FPQ208 | 功能描述:IC FPGA MX SGL CHIP 36K 160-PQFP RoHS:否 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:MX 标准包装:40 系列:SX-A LAB/CLB数:6036 逻辑元件/单元数:- RAM 位总计:- 输入/输出数:360 门数:108000 电源电压:2.25 V ~ 5.25 V 安装类型:表面贴装 工作温度:0°C ~ 70°C 封装/外壳:484-BGA 供应商设备封装:484-FPBGA(27X27) |

| A42MX24-FPQG160 | 功能描述:IC FPGA MX SGL CHIP 36K 160-PQFP RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:MX 标准包装:40 系列:SX-A LAB/CLB数:6036 逻辑元件/单元数:- RAM 位总计:- 输入/输出数:360 门数:108000 电源电压:2.25 V ~ 5.25 V 安装类型:表面贴装 工作温度:0°C ~ 70°C 封装/外壳:484-BGA 供应商设备封装:484-FPBGA(27X27) |

发布紧急采购,3分钟左右您将得到回复。