参数资料

| 型号: | AD14060LBF-4 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 30/48页 |

| 文件大小: | 0K |

| 描述: | IC DSP CMOS 32BIT 308CQFP |

| 产品培训模块: | SHARC Processor Overview |

| 标准包装: | 1 |

| 系列: | SHARC® |

| 类型: | 浮点 |

| 接口: | 主机接口,连接端口,串行端口 |

| 时钟速率: | 40MHz |

| 非易失内存: | 外部 |

| 芯片上RAM: | 2MB |

| 电压 - 输入/输出: | 3.30V |

| 电压 - 核心: | 3.30V |

| 工作温度: | -40°C ~ 100°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 308-CBQFP |

| 供应商设备封装: | 308-CQFP(52x52) |

| 包装: | 托盘 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页当前第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页

AD14060/AD14060L

Rev. B | Page 36 of 48

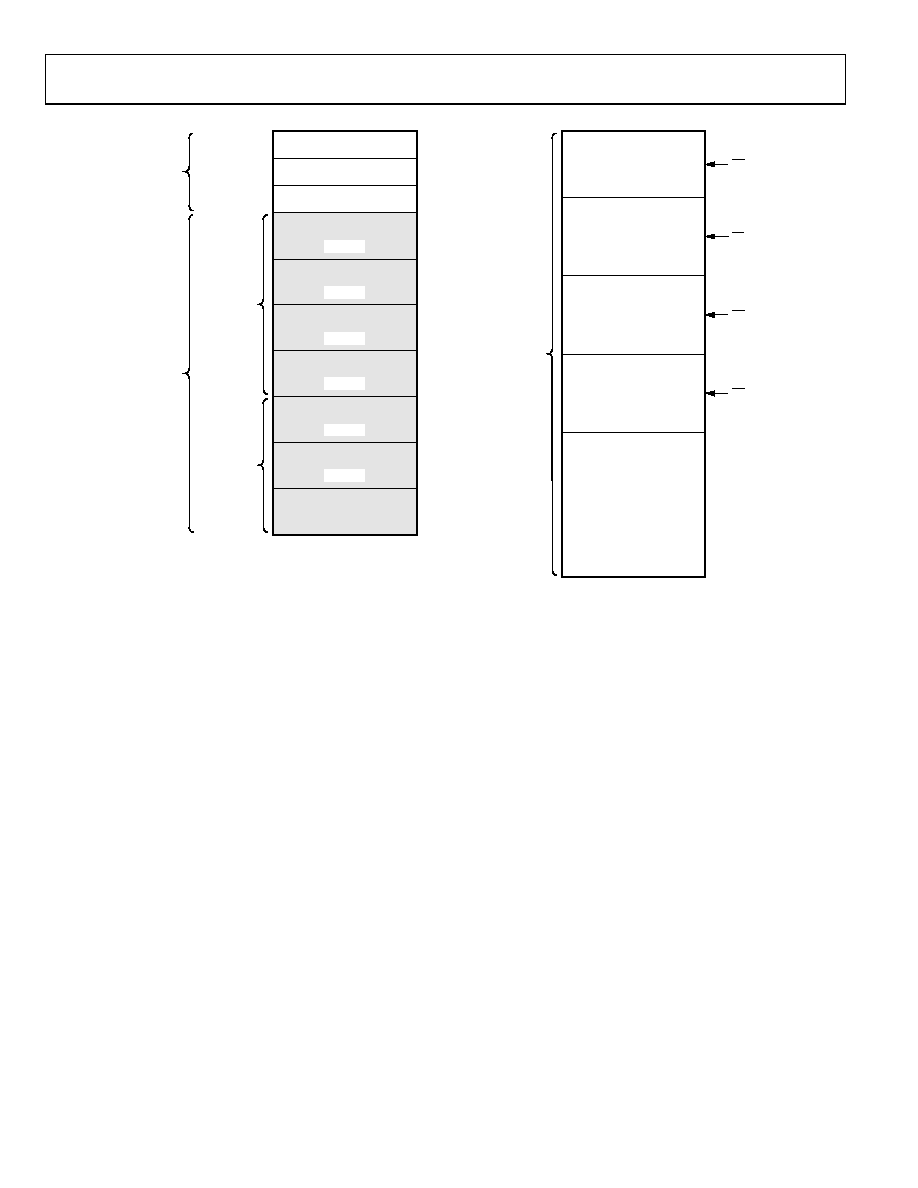

IOP REGISTERS

NORMAL WORD ADDRESSING

0x0000 0000

0x0002 0000

0x0004 0000

0x0008 0000

0x0010 0000

0x0018 0000

0x0020 0000

0x0028 0000

0x0030 0000

0x0038 0000

0x003F FFFF

SHORT WORD ADDRESSING

INTERNAL MEMORY SPACE

OF SHARC_B

ID = 010

INTERNAL MEMORY SPACE

OF SHARC_A

ID = 001

INTERNAL MEMORY SPACE

OF SHARC_C

ID = 011

INTERNAL MEMORY SPACE

OF SHARC_D

ID = 100

INTERNAL MEMORY SPACE

OF ADSP-2106x

ID = 101

INTERNAL MEMORY SPACE

OF ADSP-2106x

ID = 110

BROADCAST WRITE

TO ALL

ADSP-2106xs

NORMAL WORD ADDRESSING: 32-BIT DATA WORDS

48-BIT INSTRUCTION WORDS

SHORT WORD ADDRESSING: 16-BIT DATA WORDS

MS0

0x0040 0000

0xFFFF FFFF

MULTIPROCESSOR

MEMORY SPACE

BANK 0

BANK 1

BANK 2

DRAM

(OPTIONAL)

BANK 3

NONBANKED

MS1

MS2

MS3

BANK SIZE IS

SELECTED BY

MSIZE BIT FIELD

OF SYSCON

REGISTER

EXTERNAL

MEMORY

SPACE

INTERNAL

MEMORY SPACE

(INDIVIDUAL

SHARCs)

INTERNAL

TO AD14060

EXTERNAL

TO AD14060

00667-004

Figure 23. AD14060/AD14060L Memory Map

Bus locking is possible, allowing indivisible read-modify-write

sequences for semaphores. In either the fixed or rotating

priority scheme, it is also possible to limit the number of cycles

that the master can use to control the bus. The AD14060/

AD14060L provides the option of using the core priority access

(CPA) mode of the SHARC. Using the CPA signal allows

external bus accesses by the core processor of a slave SHARC to

take priority over ongoing DMA transfers. Also, each SHARC

can broadcast write to all other SHARCs simultaneously,

allowing the implementation of reflective semaphores.

The bus master can communicate with slave SHARCs by

writing messages to their internal IOP registers. The MSRG0 to

MSRG7 registers are general-purpose registers that can be used

for convenient message passing, semaphores, and resource

sharing among the SHARCs. For message passing, the master

communicates with a slave by writing and/or reading any of the

eight message registers on the slave. For vector interrupts, the

master can issue a vector interrupt to a slave by writing the

address of an interrupt service routine to the slave’s VIRPT

register. This causes an immediate high priority interrupt on the

slave, which, when serviced, causes it to branch to the specified

service routine.

OFF-MODULE MEMORY AND PERIPHERALS

INTERFACE

The AD14060/AD14060L’s external port provides the interface

to off-module memory and peripherals (see Figure 24). This

port consists of the complete external port bus of the SHARC,

bused in common among the four SHARCs.

The 4-gigaword off-module address space is included in the

ADSP-14060’s unified address space. Addressing of external

memory devices is facilitated by each SHARC internally

decoding the high-order address lines to generate memory-

bank select signals. Separate control lines are also generated for

simplified addressing of page-mode DRAM. The AD14060/

AD14060L also supports programmable memory wait states

and external memory acknowledge controls to allow interfacing

to DRAM and peripherals with variable access, hold, and

disable time requirements.

相关PDF资料 |

PDF描述 |

|---|---|

| AD1833AASTZ-REEL | IC DAC AUDIO 24BIT 6CH 48LQFP |

| AD1835AASZ | IC CODEC 2ADC/8DAC 24BIT 52-MQFP |

| AD1836ACSZ | IC CODEC 4ADC/6DAC 24 BIT 52MQFP |

| AD1838AASZ | IC CODEC 2ADC/6DAC 24 BIT 52MQFP |

| AD1851RZ-J | IC DAC AUDIO FASTSET 16B 16SOIC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD14160 | 制造商:AD 制造商全称:Analog Devices 功能描述:Quad-SHARC DSP Multiprocessor Family |

| AD14160BB-4 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| AD14160KB-4 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| AD14160L | 制造商:AD 制造商全称:Analog Devices 功能描述:Quad-SHARC DSP Multiprocessor Family |

| AD14160LBB-4 | 制造商:AD 制造商全称:Analog Devices 功能描述:Quad-SHARC DSP Multiprocessor Family |

发布紧急采购,3分钟左右您将得到回复。