- 您现在的位置:买卖IC网 > PDF目录373890 > AD6634BBC (ANALOG DEVICES INC) 80 MSPS, Dual-Channel WCDMA Receive Signal Processor (RSP) PDF资料下载

参数资料

| 型号: | AD6634BBC |

| 厂商: | ANALOG DEVICES INC |

| 元件分类: | 无绳电话/电话 |

| 英文描述: | 80 MSPS, Dual-Channel WCDMA Receive Signal Processor (RSP) |

| 中文描述: | TELECOM, CELLULAR, BASEBAND CIRCUIT, PBGA196 |

| 封装: | 15 MM X 15 MM, BGA-196 |

| 文件页数: | 49/52页 |

| 文件大小: | 925K |

| 代理商: | AD6634BBC |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页当前第49页第50页第51页第52页

REV. 0

AD6634

–49–

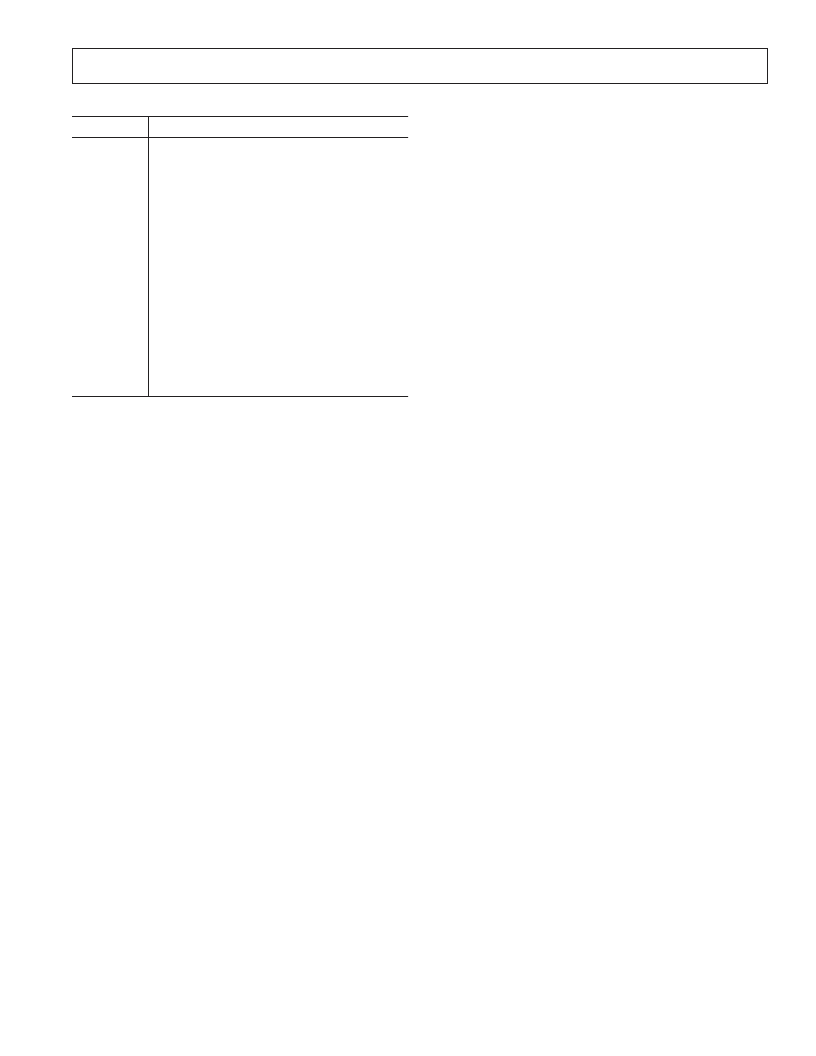

Table XVII. Microport Instructions

Instruction

Comment

0000

0001

0010

0100

1000

All chips and all channels will get the access.

Channel 0, 1, 2 of all chips will get the access.

Channel 1, 2, 3 of all chips will get the access.

All chips will get the access.

*

All chips with Chip_ID[3:0] = xxx0 will get the

access.

*

All chips with Chip_ID[3:0] = xxx1 will get the

access.

*

All chips with Chip_ID[3:0] = xx00 will get the

access.

*

All chips with Chip_ID[3:0] = xx01 will get the

access.

*

All chips with Chip_ID[3:0] = xx10 will get the

access.

*

All chips with Chip_ID[3:0] = xx11 will get the

access.

*

1001

1100

1101

1110

1111

*

A[9:8] bits control which channel is decoded for the access.

When broadcast is enabled (Bit 6 set high), readback is not valid

because of the potential for internal bus contention. Therefore,

if readback is subsequently desired, the broadcast bit should be

set low.

Bits 1–0 of this register are address bits that decode which of the

four channels are being accessed. If the Instruction bits decode

an access to multiple channels then these bits are ignored. If the

instruction decodes an access to a subset of chips, then the A[9:8]

bits will otherwise determine the channel being accessed.

Channel Address Register (CAR)

This register represents the 8-bit internal address of each channel.

If the Auto-Increment bit of the ACR is 1, this value will be incre-

mented after every access to the DR0 register, which will in turn

access the location pointed to by this address. The Channel Address

register cannot be read back while the Broadcast bit is set high.

SOFT_SYNC Control Register

External Address [5] is the SOFT_SYNC control register and is

write only.

Bits 0–3 of this register are the SOFT_SYNC control bits. These pins

may be written to by the controller to initiate the synchronization

of a selected channel. Although there are four inputs, these do not

necessarily go to the channel of the same number. This is fully

configurable at the channel level as to which bit to look at. All

four channels may be configured to synchronize from a single

position, or they may be paired or all independent.

Bit 4 determines if the synchronization is to apply to a chip start.

If this bit is set, a chip start will be initiated.

Bit 5 determines if the synchronization is to apply to a chip hop.

If this bit is set, the NCO frequency will be updated when the

SOFT_SYNC occurs.

Bit 6 configures how the internal databus is configured. If this bit

is set low, the internal ADC databuses are configured normally.

If this bit is set, the internal test signals are selected. The internal

test signals are configured in Bit 7 of this register.

Bit 7 if set clear, a negative full scale signal is generated and made

available to the internal databus. If this bit is high, internal

pseudo-random sequence generator is enabled and this data is

available to the internal databus. The combined functions of

Bits 6 and 7 facilitate verification of a given filter design. Also, in

conjunction with the MISR registers allows for detailed in-system

chip testing. In conjunction with the JTAG test board, very high

levels of chip verification can be done during system test, both

in the factory and field.

PIN_SYNC Control Register

External Address [4] is the PIN_SYNC control register and is

write only.

Bits 0–3 of this register are the SYNC_EN control bits. These pins

may be written to by the controller to allow pin synchronization

of a selected sync channel. Although there are four inputs, these

do not necessarily go to the channel of the same number. This is

fully configurable at the channel level as to which bit to look at.

All four channels may be configured to synchronize from a

single position, or they may be paired or all independent.

Bit 4 determines if the synchronization is to apply to a chip

start. If this bit is set, a chip start will be initiated when the

PIN_SYNC occurs.

Bit 5 determines if the synchronization is to apply to a chip hop.

If this bit is set, the NCO frequency will be updated when the

when the PIN_SYNC occurs.

Bit 6 is used to ignore repetitive synchronization signals. In

some applications, this signal may occur periodically. If this bit

is clear, each PIN_SYNC will restart/hop the channel. If this bit

is set, only the first occurrence will cause the chip to take action.

Bit 7 is used with Bits 6 and 7 of external address 5. When this

bit is cleared, the data supplied to the internal databus simulates

a normal ADC. When this bit is set, the data supplied is in the

form of a time multiplexed ADC such as the AD6600 (this

allows the equivalent of testing in the 4-channel input mode).

Internally, when set, this bit forces the IEN pin to toggle as if it

were driven by the A/B signal of the AD6600.

SLEEP Control Register

External Address [3] is the Sleep register.

Bits 3–0 control the state of each of the channels. Each bit corre-

sponds to one of the possible RSP channels within the device. If this

bit is cleared, the channel operates normally. However, when this

bit is set, the indicated channel enters a low power Sleep mode.

Bit 4 is reserved and should always be set to 0.

Bit 5 allows access to the Input/Output Control Port Registers.

When this bit is set low, the channel memory map is accessed.

However, when this bit is set high, it allows access to the

Input/Output Port Control Registers. When this bit is set high,

the value in external address 6 (CAR) points to the memory map

for the Input/Output Port Control Registers instead of the

normal channel memory map. See Input and Output Port Control

Registers in the respective Input and Output memory map sections.

Bits 6–7 are reserved and should be set low.

Data Address Registers

External Address [2–0] forms the data registers DR2, DR1, and

DR0, respectively. All internal data-words have widths that are

less than or equal to 20 bits. Accesses to External Address [0]

DR0 trigger an internal access to the AD6634 based on the

address indicated in the ACR and CAR. Thus during writes to the

internal registers, External Address [0] DR0 must be written last.

At this point data is transferred to the internal memory indicated

in A[9:0]. Reads are performed in the opposite direction. Once the

相关PDF资料 |

PDF描述 |

|---|---|

| AD6634PCB | 80 MSPS, Dual-Channel WCDMA Receive Signal Processor (RSP) |

| AD6635 | 4-Channel, 80 MSPS WCDMA Receive Signal Processor (RSP) |

| AD6635BB | 4-Channel, 80 MSPS WCDMA Receive Signal Processor (RSP) |

| AD6636 | 150 MSPS Wideband Digital Down-Converter (DDC) |

| AD6636BBCZ1 | 150 MSPS Wideband Digital Down-Converter (DDC) |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD6634BBCZ | 功能描述:IC RSP 80MSPS DUAL 196CSPBGA RoHS:是 类别:RF/IF 和 RFID >> RF 混频器 系列:AD6634 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:100 系列:- RF 型:W-CDMA 频率:2.11GHz ~ 2.17GHz 混频器数目:1 增益:17dB 噪音数据:2.2dB 次要属性:- 电流 - 电源:11.7mA 电源电压:2.7 V ~ 3.3 V 包装:托盘 封装/外壳:12-VFQFN 裸露焊盘 供应商设备封装:12-QFN-EP(3x3) |

| AD6634BC/PCB | 制造商:Analog Devices 功能描述:WCDMA RECEIVE SGNL PROCESSOR - Bulk |

| AD6634PCB | 制造商:AD 制造商全称:Analog Devices 功能描述:80 MSPS, Dual-Channel WCDMA Receive Signal Processor (RSP) |

| AD6635 | 制造商:AD 制造商全称:Analog Devices 功能描述:4-Channel, 80 MSPS WCDMA Receive Signal Processor (RSP) |

| AD6635BB | 功能描述:IC RSP 80MSPS QUAD 324-BGA RoHS:否 类别:RF/IF 和 RFID >> RF 混频器 系列:AD6635 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:100 系列:- RF 型:W-CDMA 频率:2.11GHz ~ 2.17GHz 混频器数目:1 增益:17dB 噪音数据:2.2dB 次要属性:- 电流 - 电源:11.7mA 电源电压:2.7 V ~ 3.3 V 包装:托盘 封装/外壳:12-VFQFN 裸露焊盘 供应商设备封装:12-QFN-EP(3x3) |

发布紧急采购,3分钟左右您将得到回复。