- 您现在的位置:买卖IC网 > PDF目录1900 > ADSP-TS203SABP-050 (Analog Devices Inc)IC DSP FLOAT/FIXED 500MHZ 576BGA PDF资料下载

参数资料

| 型号: | ADSP-TS203SABP-050 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 3/48页 |

| 文件大小: | 0K |

| 描述: | IC DSP FLOAT/FIXED 500MHZ 576BGA |

| 标准包装: | 1 |

| 系列: | TigerSHARC® |

| 类型: | 定点/浮点 |

| 接口: | 主机接口,连接端口,多处理器 |

| 时钟速率: | 500MHz |

| 非易失内存: | 外部 |

| 芯片上RAM: | 512kB |

| 电压 - 输入/输出: | 2.50V |

| 电压 - 核心: | 1.05V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 576-BBGA 裸露焊盘 |

| 供应商设备封装: | 576-BGA-ED(25x25) |

| 包装: | 托盘 |

| 其它名称: | ADSP-TS203SABP050 ADSP-TS203SABP050-ND |

第1页第2页当前第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页

Rev. D

|

Page 11 of 48

|

May 2012

PIN FUNCTION DESCRIPTIONS

While most of the ADSP-TS203S processor’s input pins are nor-

mally synchronous—tied to a specific clock—a few are

asynchronous. For these asynchronous signals, an on-chip syn-

chronization circuit prevents metastability problems. Use the ac

specification for asynchronous signals when the system design

requires predictable, cycle-by-cycle behavior for these signals.

The output pins can be three-stated during normal operation.

The processor three-states all output during reset, allowing

these pins to get to their internal pull-up or pull-down state.

Some pins have an internal pull-up or pull-down resistor (±30%

tolerance) that maintains a known value during transitions

between different drivers.

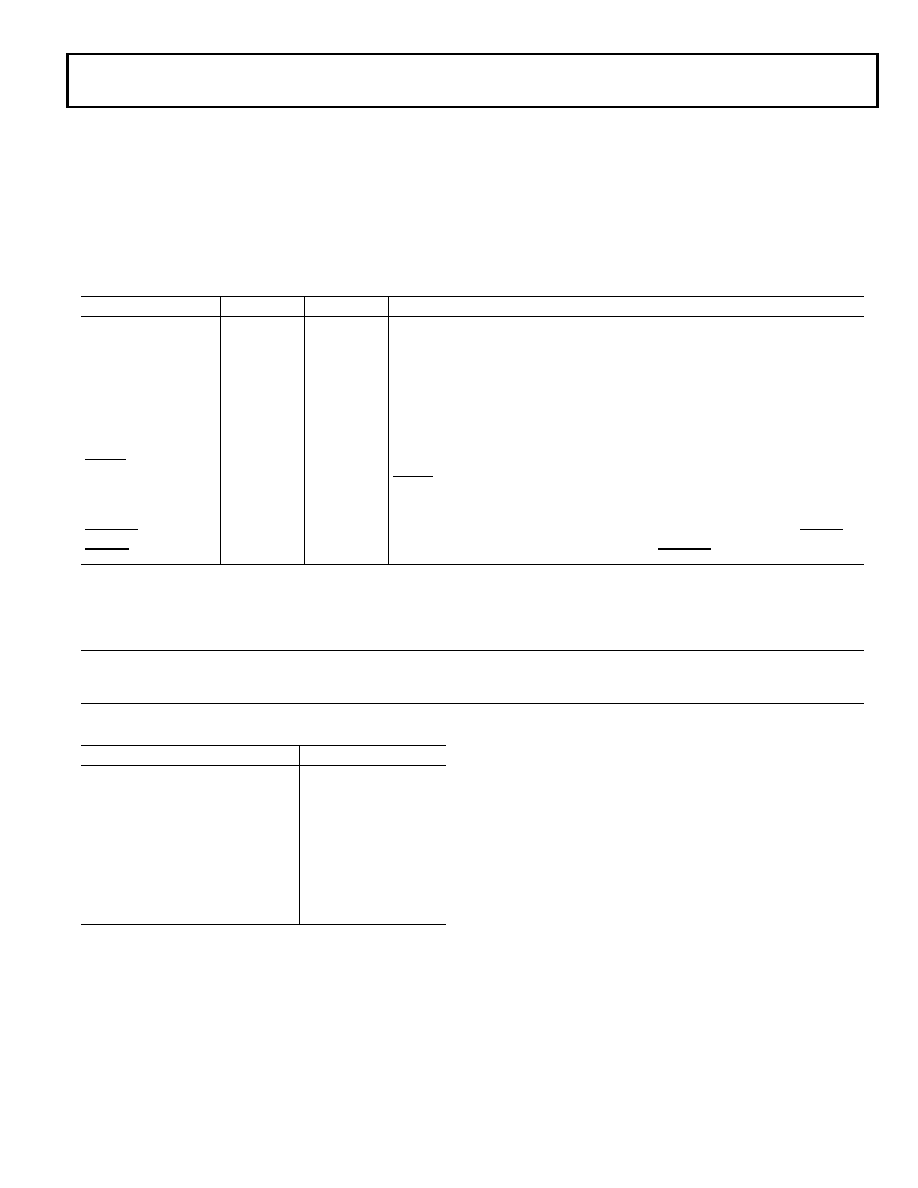

Table 3. Pin Definitions—Clocks and Reset

Signal

Type

Term

Description

SCLKRAT2–0

I (pd)

na

Core Clock Ratio. The processor’s core clock (CCLK) rate = n

× SCLK, where n is user-

programmable using the SCLKRATx pins to the values shown in Table 4. These pins

may change only during reset; connect these pins to VDD_IO or VSS. All reset specifi-

(CCLK) is the instruction cycle rate.

SCLK

I

na

System Clock Input. The processor’s system input clock for cluster bus. The core

clock rate is user-programmable using the SCLKRATx pins. For more information,

RST_IN

I/A

na

Reset. Sets the processor to a known state and causes program to be in idle state.

RST_IN must be asserted a specified time according to the type of reset operation.

RST_OUT

O

na

Reset Output. Indicates that the processor reset is complete. Connect to POR_IN.

POR_IN

I/A

na

Power-On Reset for internal DRAM. Connect to RST_OUT.

I = input; A = asynchronous; O = output; OD = open-drain output; T = three-state; P = power supply; G = ground; pd = internal pull-down

5kΩ; pu = internal pull-up 5 kΩ; pd_0 = internal pull-down 5 kΩ on processor ID = 0; pu_0 = internal pull-up 5 kΩ on processor ID = 0;

pu_od_0 = internal pull-up 500 Ω on processor ID = 0; pd_m = internal pull-down 5 kΩ on processor bus master; pu_m = internal pull-up

5 kΩ on processor bus master; pu_ad = internal pull-up 40 kΩ. For more pull-down and pull-up information, see Electrical Characteristics

Term (termination of unused pins) column symbols: epd = external pull-down approximately 5 kΩ to VSS; epu = external pull-up

approximately 5 kΩ to VDD_IO, nc = not connected; na = not applicable (always used); VDD_IO = connect directly to VDD_IO; VSS = connect

directly to VSS

Table 4. SCLK Ratio

SCLKRAT2–0

Ratio

000

(default)

4

001

5

010

6

011

7

100

8

101

10

110

12

111

Reserved

相关PDF资料 |

PDF描述 |

|---|---|

| ADUC7021BCPZ62-RL7 | IC MCU 12BIT 1MSPS UART 40-LFCSP |

| ADUC7023BCPZ62I-R7 | IC MCU 12BIT 62KB FLASH 32LFCSP |

| ADUC7024BCPZ62 | IC MCU FLSH 62K ANLG I/O 64LFCSP |

| ADUC7032BSTZ-88 | IC MCU 96K FLASH DUAL 48LQFP |

| ADUC7032BSTZ-8V-RL | IC BATTERY SENSOR PREC 48-LQFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADSP-TS203SABP-05X | 制造商:Analog Devices 功能描述: |

| ADSP-TS203SABPZ050 | 功能描述:IC PROCESSOR 500MHZ 576BGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - DSP(数字式信号处理器) 系列:TigerSHARC® 标准包装:2 系列:StarCore 类型:SC140 内核 接口:DSI,以太网,RS-232 时钟速率:400MHz 非易失内存:外部 芯片上RAM:1.436MB 电压 - 输入/输出:3.30V 电压 - 核心:1.20V 工作温度:-40°C ~ 105°C 安装类型:表面贴装 封装/外壳:431-BFBGA,FCBGA 供应商设备封装:431-FCPBGA(20x20) 包装:托盘 |

| ADSP-TS203SBBPZ050 | 制造商:Analog Devices 功能描述:DSP - Bulk |

| ADSQ-1410 | 制造商:MURATA-PS 制造商全称:Murata Power Solutions Inc. 功能描述:Quad 14-Bit, 10 MSPS Sampling A/D Converter |

| ADSQ-1410-C | 制造商:MURATA-PS 制造商全称:Murata Power Solutions Inc. 功能描述:Quad 14-Bit, 10 MSPS Sampling A/D Converter |

发布紧急采购,3分钟左右您将得到回复。