- 您现在的位置:买卖IC网 > PDF目录1900 > ADSP-TS203SABP-050 (Analog Devices Inc)IC DSP FLOAT/FIXED 500MHZ 576BGA PDF资料下载

参数资料

| 型号: | ADSP-TS203SABP-050 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 5/48页 |

| 文件大小: | 0K |

| 描述: | IC DSP FLOAT/FIXED 500MHZ 576BGA |

| 标准包装: | 1 |

| 系列: | TigerSHARC® |

| 类型: | 定点/浮点 |

| 接口: | 主机接口,连接端口,多处理器 |

| 时钟速率: | 500MHz |

| 非易失内存: | 外部 |

| 芯片上RAM: | 512kB |

| 电压 - 输入/输出: | 2.50V |

| 电压 - 核心: | 1.05V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 576-BBGA 裸露焊盘 |

| 供应商设备封装: | 576-BGA-ED(25x25) |

| 包装: | 托盘 |

| 其它名称: | ADSP-TS203SABP050 ADSP-TS203SABP050-ND |

第1页第2页第3页第4页当前第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页

Rev. D

|

Page 13 of 48

|

May 2012

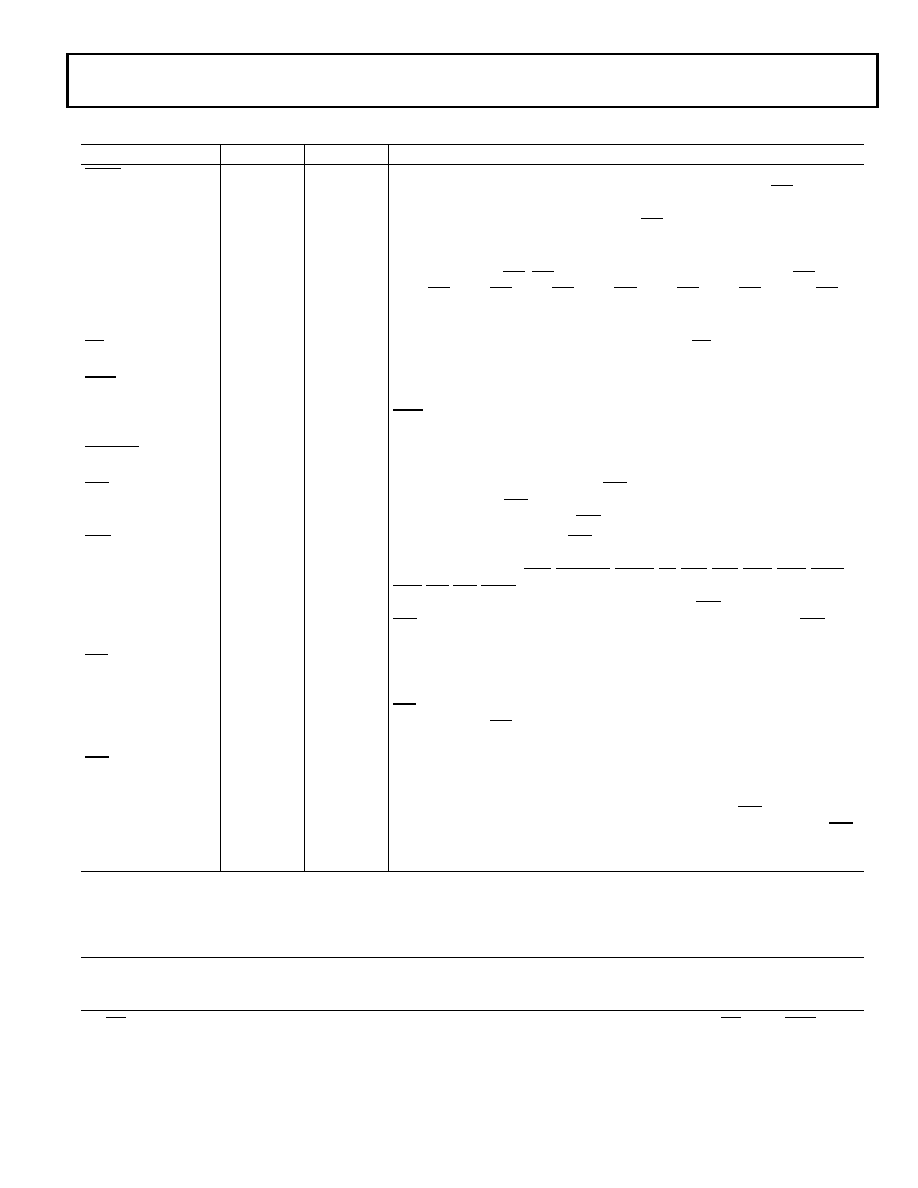

Table 6. Pin Definitions—External Port Arbitration

Signal

Type

Term

Description

BR7–0

I/O

Multiprocessing Bus Request Pins. Used by the processors in a multiprocessor

system to arbitrate for bus mastership. Each processor drives its own BRx line (corre-

sponding to the value of its ID2–0 inputs) and monitors all others. In systems with

fewer than eight processors, set the unused BRx pins high (VDD_IO).

ID2–0

I (pd)

na

Multiprocessor ID. Indicates the processor’s ID, from which the processor deter-

mines its order in a multiprocessor system. These pins also indicate to the processor

which bus request (BR0–BR7) to assert when requesting the bus: 000 = BR0,

001 = BR1, 010 = BR2, 011 = BR3, 100 = BR4, 101 = BR5, 110 = BR6, or 111 = BR7.

ID2–0 must have a constant value during system operation and can change during

reset only.

BM

O

na

Bus Master. The current bus master processor asserts BM. For debugging only. At

reset this is a strap pin. For more information, see Table 16 on Page 18.

BOFF

I

epu

Back Off. A deadlock situation can occur when the host and a processor try to read

from each other’s bus at the same time. When deadlock occurs, the host can assert

BOFF to force the processor to relinquish the bus before completing its outstanding

transaction.

BUSLOCK

O/T

(pu_0)

na

Bus Lock Indication. Provides an indication that the current bus master has locked

the bus. At reset, this is a strap pin. For more information, see Table 16 on Page 18.

HBR

I

epu

Host Bus Request. A host must assert HBR to request control of the processor’s

external bus. When HBR is asserted in a multiprocessing system, the bus master

relinquishes the bus and asserts HBG once the outstanding transaction is finished.

HBG

I/O/T

(pu_0)

epu2

Host Bus Grant. Acknowledges HBR and indicates that the host can take control of

the external bus. When relinquishing the bus, the master processor three-states the

ADDR31–0, DATA31–0, MSH, MSSD3–0, MS1–0, RD, WRL, BMS, BRST, IORD, IOWR,

IOEN, RAS, CAS, SDWE, SDA10, SDCKE, LDQM, and TM4 pins, and the processor puts

the SDRAM in self-refresh mode. The processor asserts HBG until the host deasserts

HBR. In multiprocessor systems, the current bus master processor drives HBG, and

all slave processors monitor it.

CPA

I/O/OD

(pu_od_0)

epu2

Core Priority Access. Asserted while the processor’s core accesses external memory.

This pin enables a slave processor to interrupt a master processor’s background

DMA transfers and gain control of the external bus for core-initiated transactions.

CPA is an open-drain output, connected to all DSPs in the system. If not required in

the system, leave CPA unconnected (external pull-ups will be required for processor

ID = 1 through ID = 7).

DPA

I/O/OD

(pu_od_0)

epu2

DMA Priority Access. Asserted while a high priority processor DMA channel accesses

external memory. This pin enables a high priority DMA channel on a slave processor

to interrupt transfers of a normal priority DMA channel on a master processor and

gain control of the external bus for DMA-initiated transactions. DPA is an open-drain

output, connected to all DSPs in the system. If not required in the system, leave DPA

unconnected (external pull-ups will be required for processor ID = 1 through

ID = 7).

I = input; A = asynchronous; O = output; OD = open-drain output; T = three-state; P = power supply; G = ground; pd = internal pull-down

5kΩ; pu = internal pull-up 5 kΩ; pd_0 = internal pull-down 5 kΩ on processor ID = 0; pu_0 = internal pull-up 5 kΩ on processor ID = 0;

pu_od_0 = internal pull-up 500 Ω on processor ID = 0; pd_m = internal pull-down 5 kΩ on processor bus master; pu_m = internal pull-up

5 kΩ on processor bus master; pu_ad = internal pull-up 40 kΩ. For more pull-down and pull-up information, see Electrical Characteristics

Term (termination of unused pins) column symbols: epd = external pull-down approximately 5 kΩ to VSS; epu = external pull-up

approximately 5 kΩ to VDD_IO, nc = not connected; na = not applicable (always used); VDD_IO = connect directly to VDD_IO; VSS = connect

directly to VSS

1 The BRx pin matching the ID2–0 input selection for the processor should be left nc if unused. For example, the processor with ID = 000 has BR0 = nc and BR7–1 = VDD_IO.

2 This external pull-up resistor may be omitted for the ID = 000 TigerSHARC processor.

相关PDF资料 |

PDF描述 |

|---|---|

| ADUC7021BCPZ62-RL7 | IC MCU 12BIT 1MSPS UART 40-LFCSP |

| ADUC7023BCPZ62I-R7 | IC MCU 12BIT 62KB FLASH 32LFCSP |

| ADUC7024BCPZ62 | IC MCU FLSH 62K ANLG I/O 64LFCSP |

| ADUC7032BSTZ-88 | IC MCU 96K FLASH DUAL 48LQFP |

| ADUC7032BSTZ-8V-RL | IC BATTERY SENSOR PREC 48-LQFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADSP-TS203SABP-05X | 制造商:Analog Devices 功能描述: |

| ADSP-TS203SABPZ050 | 功能描述:IC PROCESSOR 500MHZ 576BGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - DSP(数字式信号处理器) 系列:TigerSHARC® 标准包装:2 系列:StarCore 类型:SC140 内核 接口:DSI,以太网,RS-232 时钟速率:400MHz 非易失内存:外部 芯片上RAM:1.436MB 电压 - 输入/输出:3.30V 电压 - 核心:1.20V 工作温度:-40°C ~ 105°C 安装类型:表面贴装 封装/外壳:431-BFBGA,FCBGA 供应商设备封装:431-FCPBGA(20x20) 包装:托盘 |

| ADSP-TS203SBBPZ050 | 制造商:Analog Devices 功能描述:DSP - Bulk |

| ADSQ-1410 | 制造商:MURATA-PS 制造商全称:Murata Power Solutions Inc. 功能描述:Quad 14-Bit, 10 MSPS Sampling A/D Converter |

| ADSQ-1410-C | 制造商:MURATA-PS 制造商全称:Murata Power Solutions Inc. 功能描述:Quad 14-Bit, 10 MSPS Sampling A/D Converter |

发布紧急采购,3分钟左右您将得到回复。