- 您现在的位置:买卖IC网 > PDF目录11791 > ADUC7129BSTZ126-RL (Analog Devices Inc)IC DAS MCU ARM7 ADC/DDS 80-LQFP PDF资料下载

参数资料

| 型号: | ADUC7129BSTZ126-RL |

| 厂商: | Analog Devices Inc |

| 文件页数: | 71/92页 |

| 文件大小: | 0K |

| 描述: | IC DAS MCU ARM7 ADC/DDS 80-LQFP |

| 产品培训模块: | ARM7 Applications & Tools Intro to ARM7 Core & Microconverters Process Control Direct Digital Synthesis Tutorial Series (1 of 7): Introduction |

| 标准包装: | 1 |

| 系列: | MicroConverter® ADuC7xxx |

| 核心处理器: | ARM7 |

| 芯体尺寸: | 16/32-位 |

| 速度: | 41.78MHz |

| 连通性: | EBI/EMI,I²C,SPI,UART/USART |

| 外围设备: | PLA,POR,PWM,PSM,温度传感器,WDT |

| 输入/输出数: | 38 |

| 程序存储器容量: | 126KB(63K x 16) |

| 程序存储器类型: | 闪存 |

| RAM 容量: | 8K x 8 |

| 电压 - 电源 (Vcc/Vdd): | 3 V ~ 3.6 V |

| 数据转换器: | A/D 10x12b; D/A 1x10b |

| 振荡器型: | 内部 |

| 工作温度: | -40°C ~ 125°C |

| 封装/外壳: | 80-LQFP |

| 包装: | 标准包装 |

| 其它名称: | ADUC7129BSTZ126-RLDKR |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页当前第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页

ADuC7128/ADuC7129

Rev. 0 | Page 73 of 92

Programmed Interrupts

As the programmed interrupts are nonmaskable, they are

controlled by the SWICFG register that writes into both the

IRQSTA and IRQSIG registers and/or FIQSTA and FIQSIG

registers at the same time. The 32-bit register dedicated to

software interrupt is SWICFG described in Table 106. This

MMR allows the control of programmed source interrupt.

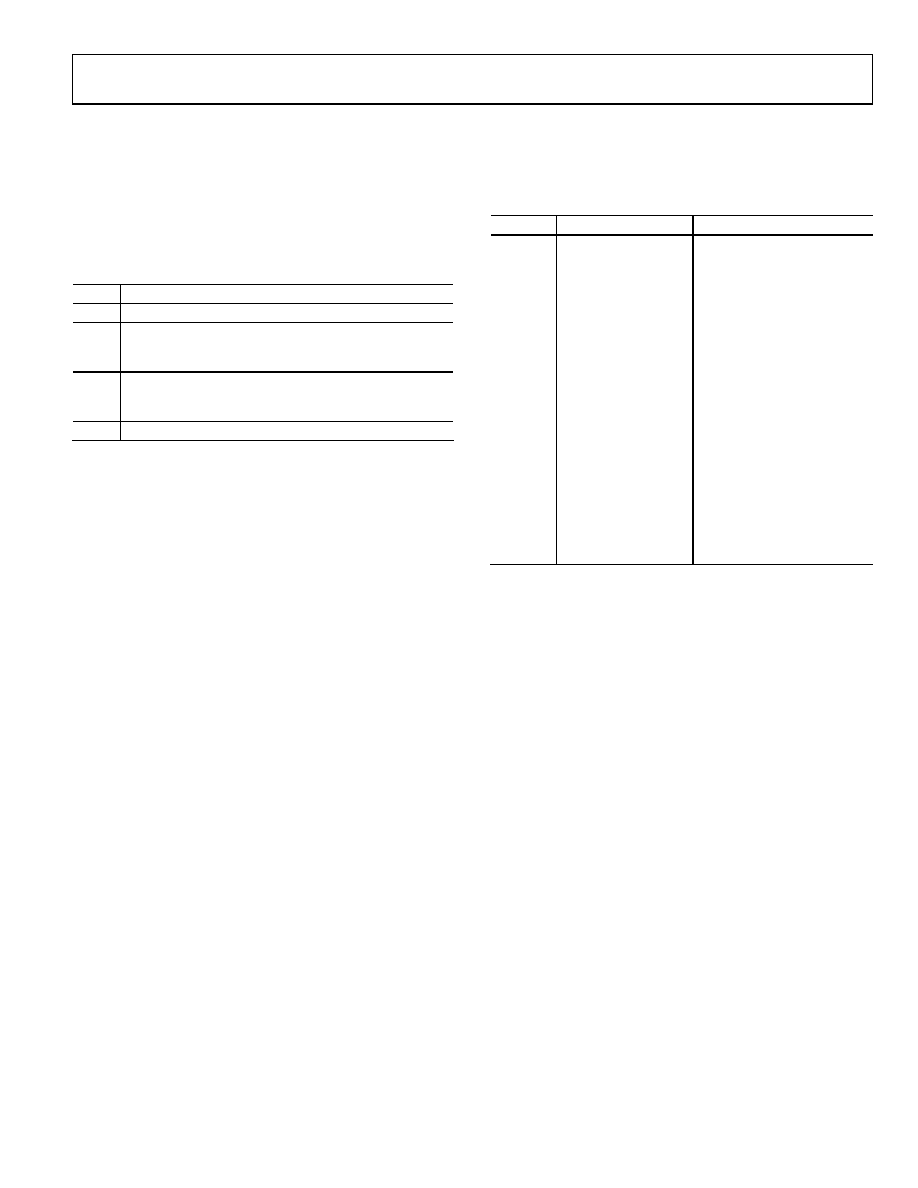

Table 106. SWICFG MMR Bit Designations

Bit

Description

31:3

Reserved.

2

Programmed Interrupt (FIQ). Setting/clearing this bit

corresponds to setting/clearing Bit 1 of FIQSTA and

FIQSIG.

1

Programmed Interrupt (IRQ). Setting/clearing this bit

corresponds to setting/clearing Bit 1 of IRQSTA and

IRQSIG.

0

Reserved.

Note that any interrupt signal must be active for at least the

equivalent of the interrupt latency time, to be detected by the

interrupt controller and to be detected by the user in the

IRQSTA/FIQSTA register.

TIMERS

The ADuC7128/ADuC7129 have five general purpose

timers/counters.

Timer0

Timer1

Timer2 or wake-up timer

Timer3 or watchdog timer

Timer4

The five timers in their normal mode of operation can be either

free-running or periodic.

In free-running mode, the counter decrements or increments

from the maximum or minimum value until zero scale or full

scale and starts again at the maximum or minimum value.

In periodic mode, the counter decrements/increments from the

value in the load register (TxLD MMR) until zero scale or full

scale and starts again at the value stored in the load register.

The value of a counter can be read at any time by accessing its

value register (TxVAL). Timers are started by writing in the

control register of the corresponding timer (TxCON).

In normal mode, an IRQ is generated each time the value of the

counter reaches zero, if counting down; or full scale, if counting

up. An IRQ can be cleared by writing any value to clear the register

of the particular timer (TxICLR).

Table 107. Event Selection Numbers

ES

Interrupt Number

Name

00000

2

RTOS Timer (Timer0)

00001

3

GP Timer0 (Timer1)

00010

4

Wake-Up Timer (Timer2)

00011

5

Watchdog Timer (Timer3)

00100

6

GP Timer1 (Timer4)

00101

7

Flash Control 0

00110

8

Flash Control 1

00111

9

ADC Channel

01000

10

Quadrature Encoder

01001

11

I2C Slave0

01010

12

I2C Slave1

01011

13

I2C Master0

01100

14

I2C Master1

01101

15

SPI Slave

01110

16

SPI Master

01111

17

UART0

10000

18

UART1

10001

19

External IRQ0

TIMER0—LIFETIME TIMER

Timer0 is a general-purpose, 48-bit count up, or a 16-bit count

up/down timer with a programmable prescaler. Timer0 is

clocked from the core clock, with a prescaler of 1, 16, 256, or

32,768. This gives a minimum resolution of 22 ns when the core

is operating at 41.78 MHz and with a prescaler of 1.

In 48-bit mode, Timer0 counts up from zero. The current

counter value can be read from T0VAL0 and T0VAL1.

In 16-bit mode, Timer0 can count up or count down. A 16-bit

value can be written to T0LD, which is loaded into the counter.

The current counter value can be read from T0VAL0. Timer0 has

a capture register (T0CAP) that can be triggered by a selected IRQ

source initial assertion. Once triggered, the current timer value is

copied to T0CAP, and the timer keeps running. This feature can be

used to determine the assertion of an event with more accuracy

than by servicing an interrupt alone.

Timer0 reloads the value from T0LD either when TIMER0

overflows or immediately when T0ICLR is written.

相关PDF资料 |

PDF描述 |

|---|---|

| D38999/20FC8SC | CONN RCPT 8POS WALL MNT W/SCKT |

| D38999/26WC8PB | CONN PLUG 8POS STRAIGHT W/PINS |

| MS27473E18A11P | CONN PLUG 11POS STRAIGHT W/PINS |

| AT32UC3C2512C-Z2ZR | IC MCU AVR32 512K FLASH 64QFN |

| MS27484E10B98P | CONN PLUG 6POS STRAIGHT W/PINS |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADUC7129BSTZ126-RL2 | 制造商:AD 制造商全称:Analog Devices 功能描述:Precision Analog Microcontroller ARM7TDMI MCU with 12-Bit ADC and DDS DAC |

| aduc7229bcpz126 | 制造商:Analog Devices 功能描述: |

| ADUC7229BCPZ126-RL | 制造商:Analog Devices 功能描述: |

| ADUC812 | 制造商:AD 制造商全称:Analog Devices 功能描述:MicroConverter⑩, Multichannel 12-Bit ADC with Embedded FLASH MCU |

| ADUC812_03 | 制造商:AD 制造商全称:Analog Devices 功能描述:MicroConverter㈢, Multichannel 12-Bit ADC with Embedded Flash MCU |

发布紧急采购,3分钟左右您将得到回复。