参数资料

| 型号: | DS2154LNA2+ |

| 厂商: | Maxim Integrated Products |

| 文件页数: | 121/124页 |

| 文件大小: | 0K |

| 描述: | IC TXRX E1 5V 100-LQFP |

| 产品培训模块: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 标准包装: | 90 |

| 类型: | 收发器 |

| 驱动器/接收器数: | 1/1 |

| 规程: | E1 |

| 电源电压: | 4.75 V ~ 5.25 V |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 100-LQFP |

| 供应商设备封装: | 100-LQFP(14x14) |

| 包装: | 托盘 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页当前第121页第122页第123页第124页

DS21354/DS21554 3.3V/5V E1 Single-Chip Transceivers

96 of 124

rising edge of JTCLK following entry into the Capture-DR state. Shift-DR can be used to shift the

identification code out serially via JTDO. During Test-Logic-Reset, the identification code is forced into

the instruction register’s parallel output. The ID code will always have a one in the LSB position. The

next 11 bits identify the manufacturer’s JEDEC number and number of continuation bytes followed by 16

bits for the device and 4 bits for the version. See Table 16-2. Table 16-3 lists the device ID codes for the

SCT devices.

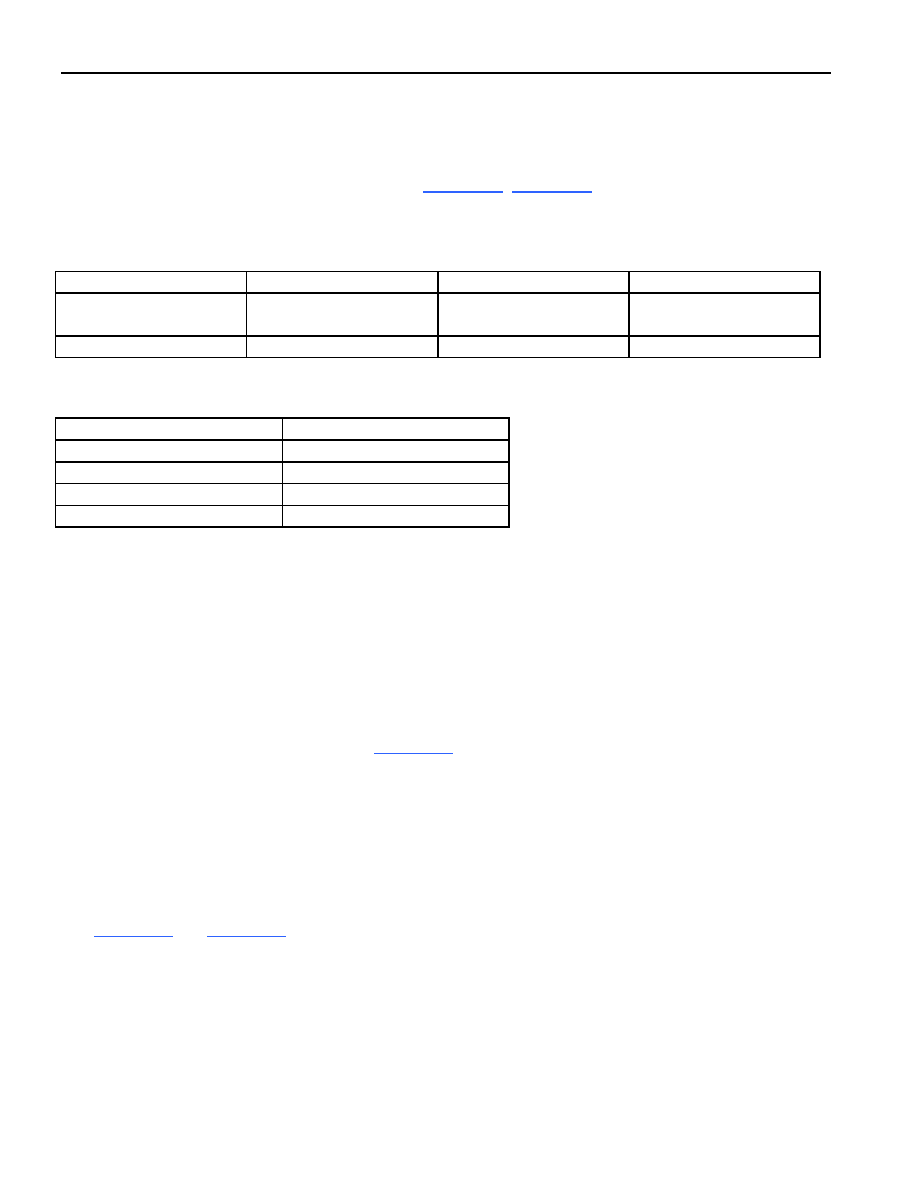

Table 16-2. ID Code Structure

MSB

LSB

Version

Contact Factory

Device ID

JEDEC

1

4 bits

16 bits

00010100001

1

Table 16-3. Device ID Codes

DEVICE

16-BIT ID

DS21354

0005h

DS21554

0003h

DS21352

0004h

DS21552

0002h

16.2.

Test Registers

IEEE 1149.1 requires a minimum of two test registers; the bypass register and the boundary scan register.

An optional test register has been included with the DS21354/554 design. This test register is the

identification register and is used in conjunction with the IDCODE instruction and the Test-Logic-Reset

state of the TAP controller.

Boundary Scan Register

This register contains both a shift register path and a latched parallel output for all control cells and

digital I/O cells and is n bits in length. See Table 16-4 for all the cell bit locations and definitions.

Bypass Register

This is a single one-bit shift register used in conjunction with the BYPASS, CLAMP, and HIGHZ

instructions that provides a short path between JTDI and JTDO.

Identification Register

The identification register contains a 32-bit shift register and a 32-bit latched parallel output. This register

is selected during the IDCODE instruction and when the TAP controller is in the Test-Logic-Reset state.

See Table 16-3 and Table 16-4 for more information on bit usage.

相关PDF资料 |

PDF描述 |

|---|---|

| DS2154L | IC TXRX E1 1CHIP 5V ENH 100-LQFP |

| DS2155LN | IC TXRX T1/E1/J1 1-CHIP 100-LQFP |

| DS2156LN+ | IC TXRX T1/E1/J1 1-CHIP 100-LQFP |

| DS2172T/T&R | IC TESTER BIT ERROR RATE 32-TQFP |

| DS2174QN+ | IC BERT ENHANCED 44-PLCC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| DS2154LNA2+ | 功能描述:网络控制器与处理器 IC Enhanced E1 Transceiver RoHS:否 制造商:Micrel 产品:Controller Area Network (CAN) 收发器数量: 数据速率: 电源电流(最大值):595 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:PBGA-400 封装:Tray |

| DS2154LND2 | 功能描述:网络控制器与处理器 IC RoHS:否 制造商:Micrel 产品:Controller Area Network (CAN) 收发器数量: 数据速率: 电源电流(最大值):595 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:PBGA-400 封装:Tray |

| DS2154LND2+ | 制造商:Maxim Integrated Products 功能描述:ENHANCED E1 SCT LQFP REVD2 IND LF - Rail/Tube |

| DS2155 | 制造商:DALLAS 制造商全称:Dallas Semiconductor 功能描述:T1/E1/J1 Single-Chip Transceiver TDM/UTOPIA II Interface |

| DS2155_06 | 制造商:DALLAS 制造商全称:Dallas Semiconductor 功能描述:T1/E1/J1 Single-Chip Transceiver |

发布紧急采购,3分钟左右您将得到回复。