- 您现在的位置:买卖IC网 > PDF目录97869 > DS3131 (MAXIM INTEGRATED PRODUCTS INC) SPECIALTY TELECOM CIRCUIT, PBGA256 PDF资料下载

参数资料

| 型号: | DS3131 |

| 厂商: | MAXIM INTEGRATED PRODUCTS INC |

| 元件分类: | Telecom IC:Other |

| 英文描述: | SPECIALTY TELECOM CIRCUIT, PBGA256 |

| 封装: | 27 X 27 MM, PLASTIC, BGA-256 |

| 文件页数: | 155/174页 |

| 文件大小: | 1261K |

| 代理商: | DS3131 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页第137页第138页第139页第140页第141页第142页第143页第144页第145页第146页第147页第148页第149页第150页第151页第152页第153页第154页当前第155页第156页第157页第158页第159页第160页第161页第162页第163页第164页第165页第166页第167页第168页第169页第170页第171页第172页第173页第174页

DS3131

81 of 174

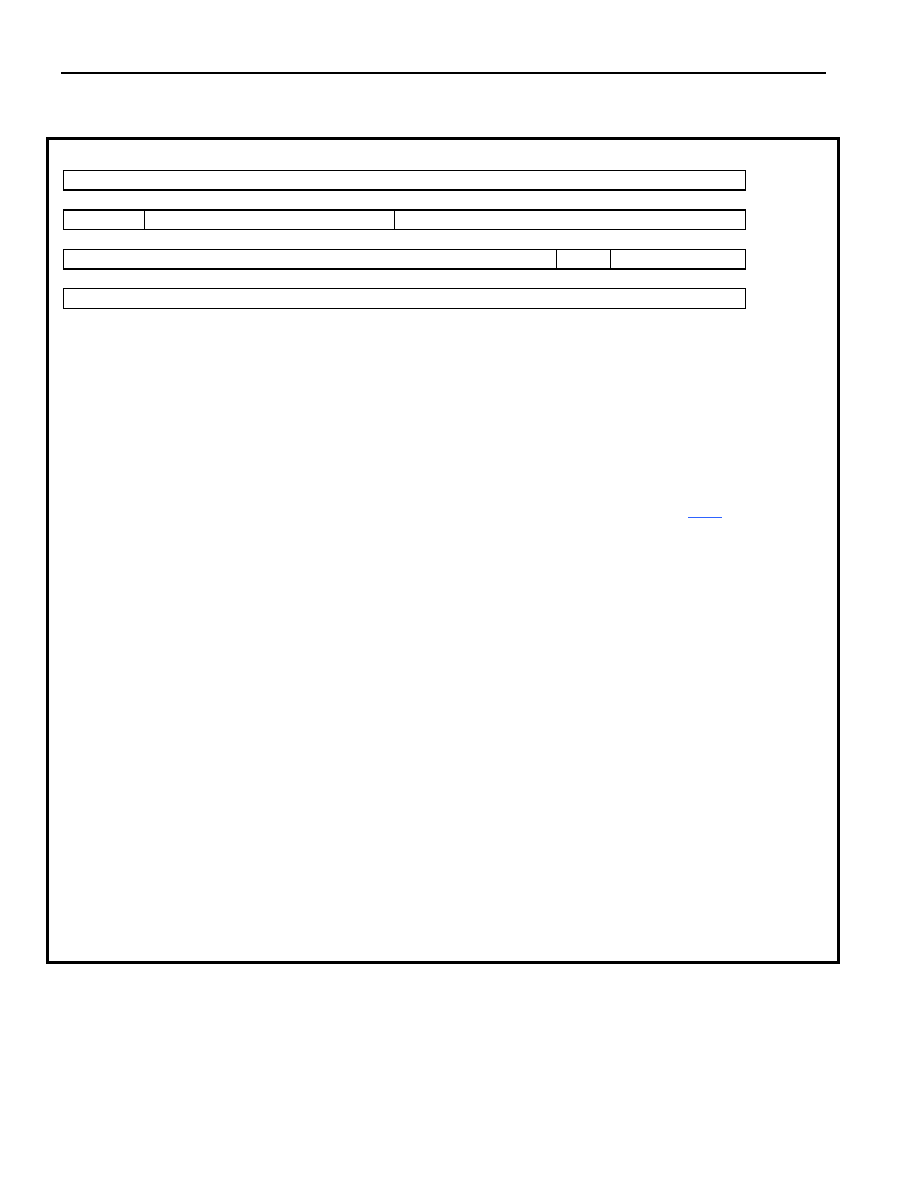

Figure 9-4. Receive Packet Descriptors

dword 0

Data Buffer Address (32)

dword 1

BUFS (3)

Byte Count (13)

Next Descriptor Pointer (16)

dword 2

Timestamp (24)

00b

HDLC CH#(6)

dword 3

unused (32)

Note: T

he organization of the receive descriptor is not affected by the enabling of Big Endian.

dword 0; Bits 0 to 31/Data Buffer Address. Direct 32-bit starting address of the data buffer that is associated

with this receives descriptor.

dword 1; Bits 0 to 15/Next Descriptor Pointer. This 16-bit value is the offset from the receive descriptor base

address of the next descriptor in the chain. Only valid if buffer status = 001 or 010.

dword 1; Bits 16 to 28/Byte Count. Number of bytes stored in the data buffer. Maximum is 8191 Bytes (0000h =

0 Bytes / 1FFFh = 8191 Bytes). This byte count does not include the buffer offset. The host determines the buffer

offset (if any) through the buffer offset field in the receive DMA configuration RAM (Section 9.2.5).

dword 1; Bits 29 to 31/Buffer Status. Must be one of the three states listed below.

001 = first buffer of a multiple buffer packet

010 = middle buffer of a multiple buffer packet

100 = last buffer of a multiple or single buffer packet (equivalent to EOF)

dword 2; Bits 0 to 5/HDLC Channel Number. HDLC channel number, which can be from 1 to 40.

000000 (00h) = HDLC channel number 1

100111 (27h) = HDLC channel number 40

dword 2; Bits 6, 7/Unused. Set to 00b by the DMA.

dword 2; Bits 8 to 31/Timestamp. When each descriptor is written into memory by the DMA, this 24-bit

timestamp is provided to keep track of packet arrival times. The timestamp is based on the PCLK frequency

divided by 16. For a 33MHz PCLK, the timestamp increments every 485ns and rolls over every 8.13s. The host

can calculate the difference in packets’ arrival times by knowing the PCLK frequency and then taking the

difference in timestamp readings between consecutive packet descriptors.

dword 3; Bits 0 to 31/Unused. Not written to by the DMA. Can be used by the host. Application Note: dword 3

is used by the transmit DMA and, in store and forward applications, the receive and transmit packet descriptors

have been designed to eliminate the need for the host to groom the descriptors before transmission. In these type of

applications, the host should not use dword 3 of the receive packet descriptor.

相关PDF资料 |

PDF描述 |

|---|---|

| DS3134 | DATACOM, FRAMER, PBGA256 |

| DS3150QN | DATACOM, PCM TRANSCEIVER, PQCC28 |

| DS3150Q | DATACOM, PCM TRANSCEIVER, PQCC28 |

| DS3150TN | DATACOM, PCM TRANSCEIVER, PDIP48 |

| DS3150T | DATACOM, PCM TRANSCEIVER, PQFP48 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| DS3131DK | 功能描述:通信集成电路 - 若干 RoHS:否 制造商:Maxim Integrated 类型:Transport Devices 封装 / 箱体:TECSBGA-256 数据速率:100 Mbps 电源电压-最大:1.89 V, 3.465 V 电源电压-最小:1.71 V, 3.135 V 电源电流:50 mA, 225 mA 最大工作温度:+ 85 C 最小工作温度:- 40 C 封装:Tube |

| DS3134 | 功能描述:IC CTRLR HDLC CHATEAU 256-BGA RoHS:否 类别:集成电路 (IC) >> 接口 - 控制器 系列:- 标准包装:4,900 系列:- 控制器类型:USB 2.0 控制器 接口:串行 电源电压:3 V ~ 3.6 V 电流 - 电源:135mA 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:36-VFQFN 裸露焊盘 供应商设备封装:36-QFN(6x6) 包装:* 其它名称:Q6396337A |

| DS-313PIN | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Analog Miscellaneous |

| DS-313-PIN | 功能描述:信号调节 RoHS:否 制造商:EPCOS 产品:Duplexers 频率:782 MHz, 751 MHz 频率范围: 电压额定值: 带宽: 阻抗:50 Ohms 端接类型:SMD/SMT 封装 / 箱体:2.5 mm x 2 mm 工作温度范围:- 30 C to + 85 C 封装:Reel |

| DS31400 | 制造商:MAXIM 制造商全称:Maxim Integrated Products 功能描述:8-Input, 14-Output, Dual DPLL Timing IC with Sub-ps Output Jitter |

发布紧急采购,3分钟左右您将得到回复。