- 您现在的位置:买卖IC网 > PDF目录295888 > EPM2210GF256A5N (ALTERA CORP) FLASH PLD, PBGA256 PDF资料下载

参数资料

| 型号: | EPM2210GF256A5N |

| 厂商: | ALTERA CORP |

| 元件分类: | PLD |

| 英文描述: | FLASH PLD, PBGA256 |

| 封装: | 17 X 17 MM, 1 MM PITCH, LEAD FREE, FBGA-256 |

| 文件页数: | 48/108页 |

| 文件大小: | 1342K |

| 代理商: | EPM2210GF256A5N |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页当前第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页

2–36Core Version a.b.c variable

Altera Corporation

MAX II Device Handbook, Volume 1

March 2008

I/O Structure

PCI Compliance

The MAX II EPM1270 and EPM2210 devices are compliant with PCI

applications as well as all 3.3-V electrical specifications in the PCI Local

Bus Specification Revision 2.2. These devices are also large enough to

support PCI intellectual property (IP) cores. Table 2–5 shows the MAX II

device speed grades that meet the PCI timing specifications.

Schmitt Trigger

The input buffer for each MAX II device I/O pin has an optional Schmitt

trigger setting for the 3.3-V and 2.5-V standards. The Schmitt trigger

allows input buffers to respond to slow input edge rates with a fast

output edge rate. Most importantly, Schmitt triggers provide hysteresis

on the input buffer, preventing slow-rising noisy input signals from

ringing or oscillating on the input signal driven into the logic array. This

provides system noise tolerance on MAX II inputs, but adds a small,

nominal input delay.

The JTAG input pins (TMS, TCK, and TDI) have Schmitt trigger buffers

that are always enabled.

1

The

TCK input is susceptible to high pulse glitches when the

input signal fall time is greater than 200 ns for all I/O standards.

Output Enable Signals

Each MAX II IOE output buffer supports output enable signals for

tri-state control. The output enable signal can originate from the

GCLK[3..0]

global signals or from the MultiTrack interconnect. The

MultiTrack interconnect routes output enable signals and allows for a

unique output enable for each output or bidirectional pin.

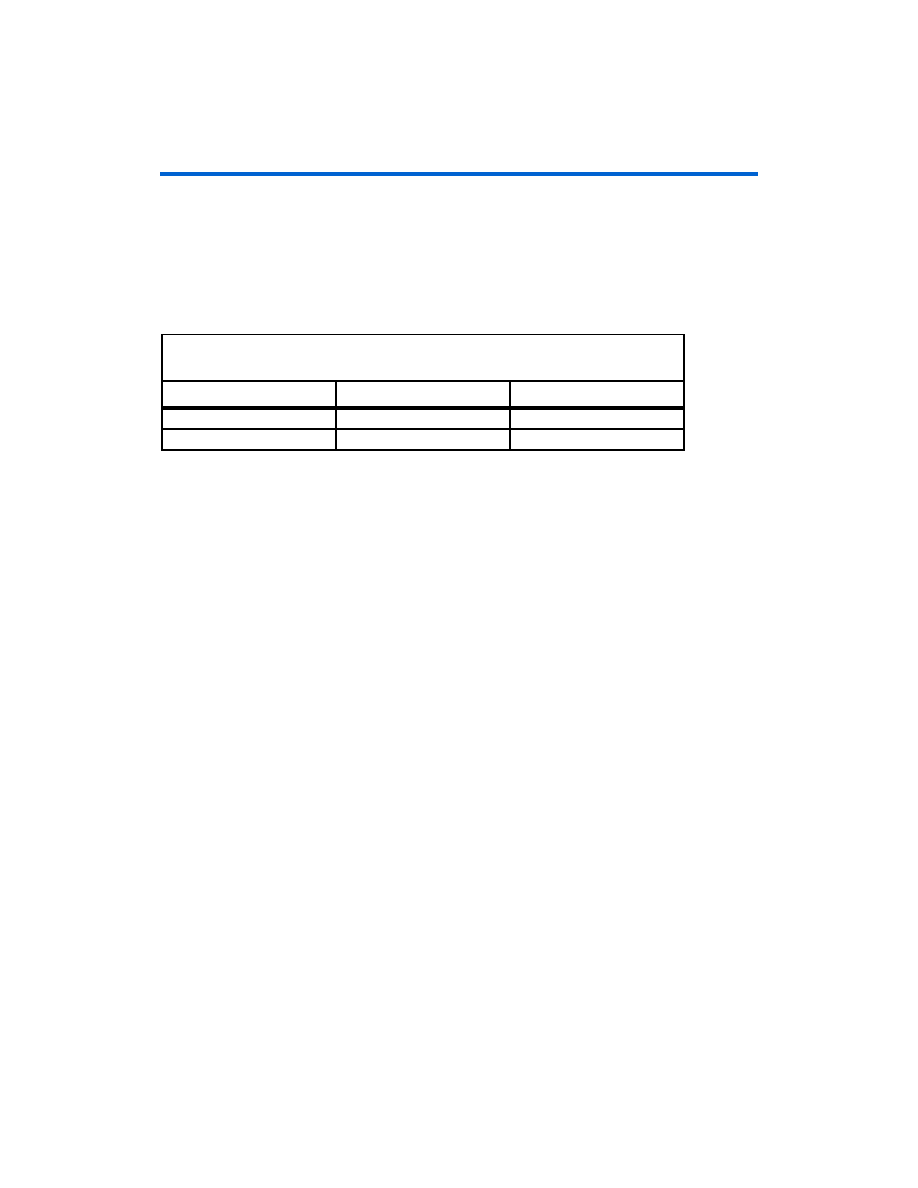

Table 2–5. MAX II Devices and Speed Grades that Support 3.3-V PCI Electrical Specifications

and Meet PCI Timing

Device

33-MHz PCI

66-MHz PCI

EPM1270

All Speed Grades

–3 Speed Grade

EPM2210

All Speed Grades

–3 Speed Grade

相关PDF资料 |

PDF描述 |

|---|---|

| EPM2210GF324A3N | FLASH PLD, PBGA324 |

| EPM2210GF324A4N | FLASH PLD, PBGA324 |

| EPM2210GF324A5N | FLASH PLD, PBGA324 |

| EPM7064BFC100-3 | EE PLD, 3.5 ns, PBGA100 |

| EPM7064BFC100-5 | EE PLD, 3.5 ns, PBGA100 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| EPM2210GF256C3 | 功能描述:CPLD - 复杂可编程逻辑器件 CPLD - MAX II 1700 Macro 204 IO RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100 |

| EPM2210GF256C3N | 功能描述:CPLD - 复杂可编程逻辑器件 CPLD - MAX II 1700 Macro 204 IO RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100 |

| EPM2210GF256C4 | 功能描述:CPLD - 复杂可编程逻辑器件 CPLD - MAX II 1700 Macro 204 IO RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100 |

| EPM2210GF256C4N | 功能描述:CPLD - 复杂可编程逻辑器件 CPLD - MAX II 1700 Macro 204 IO RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100 |

| EPM2210GF256C5 | 功能描述:CPLD - 复杂可编程逻辑器件 CPLD - MAX II 1700 Macro 204 IO RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100 |

发布紧急采购,3分钟左右您将得到回复。