- 您现在的位置:买卖IC网 > PDF目录1996 > HMC703LP4E (Hittite Microwave Corporation)IC FRACT-N PLL W/SWEEPR 24QFN PDF资料下载

参数资料

| 型号: | HMC703LP4E |

| 厂商: | Hittite Microwave Corporation |

| 文件页数: | 38/58页 |

| 文件大小: | 0K |

| 描述: | IC FRACT-N PLL W/SWEEPR 24QFN |

| 标准包装: | 1 |

| 类型: | 整数 N/小数 N 分频 |

| PLL: | 是 |

| 输入: | CMOS |

| 输出: | CMOS |

| 电路数: | 1 |

| 比率 - 输入:输出: | 1:1 |

| 差分 - 输入:输出: | 是/无 |

| 频率 - 最大: | 8GHz |

| 除法器/乘法器: | 是/无 |

| 电源电压: | 3.3V,5V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 24-VQFN 裸露焊盘 |

| 供应商设备封装: | 24-QFN 裸露焊盘(4x4) |

| 包装: | 标准包装 |

| 其它名称: | 1127-1065-6 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页当前第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页

P

LL

s

-

s

M

T

6 - 43

HMC703LP4E

v02.0813

8 GHz fractional syntHesizer

For price, delivery and to place orders: Hittite Microwave Corporation, 2 Elizabeth Drive, Chelmsford, MA 01824

978-250-3343 978-250-3373 fax Order On-line at www.hittite.com

Application Support: pll@hittite.com

cific address, it is necessary in the first sPI cycle to write the desired address to Reg 00h[4:0], then in the next sPI cycle

the desired data will be available on LD_sDO.

An example of the Open Mode two cycle procedure to read from any random address is as follows:

a. The Master (host), on the first 24 falling edges of sCK places 24 bit data, d23:d0, MsB first, on sDI

as shown in Figure 44. d23:d5 should be set to zero. d4:d0 = address of the register to be READ on

the next cycle.

b. the slave (synthesizer) shifts in data on sDI on the first 24 rising edges of sCK

c. Master places 5 bit register address , r4:r0, ( the address the WRITE ADDREss register), MsB first,

on the next 5 falling edges of sCK (25-29). r4:r0=00000.

d. slave shifts the register bits on the next 5 rising edges of sCK (25-29).

e. Master places 3 bit chip address, a2:a0, MsB first, on the next 3 falling edges of sCK (30-32).The

HMC703LP4E chip address is fixed at 000.

f.

slave shifts the chip address bits on the next 3 rising edges of sCK (30-32).

g. Master asserts sEN after the 32nd rising edge of sCK.

h. slave registers the sDI data on the rising edge of sEN.

i.

Master clears sEN to complete the address transfer of the two part READ cycle.

j.

If we do not wish to write data to the chip at the same time as we do the second cycle , then it is

recommended to simply rewrite the same contents on sDI to Register zero on the READ back part

of the cycle.

k. Master places the same sDI data as the previous cycle on the next 32 falling edges of sCK.

l.

slave (synthesizer) shifts the sDI data on the next 32 rising edges of sCK.

m. slave places the desired data (i.e. data from address in Reg 00h[4:0 ]) on LD_sDO on the next 32

rising edges of sCK. Lock Detect is disabled.

n. Master asserts sEN after the 32nd rising edge of sCK to complete the cycle and revert back to Lock

Detect on LD_sDO.

Note that if the chip address bits are unrecognized (a2:a0), the slave will tri-state the LD_sDO output to prevent a pos-

sible bus contention issue.

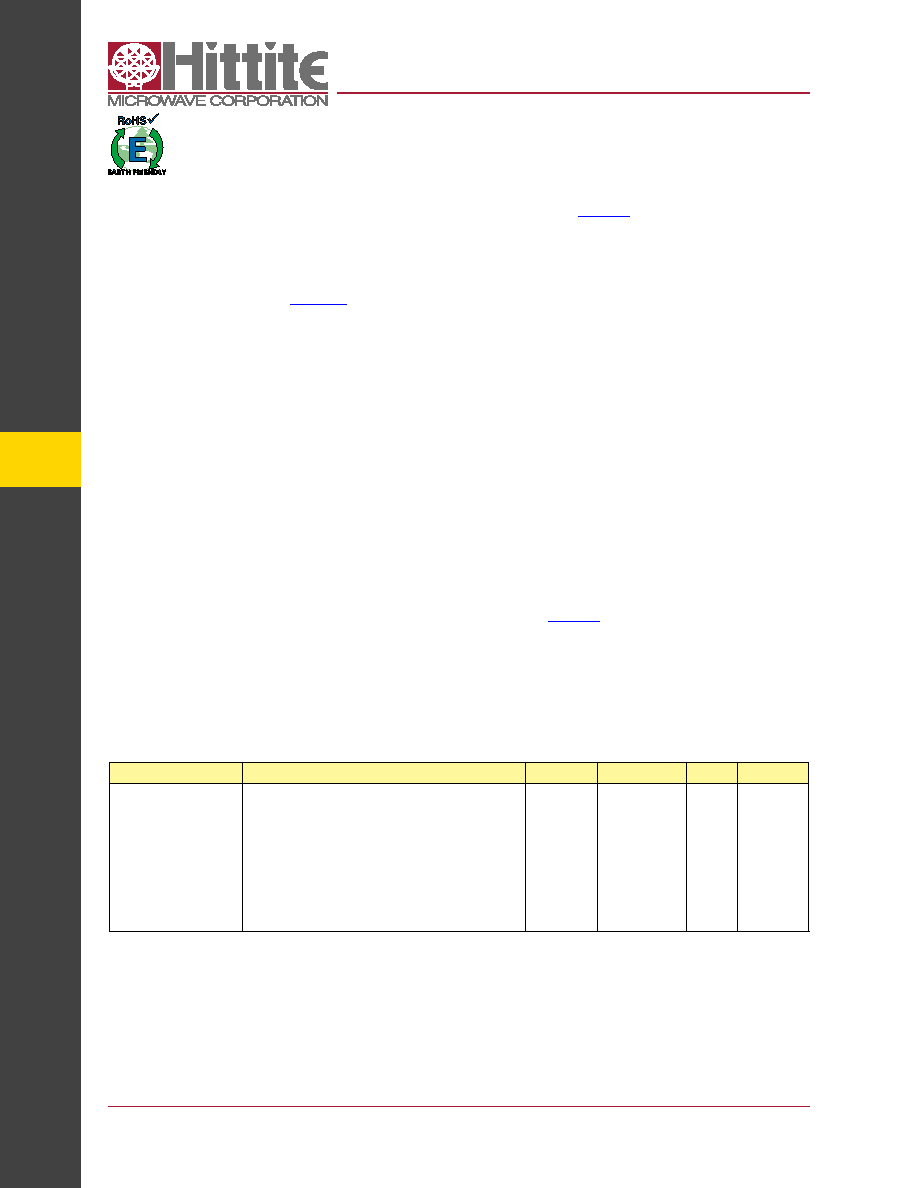

table 12. sPi open Mode - read timing characteristics

Parameter

Conditions

Min.

Typ.

Max.

Units

t1

t2

t3

t4

t5

t6

t7

sDI setup time

sDI hold time

sEN low duration

sEN high duration

sCK Rising Edge to sDO time

sEN to sCK Recovery Time

sCK 32 Rising Edge to sEN Rising Edge

3

10

8.2+0.2ns/pF

ns

相关PDF资料 |

PDF描述 |

|---|---|

| HMC704LP4E | IC FRACT-N PLL 16BIT 24QFN |

| HMC830LP6GE | IC FRACT-N PLL W/VCO 40QFN |

| HMP8117CNZ | IC VIDEO DECODER NTSC/PAL 80PQFP |

| HMP8156ACNZ | IC VIDEO ENCODER NTSC/PAL 64MQFP |

| HSP45102SC-40Z | IC OSC NCO 40MHZ 28-SOIC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| HMC703LP4ETR | 制造商:Hittite Microwave Corp 功能描述:IC FRACT-N PLL W/SWEEPR 24QFN 制造商:Hittite Microwave Corp 功能描述:8 GHz Fractional-N PLL with Sweeper |

| HMC7043LP7FE | 功能描述:IC FRACT-N PLL W/SWEEPR 48LFCSP 制造商:analog devices inc. 系列:- 包装:剪切带(CT) 零件状态:新产品 类型:* PLL:是 输入:时钟 输出:CML,LVDS,LVPECL 电路数:1 比率 - 输入:输出:1:14 差分 - 输入:输出:是/是 频率 - 最大值:3.2GHz 分频器/倍频器:是/无 电压 - 电源:3.135 V ~ 3.465 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:48-VFQFN 裸露焊盘,CSP 供应商器件封装:48-LFCSP(7x7) 标准包装:1 |

| HMC7043LP7FETR | 功能描述:IC FRACT-N PLL W/SWEEPR 48LFCSP 制造商:analog devices inc. 系列:- 包装:剪切带(CT) 零件状态:在售 类型:时钟缓冲器 PLL:是 输入:时钟 输出:CMOS,LVDS,LVPECL 电路数:1 比率 - 输入:输出:1:14 差分 - 输入:输出:是/是 频率 - 最大值:3.2GHz 分频器/倍频器:是/无 电压 - 电源:3.135 V ~ 3.465 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:48-VFQFN 裸露焊盘,CSP 供应商器件封装:48-LFCSP(7x7) 标准包装:1 |

| HMC7044LP10BETR | 功能描述:IC JITTER ATTENUATOR 68LFCSP 制造商:analog devices inc. 系列:- 包装:剪切带(CT) 零件状态:在售 类型:漂移衰减器 PLL:是 输入:CML,CMOS,LVDS,LVPECL 输出:CML,LVDS,LVPECL 电路数:1 比率 - 输入:输出:4:14 差分 - 输入:输出:是/是 频率 - 最大值:3.2GHz 分频器/倍频器:是/无 电压 - 电源:3.135 V ~ 3.465 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:68-VFQFN 裸露焊盘,CSP 供应商器件封装:68-LFCSP-VQ(10x10) 标准包装:1 |

| HMC704LP4E | 功能描述:IC FRACT-N PLL 16BIT 24QFN RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:2,000 系列:- 类型:PLL 频率合成器 PLL:是 输入:晶体 输出:时钟 电路数:1 比率 - 输入:输出:1:1 差分 - 输入:输出:无/无 频率 - 最大:1GHz 除法器/乘法器:是/无 电源电压:4.5 V ~ 5.5 V 工作温度:-20°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-LSSOP(0.175",4.40mm 宽) 供应商设备封装:16-SSOP 包装:带卷 (TR) 其它名称:NJW1504V-TE1-NDNJW1504V-TE1TR |

发布紧急采购,3分钟左右您将得到回复。