- 您现在的位置:买卖IC网 > PDF目录299403 > LFXP15C-4FN256C (LATTICE SEMICONDUCTOR CORP) PDF资料下载

参数资料

| 型号: | LFXP15C-4FN256C |

| 厂商: | LATTICE SEMICONDUCTOR CORP |

| 元件分类: | FPGA |

| 中文描述: | FPGA, 1932 CLBS, PBGA256 |

| 封装: | 17 X 17 MM, LEAD FREE, FPBGA-256 |

| 文件页数: | 44/130页 |

| 文件大小: | 1312K |

| 代理商: | LFXP15C-4FN256C |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页当前第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页

2-17

Architecture

Lattice Semiconductor

LatticeXP Family Data Sheet

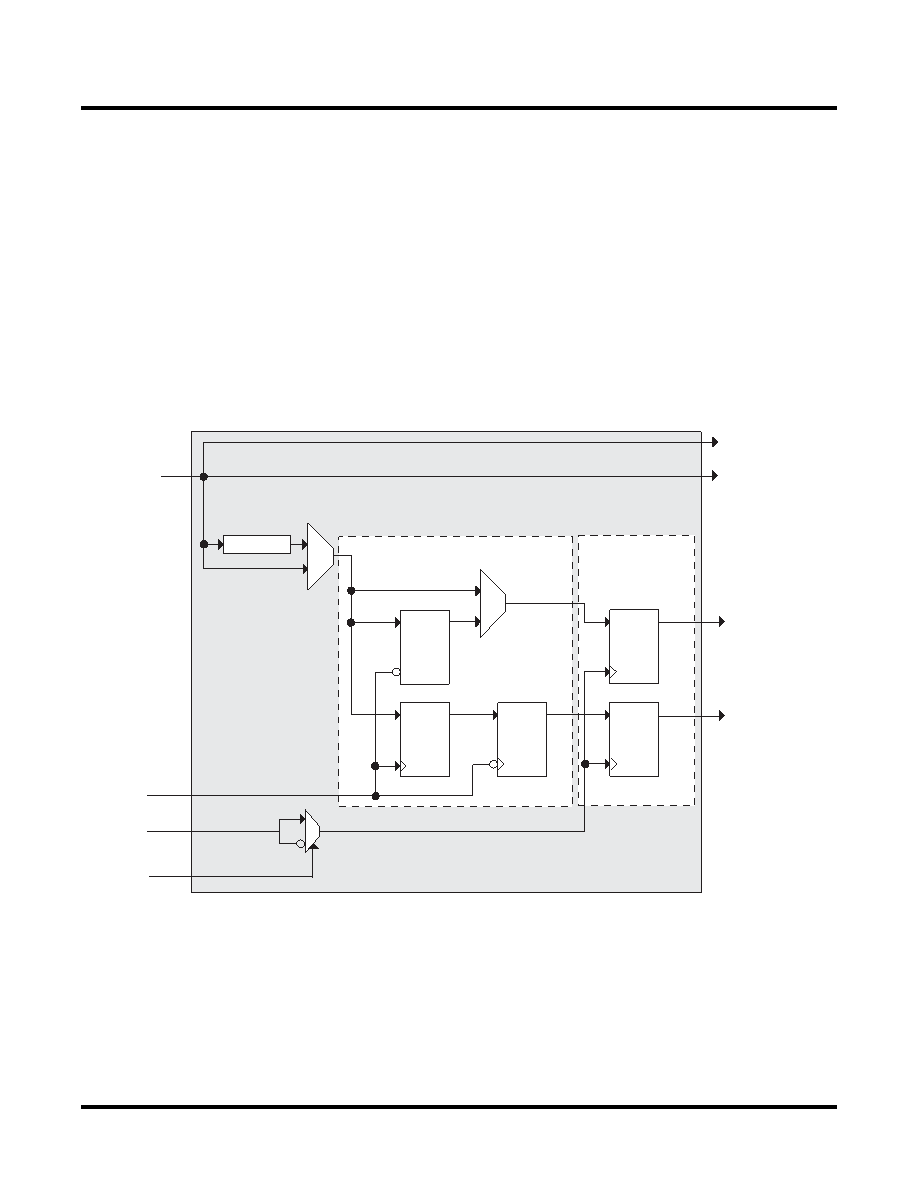

in selected blocks the input to the DQS delay block. If one of the bypass options is not chosen, the signal first

passes through an optional delay block. This delay, if selected, ensures no positive input-register hold-time require-

ment when using a global clock.

The input block allows two modes of operation. In the single data rate (SDR) the data is registered, by one of the

registers in the single data rate sync register block, with the system clock. In the DDR Mode two registers are used

to sample the data on the positive and negative edges of the DQS signal creating two data streams, D0 and D2.

These two data streams are synchronized with the system clock before entering the core. Further discussion on

this topic is in the DDR Memory section of this data sheet.

Figure 2-21 shows the input register waveforms for DDR operation and Figure 2-22 shows the design tool primi-

tives. The SDR/SYNC registers have reset and clock enable available.

The signal DDRCLKPOL controls the polarity of the clock used in the synchronization registers. It ensures ade-

quate timing when data is transferred from the DQS to the system clock domain. For further discussion of this topic,

see the DDR memory section of this data sheet.

Figure 2-20. Input Register Diagram

D

Q

D

Q

D

Q

D-Type

Fixed Delay

To Routing

DI

(From sysIO

Buffer)

DQS Delayed

(From DQS

Bus)

CLK0

(From Routing)

DDRCLKPOL

(From DDR Polarity

Control Bus)

INCK

INDD

Delay Block

DDR Registers

D-Type

D

Q

D

Q

D-Type

/LATCH

D-Type

IPOS0

IPOS1

SDR & Sync

Registers

D0

D2

D1

相关PDF资料 |

PDF描述 |

|---|---|

| LFZ3508VXX | GENERAL PURPOSE INDUCTOR |

| LFZ2805HXX | GENERAL PURPOSE INDUCTOR |

| LF02004VTX | GENERAL PURPOSE INDUCTOR |

| LG3341-NE7501 | T-1 SINGLE COLOR LED, GREEN, 3 mm |

| LG3341-KNE9117 | T-1 SINGLE COLOR LED, GREEN, 3 mm |

相关代理商/技术参数 |

参数描述 |

|---|---|

| LFXP15C-4FN256I | 功能描述:FPGA - 现场可编程门阵列 15.4K LUTs 188 IO 1. 8/2.5/3.3V-4 Spd I RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 栅极数量: 逻辑块数量:943 内嵌式块RAM - EBR:1956 kbit 输入/输出端数量:128 最大工作频率:800 MHz 工作电源电压:1.1 V 最大工作温度:+ 70 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-256 |

| LFXP15C-4FN388C | 功能描述:FPGA - 现场可编程门阵列 15.4K LUTs 268 IO 1. 8/2.5/3.3V -4 Spd RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 栅极数量: 逻辑块数量:943 内嵌式块RAM - EBR:1956 kbit 输入/输出端数量:128 最大工作频率:800 MHz 工作电源电压:1.1 V 最大工作温度:+ 70 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-256 |

| LFXP15C-4FN388I | 功能描述:FPGA - 现场可编程门阵列 15.4K LUTs 268 IO 1. 8/2.5/3.3V-4 Spd I RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 栅极数量: 逻辑块数量:943 内嵌式块RAM - EBR:1956 kbit 输入/输出端数量:128 最大工作频率:800 MHz 工作电源电压:1.1 V 最大工作温度:+ 70 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-256 |

| LFXP15C-4FN484C | 功能描述:FPGA - 现场可编程门阵列 15.4K LUTs 1.8/2.5/3 .3V -4 Spd RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 栅极数量: 逻辑块数量:943 内嵌式块RAM - EBR:1956 kbit 输入/输出端数量:128 最大工作频率:800 MHz 工作电源电压:1.1 V 最大工作温度:+ 70 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-256 |

| LFXP15C-4FN484I | 功能描述:FPGA - 现场可编程门阵列 15.4K LUTs 1.8/2.5/3 .3V-4 Spd I RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 栅极数量: 逻辑块数量:943 内嵌式块RAM - EBR:1956 kbit 输入/输出端数量:128 最大工作频率:800 MHz 工作电源电压:1.1 V 最大工作温度:+ 70 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-256 |

发布紧急采购,3分钟左右您将得到回复。